входного операнда и выходной информа- зо операнда - выходная информация с нации.

При сложении и вычитании входной информации устройство работает следующим образом.

Информация по входам первого и втрого операндов поступает на информационные входы сигнатурного регистра 10 и одновременно в блок 3 определения знака числа, который служит для определения знака результата сложения и вычитания. Если знаки операндов совпадают, то в сумматоре 6 прокопителя 1 через второй выходной регистр 8 и соответственно в случае сложения второго операнда с выходной информацией. Далее процесс происходит

аналогично режиму обработки входной информации.

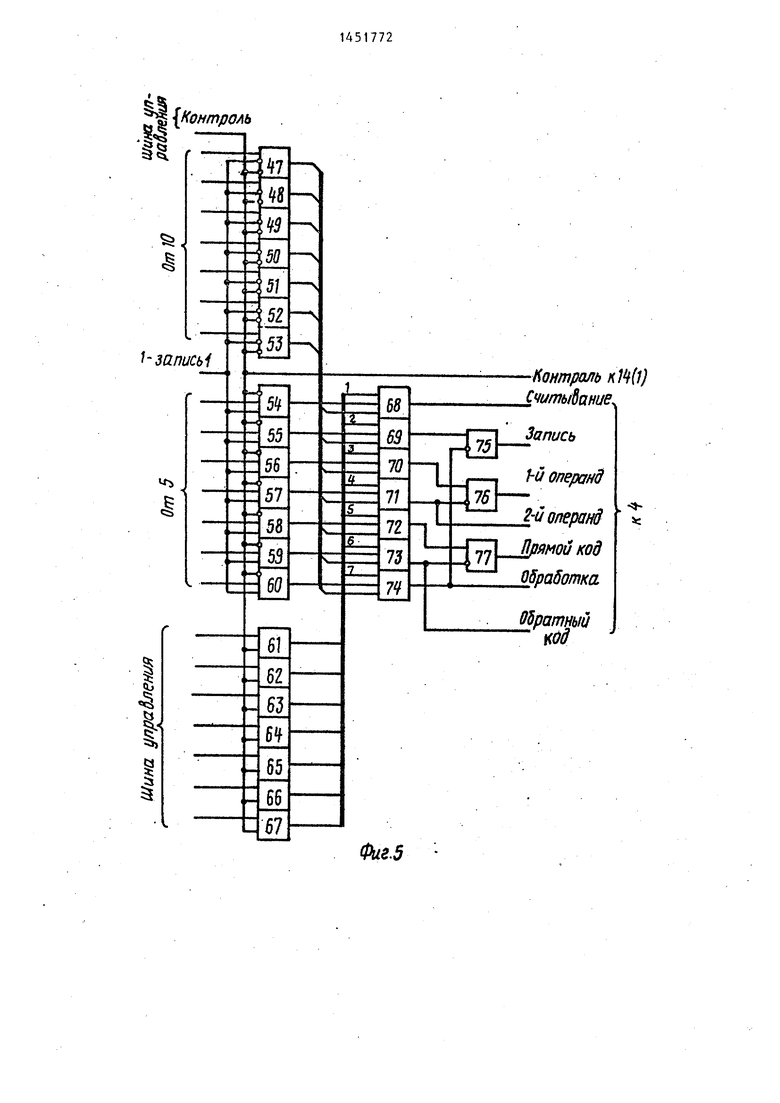

Режим тестового самодиагностирова- ния инициируется подачей сигнала Контроль на вход мультиплексора и

далее на блок 14. После этого инфорг мация на шинах управления перестает влиять на функционирование устройства. Блок 14 с помощью элемента 31 за

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых узлов | 1983 |

|

SU1124312A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1307459A1 |

| Микропрограммное устройство управления с самоконтролем | 1987 |

|

SU1427367A1 |

| Устройство для контроля цифровых блоков | 1987 |

|

SU1587515A1 |

| Устройство для деления | 1988 |

|

SU1621034A1 |

| Сигнатурный анализатор | 1984 |

|

SU1238075A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1539782A2 |

| Устройство для встроенного тестового контроля | 1984 |

|

SU1196877A1 |

| Арифметическое устройство | 1989 |

|

SU1647557A1 |

| Устройство для контроля полупроводниковой памяти | 1986 |

|

SU1432612A2 |

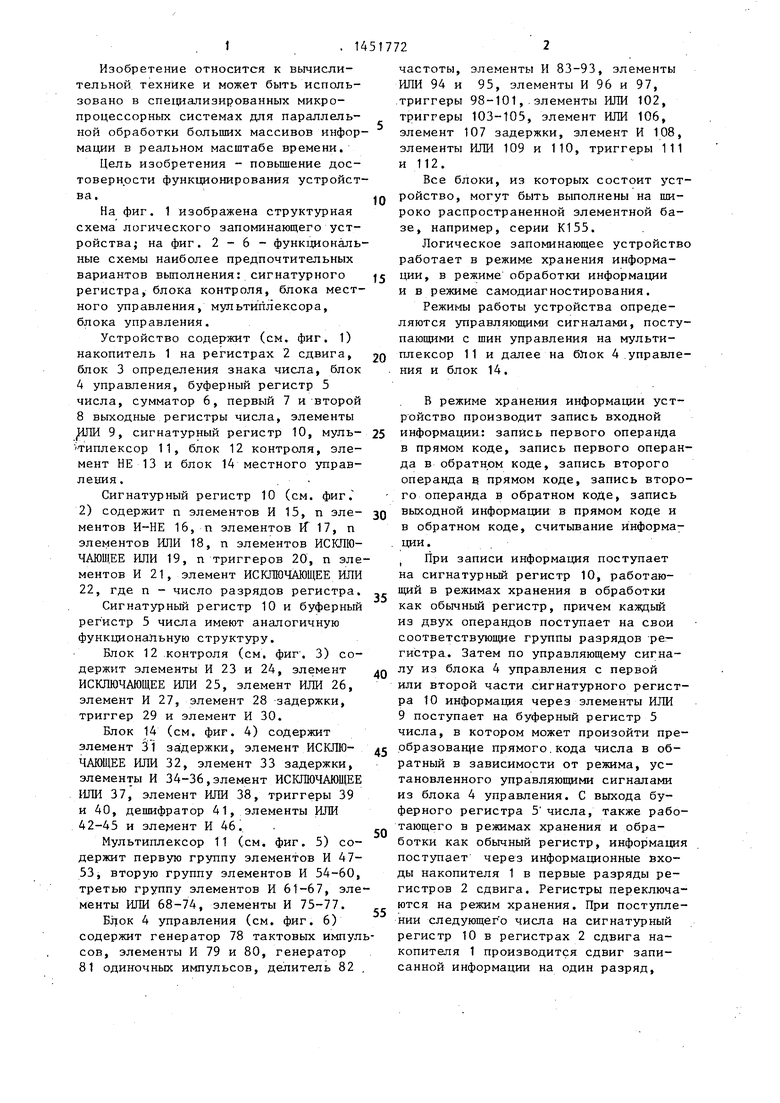

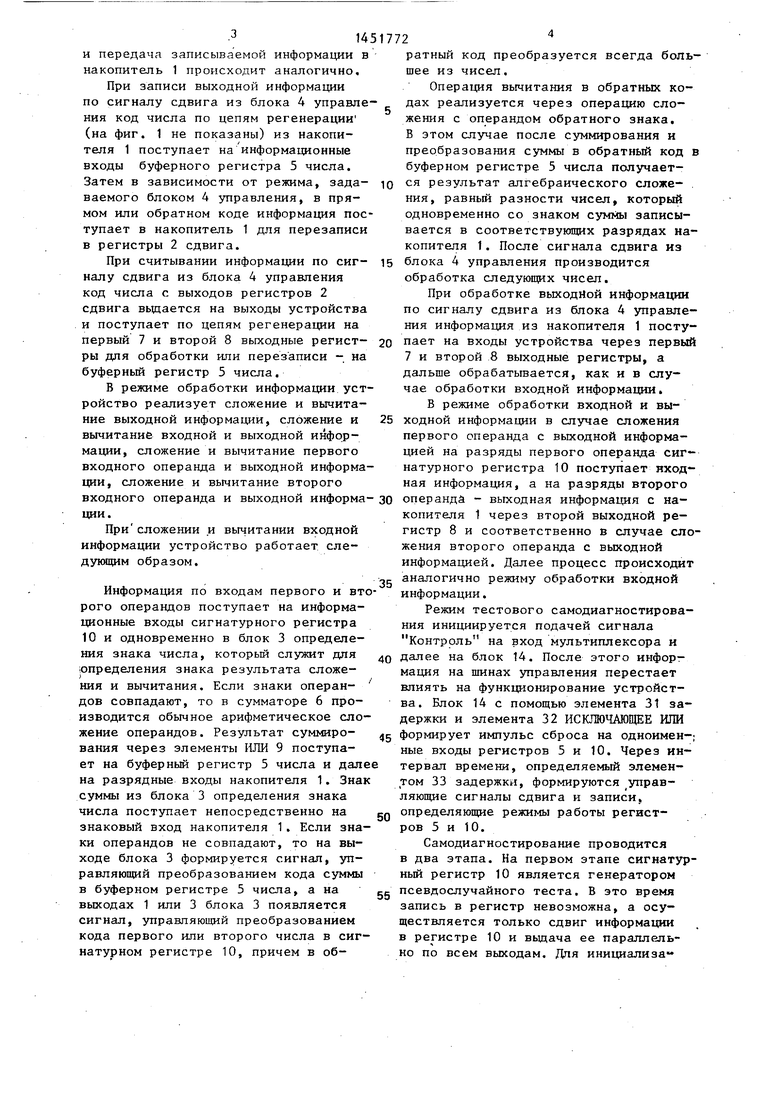

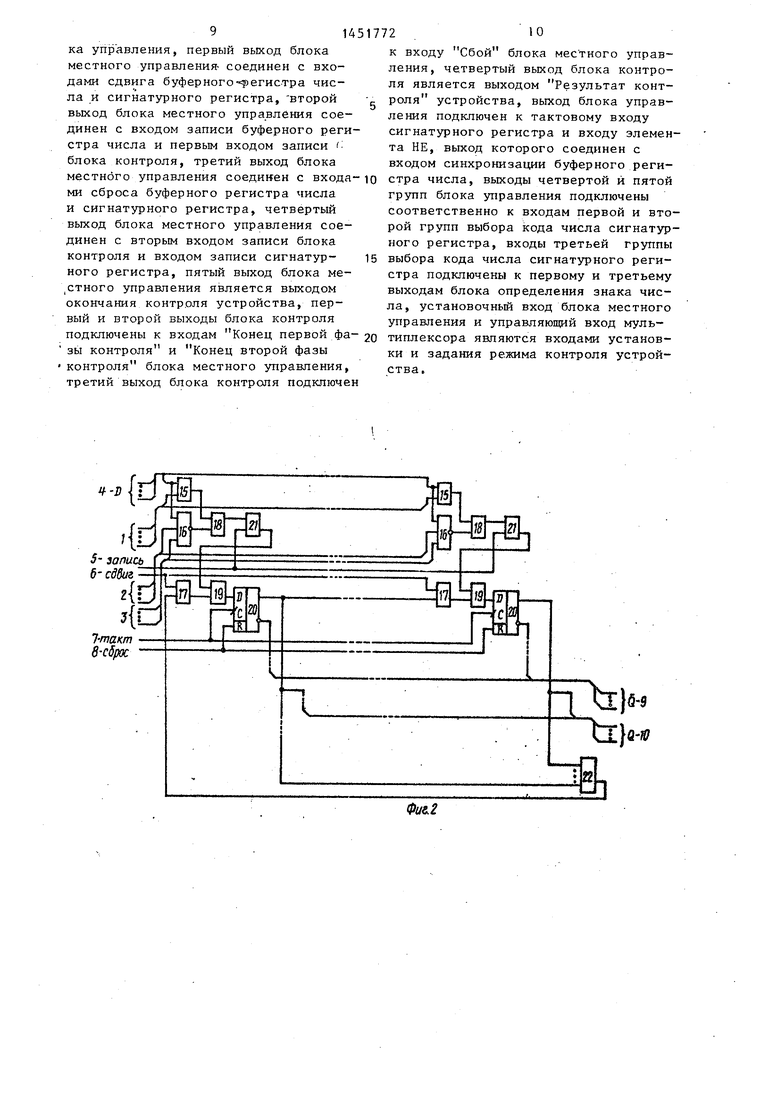

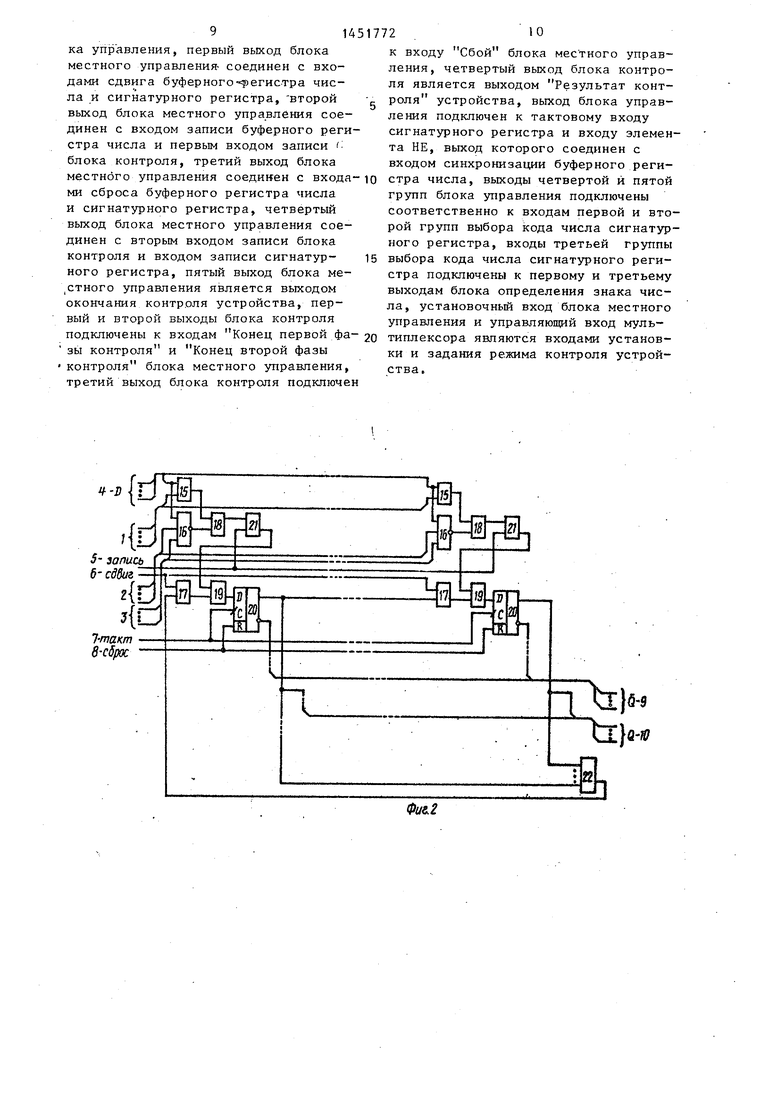

Изобретение относится к вычислительной технике и может быть использовано в специализированных микропроцессорных системах для параллельной обработки больших массивов информации в реальном масштабе времени. Целью изобретения является повышение достоверности функционирования устройства за счет его самодиагностиро вания. Устройство содержит накопитель 1 на регистрах 2 сдвига, блок 3 определения знака числа, блок 4 управления, буферный регистр 5 числа, сумматор 6, первый 7 и второй 8 выходные регистры числа, элементы ИЛИ 9, сигнатурный регистр 10,мультиплексор 11, блок 12 контроля, элемент НЕ 13, блок 14 местного управления. Уст ройство работает в режимехранения информации, в режиме обработки инфор мации и в режиме самодиагностирования . 6 ил. - с (Л

изводится обьмное арифметическое ело- держки и злемента 32 ИСКЛЮЧАЮЩЕЕ ИПИ жение операндов. Результат суммиро- ,,g формирует импульс сброса на одноимен-; вания через элементы PiJIH 9 поступа- ные входы регистров 5 и 10. Через инет на буферный регистр 5 числа и далее на разрядные входы накопителя 1. Знак суммы из блока 3 определения знака числа поступает непосредственно на ед знаковый вход накопителя 1. Если знаки операндов не совпадают, то на выходе блока 3 формируется сигнал, управляющий преобразованием кода суммы в буферном регистре 5 числа, а на выходах 1 или 3 блока 3 появляется сигнал, управляющий преобразованием

тервал времени, определяемый элементом 33 задержки, формируются управляющие сигналы сдвига и записи, определяющие режимы работы регистров 5 и 10.

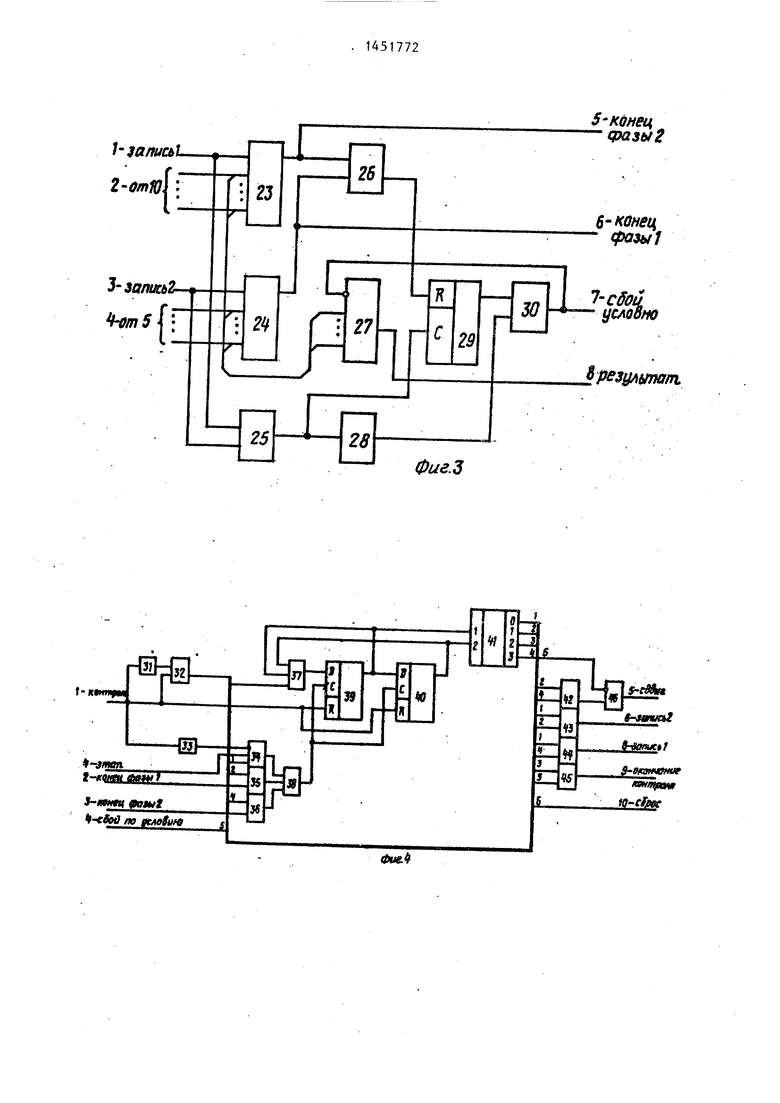

Самодиагностирование проводится в два этапа. На первом этапе сигнатур- ньй регистр 10 является генератором gg псевдослучайного теста. В это время запись в регистр невозможна, а осуществляется только сдвиг информации в регистре 10 и вьздача ее параллельно по всем выходам. Для инициализа

кода первого или второго числа в сигнатурном регистре 10, причем в об

тервал времени, определяемый элементом 33 задержки, формируются управляющие сигналы сдвига и записи, определяющие режимы работы регистров 5 и 10.

Самодиагностирование проводится в два этапа. На первом этапе сигнатур- ньй регистр 10 является генератором псевдослучайного теста. В это время запись в регистр невозможна, а осуществляется только сдвиг информации в регистре 10 и вьздача ее параллельно по всем выходам. Для инициализа

ции регистра 10 необходимо в момент сброса установить один разряд в единицу. Это можно осуществить, например, подключением входа 8 сигнатурного регистра 10 для первого разряда регистра не к входу сброса триггера 20, а к входу установки. Благодаря наличию линейных обратных связей

и

мого элементом ИСКЛЮЧАЮЩЕЕ ИЛИ 22, на выходи регистра 10 последовательно будут вьщаны все возможные комбинации. Номера разрядов, выходы которых подключаются к входам элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 22, определяются разрядностью сигнатурного регистра.

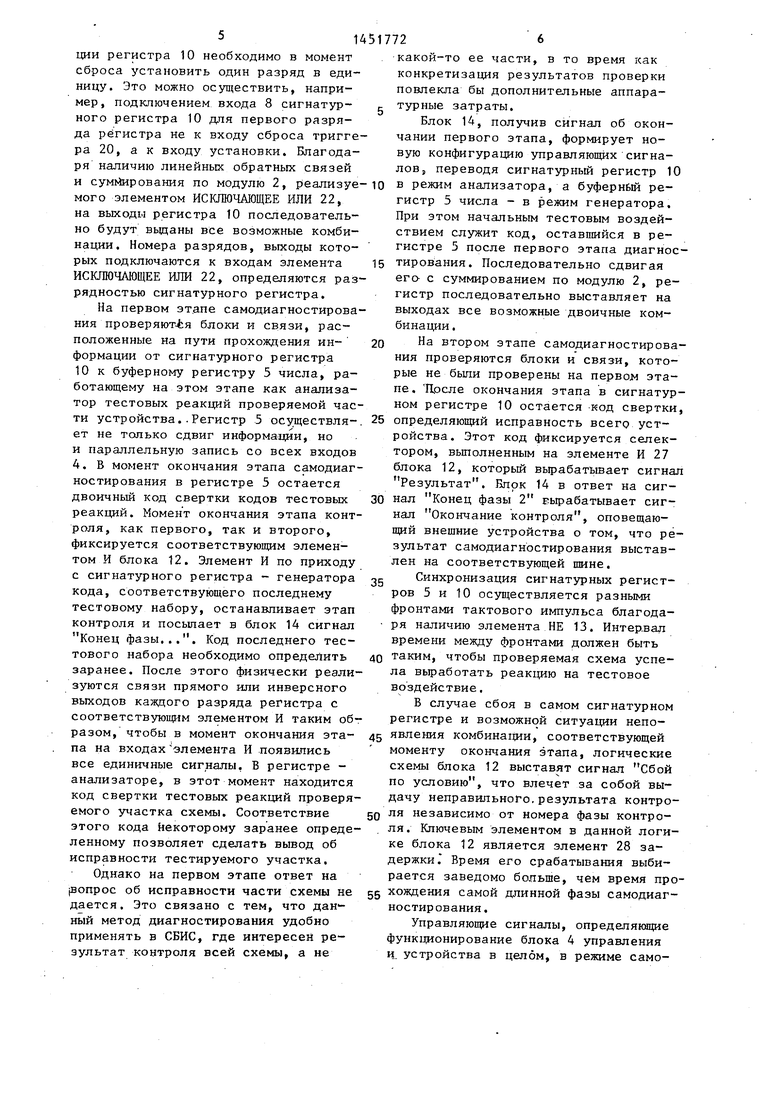

На первом эт.апе самодиагностирования проверяют ;я блоки и связи, расположенные на пути прохождения ин- формации от сигнатурного регистра 10 к буферному регистру 5 числа, работающему на этом этапе как анализатор тестовых реакций проверяемой части устройства..Регистр 5 осуществля-. ет не только сдвиг информации, но и параллельную запись со всех входов 4. В Момент окончания этапа самодиагностирования в регистре 5 остается двоичный код свертки кодов тестовых реакций. Момен т окончания этапа контроля, как первого, так и второго, фиксируется соответствующим элементом И блока 12. Элемент И по приходу с сигнатурного регистра - генератора кода, соответствующего последнему тестовому набору, останавливает этап контроля и посыпает в блок 14 сигнал Конец фазы.... Код последнего тестового набора необходимо определить заранее. После этого физически реали- зуются связи прямого или инверсного выходов каждого разряда регистра с соответствующим элементом И таким образом, чтобы в момент окончания этапа на входах элемента И появились все единичные сигналы, В регистре - анализаторе, в этот момент находится код свертки тестовых реакций проверяемого участка схемы. Соответствие этого кода Некоторому заранее определенному позволяет сделать вывод об исправности тестируемого участка.

Однако на первом этапе ответ на Вопрос об исправности части схемы не дается. Это связано с тем, что ный метод диагностирования удобно применять в СБИС, где интересен результат контроля всей схемы, а не

какой-то ее части, в то время как конкретизация результатов проверки повлекла бы дополнительные аппаратурные затраты.

Блок 14, получив сигнал об окончании первого этапа, формирует новую конфигурацию управляющих сигналов, переводя сигнатурный регистр 1

сумь4ирования по модулю 2, реализуе-ю в режим анализатора, а буферный регистр 5 числа - в режим генератора. При этом начальным тестовым воздействием служит код, оставшийся в регистре 5 после первого этапа диагнос 15 тирования. Последовательно сдвигая его- с суммированием по модулю 2, регистр последовательно выставляет на выходах все возможные двоичные комбинации .

20 На втором этапа самодиагностирова ния проверяются блоки и связи, которые не быпи проверены на первом этапе. После окончания этапа в сигнатур ном регистре 10 остается код свертки 25 определяющий исправность всего устройства. Этот код фиксируется селектором, выполненным на элементе И 27 блока 12, который вырабатывает сигна Результат. Епрк 14 в ответ на сиг- 30 нал Конец фазы 2 вырабатывает сигнал Окончание контроля, оповещающий внешние устройства о том, что ре зультат самодиагностирования выставлен на соответствзтощей шине. 25 Синхронизация сигнатурных регистров 5 и 10 осуществляется разными фронтами тактового импульса благода- ря наличию элемента НЕ 13. Интервал

времени между фронтами должен быть 40 таким, чтобы проверяемая схема успела выработать реакцию на тестовое воздействие,

В случае сбоя в самом сигнатурном регистре и возможной ситуации непо- 45 явления комбинации, соответствующей моменту окончания этапа, логические схемы блока 12 выставят сигнал Сбой по условию, что влечет за собой выдачу неправильного.результата контро- 50 ля независимо от номера фазы контро- , ля. Кпючевым элементом в данной логике блока 12 является элемент 28 задержки. Время его срабатывания выбирается заведомо больше, чем время про 55 хождения самой длинной фазы самодиагностирования.

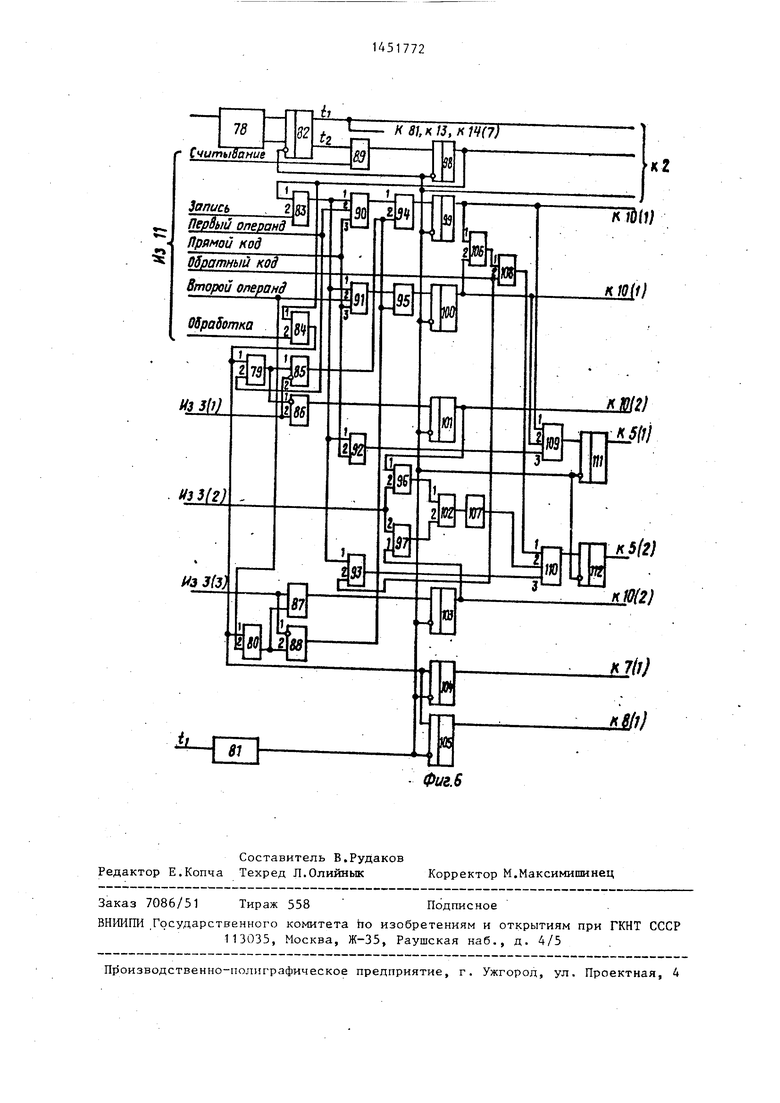

Управляющие сигналы, определяющие функционирование блока 4 управления И. устройства в целом, в режиме самокакой-то ее части, в то время как конкретизация результатов проверки повлекла бы дополнительные аппаратурные затраты.

Блок 14, получив сигнал об окончании первого этапа, формирует новую конфигурацию управляющих сигналов, переводя сигнатурный регистр 10

в режим анализатора, а буферный регистр 5 числа - в режим генератора. При этом начальным тестовым воздействием служит код, оставшийся в регистре 5 после первого этапа диагнос- тирования. Последовательно сдвигая его- с суммированием по модулю 2, регистр последовательно выставляет на выходах все возможные двоичные комбинации .

На втором этапа самодиагностирования проверяются блоки и связи, которые не быпи проверены на первом этапе. После окончания этапа в сигнатурном регистре 10 остается код свертки, определяющий исправность всего устройства. Этот код фиксируется селектором, выполненным на элементе И 27 блока 12, который вырабатывает сигнал Результат. Епрк 14 в ответ на сиг- нал Конец фазы 2 вырабатывает сигнал Окончание контроля, оповещающий внешние устройства о том, что результат самодиагностирования выставлен на соответствзтощей шине. Синхронизация сигнатурных регистров 5 и 10 осуществляется разными фронтами тактового импульса благода- ря наличию элемента НЕ 13. Интервал

времени между фронтами должен быть таким, чтобы проверяемая схема успела выработать реакцию на тестовое воздействие,

В случае сбоя в самом сигнатурном регистре и возможной ситуации непо- явления комбинации, соответствующей моменту окончания этапа, логические схемы блока 12 выставят сигнал Сбой по условию, что влечет за собой выдачу неправильного.результата контро- ля независимо от номера фазы контро- я. Кпючевым элементом в данной логике блока 12 является элемент 28 заержки. Время его срабатывания выбирается заведомо больше, чем время про- ождения самой длинной фазы самодиагностирования.

Управляющие сигналы, определяющие ункционирование блока 4 управления . устройства в целом, в режиме самоV14

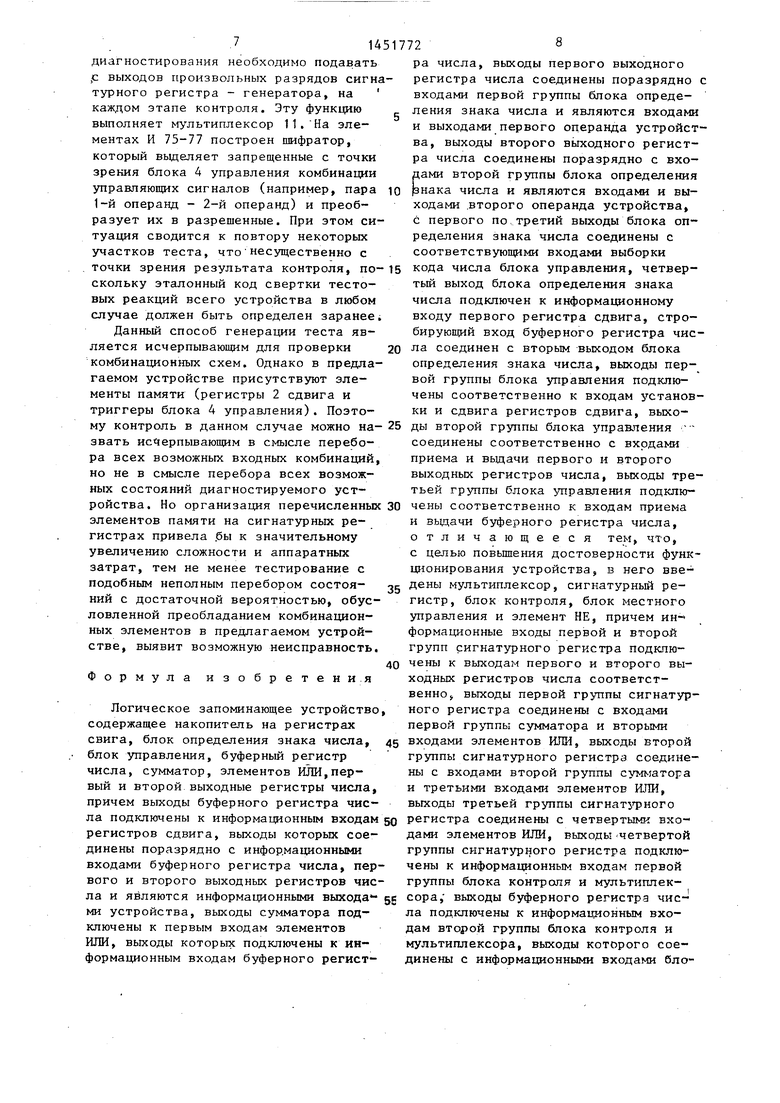

диагностирования необходимо подавать ,с выходов произвольных разрядов сигнатурного регистра - генератора, на каждом этапе контроля. Эту функцию выполняет мультиплексор 11, На элементах И 75-77 построен шифратор, который вьщеляет запрещенные с точки зрения блока 4 управления комбинации управляющих сигналов (например, пара 1-й операнд - 2-й операнд) и преобразует их в разрешенные. При этом ситуация сводится к повтору некоторых участков теста, что несущественно с

точки зрения результата контроля, по- 15 кода числа блока управления, четверскольку эталонный код свертки тестовых реакций всего устройства в любом случае должен быть определен заранееi Данный способ генерации теста является исчерпывающим для проверки комбинационных схем. Однако в предлагаемом устройстве присутствуют элементы памяти (регистры 2 сдвига и триггеры блока 4 управления). Поэтому контроль в данном случае можно на- звать исчерпывающим в смысле перебора всех возможных входных комбинаций, но не в смысле перебора всех возможных состояний диагностируемого уст-

ройства. Но организация перечисленных 30 чены соответственно к входам приема элементов памяти на сигнатурных регистрах привела бы к значительному увеличению сложности и аппаратных затрат, тем не менее тестирование с подобным неполным перебором состояний с достаточной вероятностью, обусловленной преобладанием комбинационных элементов в предлагаемом устройстве, выявит возможную неисправность.

и выдачи буферного регистра числа, отличающееся тем, что, с целью повьппения достоверности функционирования устройства, в него вве- 25 дены мультиплексор, сигнатурньй регистр, блок контроля, блок местного управления и элемент НЕ, причем информационные входы первой и второй групп сигнатурного регистра подкпю- 40 чены к выходам первого и второго выходных регистров числа соответственно выходы первой группы сигнатурного регистра соединены с входами первой группы сумматора и вторьп и 45 входами элементов ИШ1, выходы второй группы сигнатурного регистра соединены с входами второй группы сумматора и третьими входами элементов ИЛИ, выходы третьей группы сигнат фного ла подключены к информационным входам 50 регистра соединены с четвертызми вхо- регистров сдвига, выходы которых сое- дами элементов ИЛИ, выходы-четвертой динены поразрядно с информационными группы сигнатурного регистра подклю- входами буферного регистра числа, пер- чены к информационным входам первой вого и второго выходных регистров чис- группы блока контроля и мультиплек- ла и являются информационными выхода 55 сора, выходы буферного регистра чисФормула изобретени-я

Логическое запоминающее устройство, содержащее накопитель на регистрах свига, блок определения знака числа, блок управления, буферный регистр числа, сумматор, элементов ИЛИ,первый и второй выходные регистры числа, причем выходы буферного регистра чис-

ми устройства, выходы сумматора подключены к первым входам элементов ИЛИ, выходы которых подключены к информационным входам буферного регист-

ра числа, выходы первого выходного регистра числа соединены поразрядно с входами первой группы блока определения знака числа и являются входами и выходами первого операнда устройства, выходы второго выходного регистра числа соединены поразрядно с входами второй группы блока определения рнака числа и являются входами и выходами .второго операнда устройства, с первого по,третий выходы блока определения знака числа соединены с соответствуюш 1ми входами выборки

тый выход блока определения знака числа подключен к информационному входу первого регистра сдвига, стро- бирующий вход буферного регистра числа соединен с вторым выходом блока определения знака числа, выходы первой группы блока управления подключены соответственно к входам установки и сдвига регистров сдвига, выходы второй группы блока управления -- соединены соответственно с входами приема и выдачи первого и второго выходных регистров числа, выходы третьей группы блока управления подклюла подключены к информационным входам второй группы блока контроля и мультиплексора, выходы которого соединены с информационными входами блока управления, первый выход блока местного управления- соединен с входами сдвига буферного регистра числа и сигнатурного регистра, второй выход блока местного управления соединен с входом записи буферного регистра числа и первым входом записи блока контроля, третий выход блока местного управления соедикен с входа ми сброса буферного регистра числа и сигнатурного регистра, четвертый выход блока местного управления соединен с вторым входом записи блока контроля и входом записи сигнатур- ного регистра, пятый выход блока ме- стного управления является выходом окончания контроля устройства, первый и второй выходы блока контроля подключены к входам Конец первой фа зы контроля и Конец второй фазы контроля блока местного управления, третий выход блока контроля подключе

к входу Сбой блока местного управления, четвертый выход блока контроля является выходом Результат контроля устройства, выход блока управления подключен к тактовому входу сигнатурного регистра и входу элемента НЕ, выход которого соединен с входом синхронизации буферного регистра числа, выходы четвертой и пятой групп блока управления подключены соответственно к входам первой и второй групп выбора кода числа сигнатурного регистра, входы третьей группы выбора кода числа сигнатурного регистра подключены к первому и третьему выходам блока определения знака числа, установочньй вход блока местного управления и управляющий вход мультиплексора являются входами установки и задания режима контроля устройства.

Фиг.5

ИШ.

| Логическое запоминающее устройство | 1980 |

|

SU942152A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Логическое запоминающее устройство | 1985 |

|

SU1394239A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1989-01-15—Публикация

1986-07-11—Подача