Изобретение относится к звуковой информатике, в частности к технике программируемого воспроизведения речевых, музыкальных и прочих звуковых сигналов, накопленных в форме цифровых данных с сокращенной избыточностью в твердотельной памяти.

Цель изобретения - пояышение качества воспроизведения компилируемых ю звуковых сообщений.

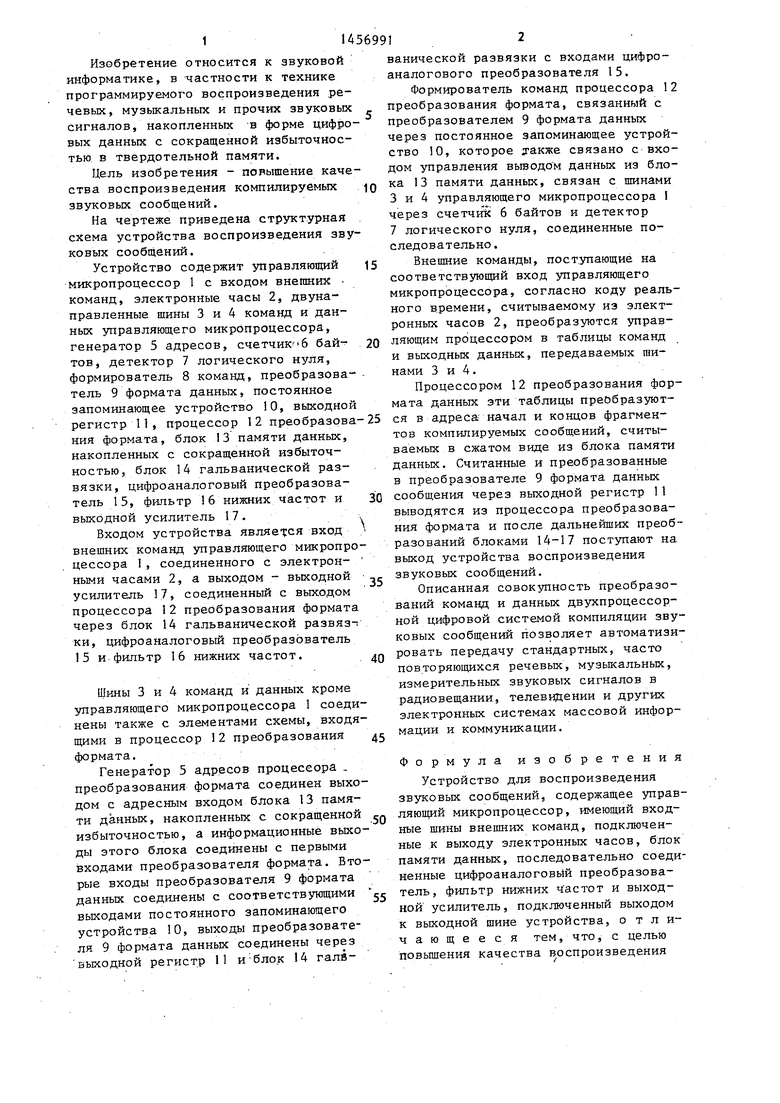

На чертеже приведена структурная схема устройства воспроизведения звуковых сообщений.

Устройство содержит управляющий 15 мрпсропроцессор 1 с входом внещних команд, электронные часы 2, двунаправленные шины 3 и 4 команд и данных управляющего микропроцессора, генератор 5 адресов, счетчик -б бай- 20 тов, детектор 7 логического нуля, формирователь 8 команд, преобразова- - тель 9 формата данных, постоянное запоминающее устройство 10, выходной

ванической развязки с входами цифро- аналогового преобразователя 15.

Формирователь команд процессора 1 преобразования формата, связанный с преобразователем 9 формата данных через постоянное запоминающее устрой ство 10, которое акже связано с вхо дом управления вьшодо м данных из бло ка 13 памяти данных, связан с шинами 3 и 4 управляющего микропроцессора через счетчи5: 6 байтов и детектор 7 логического нуля, соединенные последовательно .

Внешние команды, пост.упающие на соответствующий вход управляющего микропроцессора, согласно коду реаль ного времени, считываемому из электронных часов 2, преобразуются управляющим процессором в таблицы команд и выходных данных, передаваемых шинами 3 и 4.

Процессором 12 преобразования фор мата данных эти таблицы преобразуют

запимииаклцее уi, i juiriv-i о j v , x..-,-,-,..«,,

регистр 11, процессор 12 преобразова-25 ся в адреса начал и концов фрагмен

.,i,Fww4i trf -m-fi fr i-t f ЧЛЗТЛ Г о tJ T iI

НИЯ формата, блок 13 памяти данных, накопленных с сокращенной избыточностью, блок 14 гальванической развязки, цифроаналоговый преобразователь 15, фильтр 16 нижних частот и 30 выходной усилитель 17.ч

Входом устройства является вход внешних команд управляющего микропроцессора 1, соединенного с электронными часами 2, а выходом - выходной .js усилитель 17, соединенный с выходом процессора 12 преобразования формата через блок 14 гальванической развяз-i ки, цифроаналоговый преобразователь 15 и фильтр 16 нижних частот. дО

Шины 3 и 4 команд и данных кроме управляющего микропроцессора 1 соединены также с элементами схемы, входящими в процессор 12 преобразования 45 формата.

Генератор 5 адресов процессора - преобразования формата соединен выходом с адресным входом блока 13 памяти данных, накопленных с сокращенной JQ избыточностью, а информационные выходы этого блока соединены с первыми входами преобразователя формата. Вторые входы преобразователя 9 формата данных соединены с соответствующими 55 выходами постоянного запоминающего устройства 10, выходы преобразователя 9 формата данных соединены через выходной регистр П и-блок 14 галвтов компилируемых сообщений, считываемых в сжатом виде из блока памят данных. Считанные и преобразованные в преобразователе 9 формата данных сообщения через выходной регистр 1 1 выводятся из процессора преобразова ния формата и после дальнейших прео разований блоками 14-17 поступают н выход устройства воспроизведения звуковых сообщений.

Описанная совокупность преобразо ваний команд и данных двухпроцессор ной цифровой системой компиляции зв ковых сообщений позволяет автоматиз ровать передачу стандартных, часто повторяющихся речевых, музыкальных, измерительных звуковых сигналов в радиовещании, телевидении и других электронных системах массовой инфор мации и коммуникации.

Формула изобретени

Устройство для воспроизведения звуковых сообщений, содержащее упра ляющий микропроцессор, имеющий вход ные шины внешних команд, подключенные к выходу электронных часов, бло памяти данных, последовательно соед ненные цифроаналоговый преобразователь, фипьтр нижних ч астот и выходной усилитель, подключенный выходом к выходной шине устройства, отли чающееся тем, что, с целью повьш1ения качества в оспроизведения

ванической развязки с входами цифро- аналогового преобразователя 15.

Формирователь команд процессора 12 преобразования формата, связанный с преобразователем 9 формата данных через постоянное запоминающее устройство 10, которое акже связано с входом управления вьшодо м данных из блока 13 памяти данных, связан с шинами 3 и 4 управляющего микропроцессора через счетчи5: 6 байтов и детектор 7 логического нуля, соединенные последовательно .

Внешние команды, пост.упающие на соответствующий вход управляющего микропроцессора, согласно коду реального времени, считываемому из электронных часов 2, преобразуются управляющим процессором в таблицы команд и выходных данных, передаваемых шинами 3 и 4.

Процессором 12 преобразования формата данных эти таблицы преобразуют-,-,..«,,

ся в адреса начал и концов фрагмен

ся в адреса начал и концов фрагмен

,i,Fww4i trf -m-fi fr i-t f ЧЛЗТЛ Г о tJ T iI

тов компилируемых сообщений, считываемых в сжатом виде из блока памяти данных. Считанные и преобразованные в преобразователе 9 формата данных сообщения через выходной регистр 1 1 выводятся из процессора преобразования формата и после дальнейших преобразований блоками 14-17 поступают на выход устройства воспроизведения звуковых сообщений.

Описанная совокупность преобразований команд и данных двухпроцессорной цифровой системой компиляции звуковых сообщений позволяет автоматизировать передачу стандартных, часто повторяющихся речевых, музыкальных, измерительных звуковых сигналов в радиовещании, телевидении и других электронных системах массовой информации и коммуникации.

Формула изобретения

Устройство для воспроизведения звуковых сообщений, содержащее управляющий микропроцессор, имеющий входные шины внешних команд, подключенные к выходу электронных часов, блок памяти данных, последовательно соединенные цифроаналоговый преобразователь, фипьтр нижних ч астот и выходной усилитель, подключенный выходом к выходной шине устройства, отличающееся тем, что, с целью повьш1ения качества в оспроизведения

компилируемых звуковьк сообщений, в него введены последовательно соединенные процессор преобразования формата данных и блок гальванической развязки, подключенный выходом к входу цифроаналогового преобразователя, процессор преобразования формата данных выполнен в виде преобразователя

частоты дискретизации от управлягащего микропроцессора, выход - с управляющими входами генератора адресов, счетчика байтов, логического детектора, выходного регистра и с одним управляющим входом управляюшего постоянного запоминающего устройства,

ных выполнен в виде преоира.иь.4... ДРУГОЙ управляющий вход которого формата данньк, управляющего постоян- ю подключен к линии сигнала тактовой ного запоминающего устройства, вьпсод- частоты от управляющего микропроцес -т ного регистра, генератора адресов, счетчика байтов, логического детектора и формирователя команд, при этом генератор адресов, счетчик байтов и формирователь команд соединены входами через двунаправленные шины команд и данных с управлявшим микропроцессором, счетчик байтов выходом подключен по двунаправленной шине через логический детектор к второму .входу формирователя команд, третий вход которого соединен с линией сигнала

сора и которое связано двунаправленными шинами с формирователем команд и через преобразователь формата дан15 ных и выходной регистр - с блоком

гальванической развязки, а блок памяти данных связан двунаправленными шинами с генератором адресов и преобразователем формата данных и подклю20 чен управляющем входом через линию сигнала чтения к соответств тощему выходу управляющего постоянного запоминающего устройства.

U56$ 91

ДРУГОЙ управляющий вход которого подключен к линии сигнала тактовой частоты от управляющего микропроцес -т

сора и которое связано двунаправленными шинами с формирователем команд и через преобразователь формата данных и выходной регистр - с блоком

гальванической развязки, а блок памяти данных связан двунаправленными шинами с генератором адресов и преобразователем формата данных и подключен управляющем входом через линию сигнала чтения к соответств тощему выходу управляющего постоянного запоминающего устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО КОНТРОЛЯ ПРОЧНОСТИ КРЫЛА ВОЗДУШНОГО СУДНА | 2011 |

|

RU2469289C1 |

| Устройство для обмена информацией | 1987 |

|

SU1497619A1 |

| СИСТЕМА ТРЕВОЖНОЙ СИГНАЛИЗАЦИИ | 1994 |

|

RU2103744C1 |

| МИКРОПРОЦЕССОР ВВОДА-ВЫВОДА ИНФОРМАЦИИ | 1992 |

|

RU2042182C1 |

| ЭЛЕКТРОННЫЕ ЧАСЫ С РЕЧЕВЫМ ОПОВЕЩЕНИЕМ | 1992 |

|

RU2029333C1 |

| КОНТРОЛЛЕР ПЕРЕДАЧИ ДАННЫХ | 2013 |

|

RU2514135C1 |

| ВОСПРОИЗВОДЯЩЕЕ УСТРОЙСТВО И СПОСОБ ВОСПРОИЗВЕДЕНИЯ | 2000 |

|

RU2253146C2 |

| Адаптер магистрального последовательного интерфейса мультиплексного канала информационного обмена | 2016 |

|

RU2639959C2 |

| ПАРАЛЛЕЛЬНАЯ ПРОЦЕССОРНАЯ СИСТЕМА | 1991 |

|

RU2084953C1 |

| Устройство для отображения информации | 1986 |

|

SU1441450A1 |

Устройство для воспроизведения , звуковых сообщений содержит блок 13 памяти данных, накопленных с сокращенной избыточностью, два процессора 1 и 12, электронные часы 2, блок 14 гальваническор развязки, цифро- аналоговый преобразователь 15, фильтр нижних частот 16 и выходной усилитель 17. Первый процессор управляет компиляцией фрагментов звуковых сообщений в заданные моменты времени, отсчитываемые элек тронными часами, второй считывает фрагменты из блока памяти и восстанавливает формат радиовещательных сигналов. 1 ил. (Л 4ik сл о

| Патент США № 4449232, кл | |||

| Подвесная канатная дорога | 1920 |

|

SU381A1 |

| Колосниковая решетка с чередующимися неподвижными и движущимися возвратно-поступательно колосниками | 1917 |

|

SU1984A1 |

Авторы

Даты

1989-02-07—Публикация

1986-09-24—Подача