0,00.10,.,. ,,.010

.j .-

010

V

1.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения на коэффициенты | 1986 |

|

SU1442987A1 |

| Устройство для умножения на коэффициенты | 1985 |

|

SU1397901A1 |

| Устройство для умножения на коэффициенты | 1985 |

|

SU1305663A1 |

| Устройство для умножения на коэффициенты | 1988 |

|

SU1562904A1 |

| Устройство для умножения | 1976 |

|

SU651341A1 |

| Устройство для умножения переменной на дробь | 1987 |

|

SU1543400A1 |

| Устройство для умножения | 1989 |

|

SU1667061A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| Устройство для умножения | 1981 |

|

SU1018115A1 |

| Устройство для умножения чисел | 1990 |

|

SU1714595A1 |

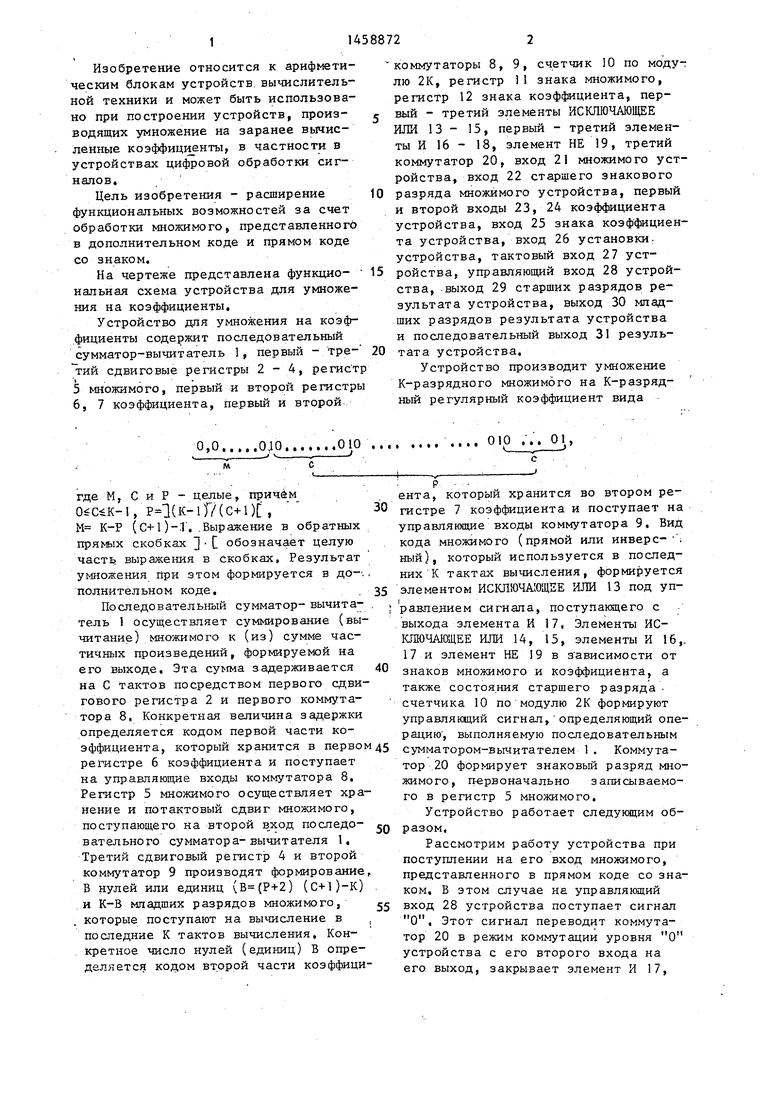

Изобретение относится к арифметическим блокам устройств вычисли- . тельной техники я может быть использовано при построении устройств, производящих умножение на заранее вычисленные коэффициенты, в частности в устройствах цифровой обработки сигналов. Цель изобретения - расширение функциональных возможностей за счет обработки множимого, представленного в дополнительном коде и в прямом коде со знаком. Устройство для у1чноже- ния на коэффициенты содержит последовательный сумматор-вычитатель 1,, сдвиговые регистры 2-4, регистры множимого 5, коэффициента 6, 7, коммутаторы 8, 9, счетчик по модулю 2К 10, регистры знаков множимого 11 и коэффициента 12, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 13-15, элементы И 16-18, элемент НЕ 19, коммутатор 20, входы 21-28 устройства и выходы 29-3J устройства. Поставленная цель достигается введением элемента ИСКЛЮЧАЮЩЕЕ ШШ 15, элементов И 17, 18, элемента НЕ 19 и коммутатора 20. 1 ил. (Л

где М, С и Р - целые, причём O CiK-1, (К-ГГ/(С+1) ,

М К-Р (С+1)-.Т, .Выражение в обратных пря№1Х скобках З С обозначает целую часть выражения в скобках. Результат умножения При этом формируется в до- . полнительном коде,.

Последователыгош сумматор- вычита- тель 1 осуществляет суммирование (вычитание) . множимого к (из) сумме частичных произведений, формируемой на его выходе. Эта сумма задерживается на С тактов посредством первого сдвигового регистра 2 и первого коммутатора 8, Конкретная величина задержки определяется кодом первой части коэффициента, который хранится в перво регистре 6 коэффициента и поступает на управляющие входы коммутатора 8, Регистр 5 множимого осуществляет хранение и потактовый сдвиг множимого, поступающего на второй последо- вательного сумматора-вычитателя 1, Третий сдвиговый регистр 4 и второй коммутатор 9 производят формирование В нулей или единиц (В(Р+2) (С+1)-К) .и К-В младших разрядов множимого,

которые поступают на вычисление в последние К тактов вычисления. Конкретное число нулей (единиц) Б определяется кодом второй части коэффициента, который хранится во втором регистре 7 коэффициента и поступает на управлякидие входы коммутатора 9, ВиД кода множимого (прямой или инверс- ный), который используется в последних К тактах вычисления, формируется элементом ИСКЛЮЧАЮЩЕЕ ИЛИ 13 под управлением сигнала, поступающего с выхода элемента И 17. Элементы ИС- КЛЮЧАЩЕЕ ИЛИ 14, 13, элементы И 16,. 17 и элемент НЕ 19 в з ависимости от знаков множимого и коэффициента, а также состояния старшего разряда . счетчика 10 по модулю 2К формируют управляющий сигнал, определяющий операцию , выполняемую последовательным сумматором-вычитателем 1. Коммутатор 20 формирует знаковый разряд множимого, первоначально записываемого в регистр 5 множимого.

Устройство работает следукицим образом,

Рассмотрим работу устройства при поступлении на его вход множимого, представленного в прямом коде со знаком, В этом случае на управляющий вход 28 устройства поступает сигнал О. Этот сигнал переводит коммутатор 20 в режим коммутации уровня О устройства с его второго входа на его выход, закрывает элемент И 17,

в результате чего на выходе элемента НЕ 19 формируется сигнал 1, чем разрешается прохождение сигнала с выхода счетчика 10 по модулю 2К через элемент И 16, и разрешает прохождение сигнала через элемент И 18,

В начале каждого цикла вычисления на установочный вход 26 устройства поступает импульс, который производит обнуление последовательного сумматор а-вы читателя 1, счетчика 10 и сдвиговых регистров 2-4, Этим же импульсом производится запись множимого с входа 21 множимого в регистр 5 множимого (при этом в его старший знаковый разряд записывается значе- . ние нуля с выхода коммутатора 20), первой и.второй частей коэффициента соответственно с входов 23, 24 коэффициента в регистры 6, 7 коэффициента, знака множимого с входа 22 старшего знакового разряда множимого в регистр 11 знака множимого и знака коэффициента в регистр 12 знака коэф 4ициента, Затем на тактовый вход 27 устройства начинают поступать тактовые импульсы, причем их количество в каждом цикле умножения равно 2К.

В случае, если знаки множимого и коэффициента одинаковые, то одноименные сигналы, поступающие на входы элемента ИСК)1ЮЧАЮШЕЕ ИЛИ 15 с выхода регистра 12 знака коэффициента и через элемент И 18 с выхода регистра 11 знака множимого, генерируют на выходе элемента ИСКЛЮЧАЩЕЕ ИЛИ 15 сигнал О, который переводит элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 14 в режим повторителя, В результате этого сигнал с выхода старшего разряда счетчика 10 по модулю 2К без изменения проходит на управляющий вход последовательного сумматора-вычитателя 1, Поэтому последний работает в режиме суммирования первые К тактов вычисления, а последние К тактов вычисления - в режиме Ъычитания, Если же знаки множимого и коэффициента будут различны№1, то режи№1 работы последовательного сум- .матора-вычитателя 1 будут противоположными, чем рассмотренные выше,

С началом поступления тактовых импульсов в регистре 5 множимого производится пот акт о вый сдвиг ьшожимого, которое, начиная с младшего разряда, поступает на второй вход последовательного сумматора- вычитателя 1 и в зависимости от сигнала на его управляющем входе суммируется или вычита-. ется из значения суммы частичных произведений, которая поступает на первый вход последовательного сумматора- вычитателя 1 с его же выхода, но задержанная на С тактов в сдвиговом регистре 2 и коммутаторе 8,

По мере выхода из регистра 5 мно - 0 жимого старших разрядов множимого в него на освободившееся место с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 13, который в данном случае работает в режиме повторителя, вновь записывается зна- 5 чение множимого. Причем в связи с i .. тем, что в начале каждого цикла умножения сдвиговый регистр 4 обнуляется, между старшим разрядом первоначально записанного множимого и младшим раз- 0 рядом вновь записываемого числа будет сформировано В нулей (В.ЬО), В результате после первых К тактов вычисления в регистре 5 множимого будет сформировано число, состоящее из 5 В нулей и К-В бит мпадших разрядов ffloжимoгo, Это число в течение пос-- ледних К тактов вычисления поступает на второй вход последовательного сумматора-вычитателя 1,

0 В течение 2К тактов вычисления с Ъыхода младшего ра зряда сдвигового регистра 2 по последовательный выход 31 результата устройства последовательно поступают 2К бит результата с умножения в последовательном коде. Последние К тактов вычисления с выхода старшего разряда сдвигового per гистра 2 в сдвиговый регистр 3 переписываются К младших разрядов произ- 0 ведения, В результате в конце каждого цикла умножения в сдвиговом регистре 3 оказываются сформированные К младших разрядов произведения, которые поступают на выход 30 младших разря- 5 дов результата устройства, а в сдвиговом регистре 2-К старших разрядов произведения, которые поступают на выход 29 старших разрядов результата устройства,

0

Формула изобретения

Устройство для умножения на коэффициенты, содержащее первый и второй 5 коммутаторы, первый, второй и третий сдвиговые регистры, счетчик по модулю 2К (к - разрядность множимого и коэффициента), первый и второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, первый эле10

15

20

мент И, первый и второй реп1стрь ко- эффициента, регистр множимого, регистр знака шожимого, регистр знака коэффициента и последовательный сум- матор-вычитатель, выход которого соединен с информационным входом первого сдвигового регистра, разрядные выходы которого соединены соответственно с информационными входами первого коммутатора и выходами старших разрядов результата устройства, последовательный выход разрядов результата которого соединен с выходом младшего разряда результата первого сдвигового регистра, выход старшего разряда результата которого соединен с информационным входом второго сдвигового регистра, разрядные выходы которого соединены с выхрдами младших разрядов результата устройства, первый и второй входы коэффициента которого соединены соответственно с информационными входами первого и второго регистра коэффициента, разрядные выходы которых соединены соответственно с управляющим входом первого и второго коммутаторов, выход первого коммутатора соединен с первым информационным входом последовательного сумматора--вычитателя, второй информационный вход которого соединен с выходом регистра множимого, информационным входом третьего сдвигового регистра и первым информационным входом второго коммутатора, вь1ход которого соединен с первым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с информаци-. онным входом регистра множимого, ус- таноцочные входы которого, кроме первого, соединены соответственно с вхо- v дами разрядов мнош7мого, кроме старшего знакового разряда устройства, вход старшего знакового разряда множимого которого соединен с информационным входом регистра знака множимого, вход разрешения записи которого соединен с входами разрешения за1А5887.6

чика по модулю 2К и последовательного сумматора-вычитателя и входом ус- тановки устройства,тактовый вход которого соединен с тактовыми входами регистра множимого, первого, второго и третьего сдвиговых регистров, счетчика по модулю 2К и последовательного сумматора- -вычитателя, управляющий вход которого соединен с выходом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход которого соединен с выходом первого элемента И, рервый вход которого соединен с выходом старшего разряда счетчика по модулю 2К, каждый информационный вход второго коммутатора, начиная со второго, соединен соответственно с разрядными выходами третьего сдвигового регистг- ра, начиная с первого разряда, вход знака коэффициента устройства соединен с информационным входом регистра знака коэффициента, отличающееся тем, что, с целью расшире- 25 ния функциональных возможностей за счет обработки множимого, представ-: ленного и в дополнительном коде и в прямом коде со знаком, в него введены третий элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, второй и третий элементы И, элемент НЕ и третий коммутатор, цервый и второй информационные входы которого соединены соответственно с. входами старшего знакового разряда множимого и 35 нулевого потенциала устройства, управляющий вход которого соединен с управляющим входом третьего коммутатора, цервым входом второго элемента И и инверсным входом третьего элемента И, прямой вход которого соединен с выходом регистра знака множимого и вторым входом второго элемента И, выход которого соединен с вторым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 45 и входом элемента НЕ, выход которого соединен с вторым входом первого элемента И, первый и второй входы третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соедине30

40

ны с выходами третьего элемента И и

пи си первого и второго регистровкоэф-50 регистра знака коэффициента, а вы- фициента, регистра множимого и ре-ход - с вторым входом второго элегистра знака коэффициента и входамимента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход третьеустановки в 0 первого, второго иго коммутатора соединен с первым устретьего сдвиговых регистров, счет-тановочным входом регистра множимого.

| Устройство для умножения на коэффициенты | 1985 |

|

SU1305663A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для умножения на коэффициенты | 1985 |

|

SU1397901A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-02-15—Публикация

1987-06-23—Подача