:л

ээ

э

Изобретение относится к вычислительной технике и может быть использовано в арифметических блоках устройств цифровой обработки сигналов.

Цель изобретения - повышение производительности устройства за счет возможности конвейеризации процесса вычисления.

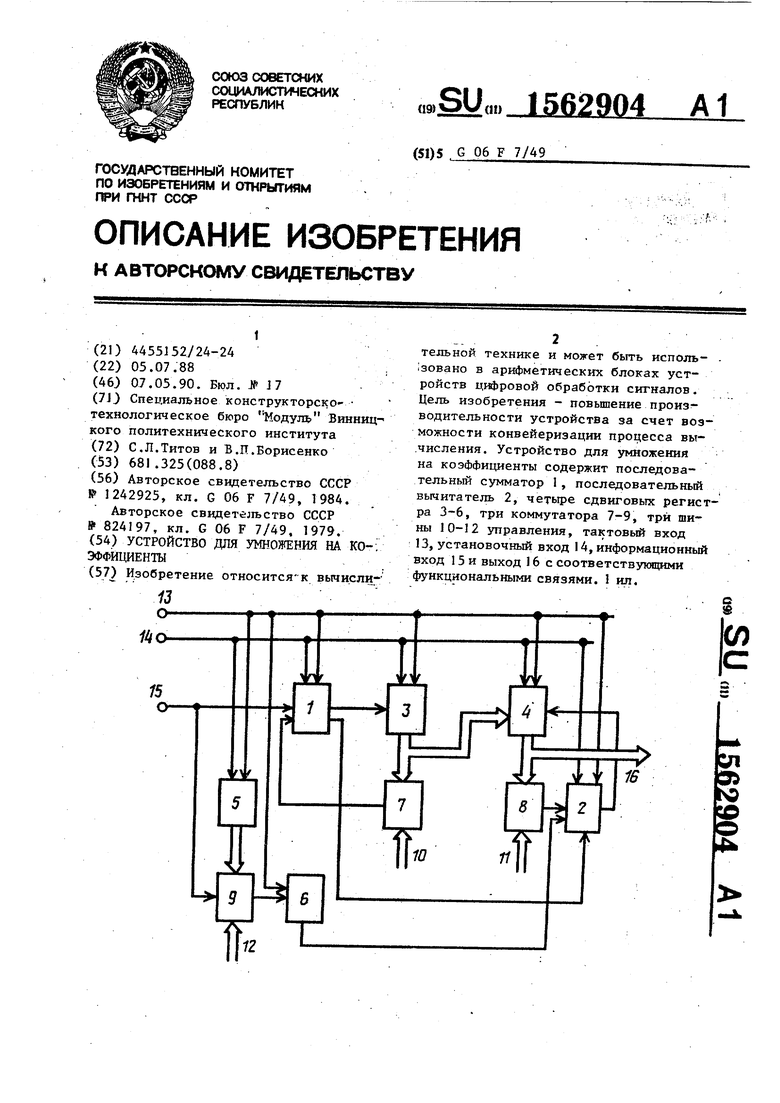

На чертеже представлена функцио- нальная схема устройства.

Устройство для умножения на коэффициенты содержит последовательный сумматор 1, последовательный вычита- |тель 2, первый 3, второй 4, третий 5 и четвертый 6 сдвиговые регистры, первый 7, второй 8 и третий 9 коммутаторы, первую 10, вторую 11 и третью 12 шины управления, тактовый вход 13, установочный вход 14, ин формационный вход 15 и выход 16с соответствующими функциональными связями.

Последовательный сумматор 3 в пер- вом цикле вычисления осуществляет формирование суммы частичных произведений, а последовательный вычкта- тель 2 в следующем цикле вычисления из сформированной суммы частичных npo изведений производит вычитание лишнего Р+2-го значения множимого. Первый сдвиговый регистр 3 и первый комму- / татор 7 осуществляют задержку суммы t частичных произведений, поступающей с выхода последовательного сумматора 1 на его дервый вход, на С тактов. 1фн- кретная величина задержки определд- ется управляющим ,кодом первой, части преобразованного коэффициента, но- ступающего по первой шине 10 управления на вход первого коммутатора 7. Аналогичную задачу выполняет управляющий код первой части преобразованног коэффициента, который поступает по второй шине 11 управления на вход второго коммутатора 8. Третий сдвиговый регистр 5 и третий коммутатор 9 производят формирование нулей В и младших раЗрЯДОВ МНОЖИМОГО, ПОСТупаЮ-

щих во втором цикле вычисления через четвертый сдвиговый регистр 6 на второй (вычитающий) вход последовательного вычитателя 2 для вычитания из суммы частичных произведений Р+2-го значения множимого. Конкретное число нулей В определяется кодом второй части преобразованного коэффициента, который поступает по третьей шине 12

управления на управляющие входы третьего коммутатора 9.

Устройство работает следуюшим образом.

В первом такте каждого цикла вычисления произведения сигнал, поступающий с входа 14 устройства на входы установки первого 3 и третьего 5 сдвиговых регистров, последовательного сумматора 1 и последовательного вычитателя 2, производит их обнуление и перезапись значения переноса последовательного сумматора 1 в триггер переноса последовательного вычитателя

2.Этот же сигнал, поступающий на вход разрешения параллельной записи второго сдвигового регистра 4, производит перезапись информации, находившейся в первом сдвиговом регистре

3.Затем на вход 13 устройства начинают поступать тактовые импульсы, причем число их в каждом цикле вычисления равно К.

С информационного входа 15 на второй вход последовательного сумматора 1 поразрядно, начиная с младшего разряда, поступают биты множимого. На первый вход последовательного сумматора 1 при этом с его же выхода через первый коммутатор 7 поступают биты суммы частичных произведений, задержанные на С тактов в первом сдвиговом регистре 3. В конце каждого цикла вычисления первый сдвиговый регистр 3 заполняется младшими разрядами К произведения.

Одновременно с формированием про- изведения биты множимого последовательно записываются в третий сдвиге- 1 вый регистр 5, третий коммутатор 9 при этом коммутирует на. свой выход сигнал, поступающий с инфо,рмационно- го входа 15 (для. ) , или сигнал- В-го выхода третьего сдвигового регистра 5 (для В 0) ,, Поэтому на выходе коммутатора 9 формируется К-В младших разрядов множимого перед которым следует В нулей, так как третий сдвиговый регистр 5 в начале цикла обнулялся. Сигнал с выхода третьего коммутатора 9 записывается в четвертый сдвиговый регистр 6 и используется в следующем цикле вычисления для вычитания из суммы частичных произведений и формирования действительных старших разрядов произведения.

В начале каждого цикла вычисления во второй сдвиговый регистр 4 производится параллельная перезапись младших разр ядов К произведения (суммы частичных произведений), сформированных в предыдущем цикле вычисления в первом сдвиговом регистре 3. Одновременно в триггер переноса последовательного вычитаталя 2 переписывается сигнал переноса с выхода переноса последовательного сумматора 1, а на вторую шину 11 передается первая часть преобразованного коэффициента с первой шины 10, под управлением которого производилось формирование суммы частичных произведений в сумматоре 1. С началом поступления на тактовый вход 13 устройства тактовых импульсов на первый вход последовательного вычитателя 2 через второй коммутатор 8 начинают поступать биты суммы частичных произведений, задержанные во втором сдвиговом регистре 4 на С тактов. Пока в течение В тактов с выхода четвертого сдвигового регистра 6 на второй (вычитающий) вход последовательного вычитателя 2 поступают В нулей, последний производит суммирование переноса с битами суммы частичных произведений. После поступления первого ненулевого бита с выхода четвертого сдвигового регистра 6 последовательный вычитатель 2 осуществляет вычитание множимого, поступающего на его второй (вычитающий) вход, из суммы частичных произведений, поступающих на его первый вход. В конце каждого цикла вычисления на втором сдвиговом регистре 4 записываются К старших разрядов произведения множимого, поступившепо на умножение в предыдущем цикле вычисления, на коэффициент, которые далее поступают на параллельный выход 16 устройства.

Таким образом, хотя общее время формирования результата умножения с учетом такта установки устройства равно 2(K+J) тактов, но данные на выходе поступают через каждый K+J такта.

Время цикла умножения можно сократить до К тактов (при формировании К-разрядного произведения) путем конвейеризации процесса вычисления, когда на последовательном сумматоре 1 в течение К тактов производится суммирование сумм частичных произведений, а в течение следующих К тактов (когда на сумматоре 1 производится сум- мирование следующей суммы частичных

0

5

0

5

0

5

0

5

0

5

произведений) на вьгчитателе 2 из суммы частичных произведений производится вычитание множимого.

Формула изобре.тения

Устройство для умножения на коэффициенты, содержащее последовательный сумматор, последовательный вычитатель, первый сдвиговый регистр, первый и второй коммутаторы, информационный вход устройства соединен с первым информационным входом побледова- тельного сумматора, выход которого соединен с информационным входом первого сдвигового регистра, разрядные выходы которого соединены соответственно с первой группой входов первого коммутатора, а первая и вторая шины управления устройства соединены соответственно с управляющими входами первого и второго коммутаторов, о т- личающееся тем, что, с целью повышения производительности устройства за счет возможности конвейеризации процесса вычисления, в него введены второй, третий и четвертый сдвиговые регистры, третий коммутатор и третья шина управления, причем . информационный вход устройства соединен с первым входом третьего комму - тзтора, входы второй группы которого соединены соответственно с разрядными выходами третьего сдвигового регистра со сдвигом на один разряд в сторону младших разрядов, третья шина управления соединена соответственно с управляющими входами третьего коммутатора, выход которого соединен с информационным входом четвертого сдвигового регистра, выход которого соединен с первым входом последовательного вычитателя, выход переноса последовательного сумматора соединен с входом переноса последовательного вычитателя, выход которого соединен с информационным входом последовательной записи второго сдвигового регистра, информационные входы параллельной записи которого соединены соответственно с разрядными выходами первого сдвигового регистра, разрядные выходы второго сдвигового регистра соединены соответственно с выходной шиной устройства и с входами первой группы второго коммутатора, выход которого соединен с вторым входом последовательного вычитателя, выход пер71562904 .8

вого коммутатора соединен с информа-а установочный вход устройства соедиционным входом последовательного сум-нен с установочными входами последоматора, тактовый вход устройства сое-вательного сумматора, последовательдинен с тактовыми входами последова-ного вычитателя, первого и третьего

тельного сумматора, последовательногосдвиговых регистров и входом развычитателя, первого, второго, треть-решения параллельной записи второго

его и четвертого сдвиговых регистров,сдвигового регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения на коэффициенты | 1986 |

|

SU1442987A1 |

| Устройство для умножения на коэффициенты | 1985 |

|

SU1397901A1 |

| Устройство для умножения на коэффициенты | 1987 |

|

SU1458872A1 |

| Устройство для умножения на коэффициенты | 1985 |

|

SU1305663A1 |

| Устройство для умножения на коэффициенты | 1985 |

|

SU1295381A1 |

| Устройство для умножения на коэффициенты | 1984 |

|

SU1242925A1 |

| Устройство для умножения на коэффициенты | 1985 |

|

SU1291966A1 |

| Устройство для умножения на коэффициенты | 1985 |

|

SU1291967A1 |

| Конвейерный умножитель | 1988 |

|

SU1575175A1 |

| Конвейерный цифровой умножитель | 1987 |

|

SU1464170A1 |

Изобретение относится к вычислительной технике и может быть использовано в арифметических блоках устройств цифровой обработки сигналов. Цель изобретения - повышение производительности устройства за счет возможности конвейеризации процесса вычисления. Устройство для умножения на коэффициенты содержит последовательный сумматор 1, последовательный вычитатель 2, четыре сдвиговых регистра 3 - 6, три коммутатора 7 - 9, три шины 10 - 12 управления, тактовый вход 13, установочный вход 14, информационный вход 15 и выход 16 с соответствующими функциональными связями. 1 ил.

| Устройство для умножения на коэффициенты | 1984 |

|

SU1242925A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Вычислительное устройство | 1979 |

|

SU824197A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-05-07—Публикация

1988-07-05—Подача