Од

ю

00

ю

СП

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки программ | 1984 |

|

SU1246100A1 |

| Устройство для формирования адресов памяти | 1984 |

|

SU1256027A2 |

| Устройство для обслуживания запросов | 1982 |

|

SU1109753A1 |

| Устройство для временного контроля сигналов интерфейса | 1986 |

|

SU1324028A1 |

| Устройство для сортировки чисел | 1979 |

|

SU792248A1 |

| Устройство для контроля следования модулей программы | 1985 |

|

SU1249521A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1988 |

|

SU1529236A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1989 |

|

SU1702377A1 |

| Устройство для распределения заданий процессорам | 1985 |

|

SU1291983A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

Изобретение относится к автоматике и вычислительной технике и используется для контроля правильности выполнения программ в автоматизированнь:х системах управления объектами и технологическими процессами. Цель изобретения - повышение досто- .верности контроля. Цель достигается тем, что устройство содержит блок 13 памяти, три элемента задержки 2,7 и 8, элемент И 10, два регистра 9 и 11 и схемы сравнения 3 и 4, счетчик 12 адреса, триггер 5, блок 6 индикации, преобразователь 1 с соответствующими связями. Это обеспечивает разбивку программы на взаимосвязанные модули, обеспечивает автоматическое присвоение текущим адресам программы соответствующих номеров модулей и сравнение последовательности номеров модулей с хранящейся в блоке памяти. 2 ил. e сл

Фиг,1

114

Изобретение относится к автоматике и вычислительной технике и используется для контроля правильности выполнения программ в автоматизированных системах управления объектами и технологическими процессами, в станках с числовым программным управлением и других устройствах и системах с программным управлением.

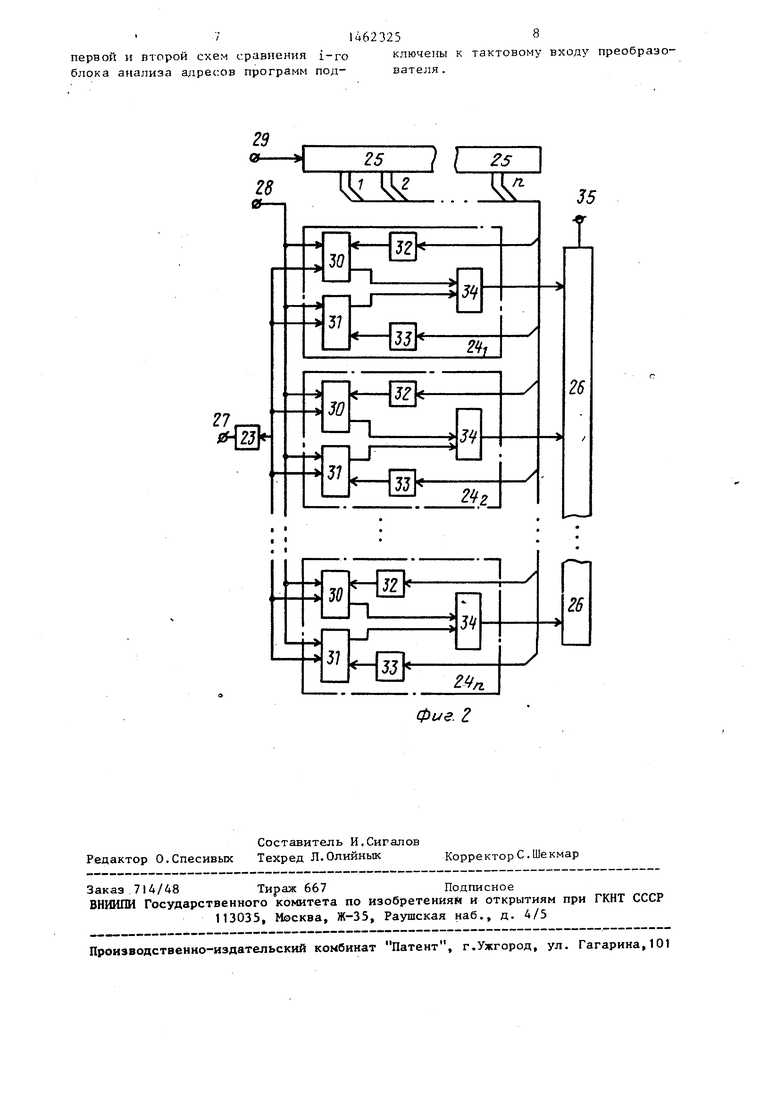

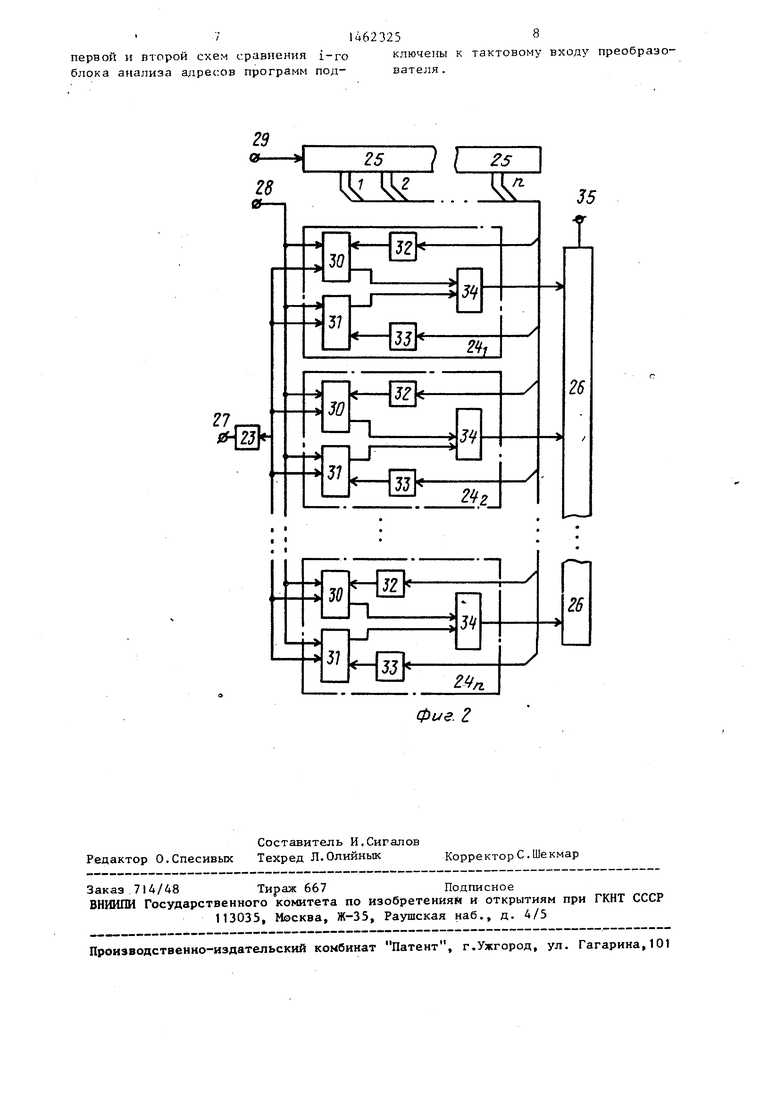

Целью изобретения является повыше : ние достоверности контроля. I На фиг.1 изображена структурная схема устройства; на фиг.2 - схема j преобразователя адреса в код номера i модуля программы.

: Устройство содержит преобразова- ; тель 1 адреса в код номера модуля : программы, первый элемент 2 задержки , первую 3 и вторую 4 схемы сравнения, i триггер 5, блок 6 индикации, второй i 7 и третий 8 элементы задержки, пер- вый регистр 9, элемент И 10, второй i регистр II, счетчик 12 адреса, блок : 13 оперативной памяти, выход блока 14 оперативной памяти, вход 15 записи, адресный вход 16, тактовый вход 17, информационный вход 18, вход 19 признака записи, вход 20 признака изменения адреса устройства, вход 21 сброса, вход 22 записи эталонной последовательности.

Преобразователь содержит регистр 23, п блоков анализа адресов программ, формирователь 25 сигналов начальной установки, шифратор 26, информационный вход 27, тактовый вход 28, вход 29 записи, схемы 30, 31 сравнения, регистры 32, 33, элемент И 34.

Устройство для контроля выполнения программы работает в следующих режимах: запись в блок 1 адресов значений нижних и верхних границ участков модулей программ; запись в блок

14 памяти последовательности номеров модулей программ контролируемого процесса.

Запись в блок I адресов значений нижних и верхних границ участков модулей программ происходит следующим образом.

На вход 16 устройства поступают адреса значений 1шжних и верхних границ участков модулей программ, которые записьшаются в соответствующие регистры 32 и 33 узлов 24 анализа диапазонов пшфратора. Этими действиями осуществляется запись верхних и

0

5

0

г

0

нижних адресов модуля программ в соответствующий узел 24 анализа диапазона изменения адресов модуля, а порядковый номер узла анализа диапазона теперь будет соответствовать номеру модуля. Адреса, поступающие на вход 27 шифратора 1 и принадлежащий одному из диапазонов адресов модуля программы,,будут зашифрованы порядковым номером узла 24 анализа,

Режим записи в блок памяти ОЗУ последовательности номеров модулей программ контролируемого процесса.

На вход 21 Сброс устройства подается сигнал, по которому производится установка в О счетчика 12 адреса и -установка триггера 5 в исходное нулевое состояние, на блоке 6 индикации индицируется нормальное функционирование устройства. Значение содержимого счетчика 12 адреса, равное нулю, поступает на адресный вход блока 14 памяти. На информацион- 5 ный вход 18 устройства подается код номера первого модуля программы выполняемого технологического процесса, выход 18 устройства является информационным входом блока 14 памяти. По сигналу Запись, поступающему с входа 19 устройства, а блоке 14 памяти запоминается номер первого модуля программы, с которого начинается выполнение контролируемого процесса. Для записи последующих номеров модулей цикл повторяется с подачи сигнала на вход 20 устройства, который соединен со счетным входом счетчика 12 адреса, и увеличивает содержимое счетчика на два, и это значение поступает на адресный вход блока 14 памяти. Количество последовательности номеров модулей программы, записываемых в блок 14 памяти, определяется циклом контролируемого процесса. По завершении записи последовательности номеров программы в блок 14 памяти подается сигнал Сброс на вход 21 устройства, который устанавливает счетчик 12 адреса в О. Значения регистров 9 и 11 равны нулю, линии сброса на.фиг.1 не показаны. С входа 8 устройства поступает первый сигнал, который разрешает прохождение информации с выхода регистра 11 через элемент И 10 на вход регистра 9, где и запоминается; сигнал, проходя через элемент 8 задержки поступает сигналом считывания в блок 14

5

0

0

5

- 1462325

памяти, а так как значение счетчика пределами значений нижних и верхних 12 адреса равно нулю, то содержимое границ адресов модулей и формируется

нулевой ячейки блока 14 памяти считывается, поступает на вход регистра I 1 и запоминается в нем. В нулевой ячейке блока 14 памяти был записан первый номер модуля программы, с которого начинается технологический процесс; первьй сигнал с входа 22 устройства, проходя через элемент 8 задержки поступает на счетный вход счетчика 12 адреса и увеличивает его содержимое на два, т.е. значение содержимого счетчика 12 адреса стало равным двум. С установочного входа 22 устройства поступает второй сигнал, который разрешает прохождение информации с выхода регистра I1 через элемент И 10 на вход регистра 9, где и запоминается, т.е. на регистре 9 записан первый номер модуля программы, с которого начинается процесс далее содержимое регистра 9 будем называть номером текущего модуля программы; сигнал, проходя через элемент 7, поступает сигналом считывания в блок 14 памяти, при этом если значение счетчика 12 адреса равно двум, то содержимое второй ячейки блока 14 памяти считьшается, поступает на вход регистра 1I и запоминается в нем. Во второй ячейке блока 14 памяти был записан второй номер модуля программы выполняемого технологического процесса, далее содержимое регистра 1I будем называть номером следующего модуля программы; сигнал с выхода элемента 7 задержки, проходя через элемент 8 задержки, поступает на счетный вход счетчика 12 адреса и увеличивает его значение на два, т.е. содержимо.е счетчика 12 адреса равно четырем.

. После выполнения подготовительных операций устройство готово к работе. Работа устройства происходит следующим образом.

В процессе выполнения программы, управляющей технологическим процессом, происходит формирование адресов программы, которые по адресному входу 16 поступают на вход 27 блока 1 и сопровождаются тактовым сигналом на входе 17 устройства, который поступает на вход 28 шифратора 1. По сигналу на входе 17 шифратор 1 осуществляет сравнение текущего адреса программы (по входу 16 устройства) с

10

позиционный код номера модуля прог- рамкы, который подается на первьш вход схемы 3 сравнения. По этому же сигналу, который поступает на управляющий вход схемы 3 сравнения, происходит сравнение значения регистра I (номера текущего модуля, записанного в блок 14 памяти) с реальным номером, который поступает из шифратора I.

В случае равенства значений кода номера выполняемого модуля, поступаю- 5 щего с блока 1 оцифровки, и кода номера текущего модуля, хранящегося в регистре 9, на втором выходе схемы 3 сравнения появляется сигнал, поступающий на триггер 5, который уста- Q навливается в нулевое состояние, и блок 6 индикации указьшает на нормальное функционирование технологического процесса.

В случае неравенства на первом 5 выходе схемы 3 сравнения появляется сигнал, которьй поступает на управляющий вход второй схемы А сравнения, На первый вход второй схемы 4 сравнения при этом поступает код номера вы- 0 полняемого модуля, поступающего с блока 1, а на второй вход второй схе- мь1 4 сравнения поступает номер сле- дугацего модуля программы, хранящегося в регистре II. В случае неравенства на втором выходе второй схемы 4 сравнения появляется сигнал, который производит установку триггера 5 в еди- ничное значение, при этом блок 6 индикации укажет на сбой в технологическом процессе.

В случае равенства на первом выходе второй схемы сравнения 4 появляется сигнал, который разрешает прохождение через элеме1 т И 10 информации с регистра И на вход регистра 9 и одновременно поступает на вход записи регистра 9, т.е. код номера следующего модуля записался в регистр I I и стал кодом номера текущего модуля; проходя через элемент 7 задержки, поступает на элемент 8 задержки, на вход Считывание блока 14 памяти и информация из блока 14 памяти поступает на вход регистра I1, на вход записи регистра II, что приводит к запоминанию на регистре I 1 нового кода номера следующего модуля; проходя через элемент 8 задержки, поступает на счетный вход счетчи5

0

5

0

5

1462325

ка 12.адреса, т.е. увеличивает значение счетчика на два - подготавливает содержимое счетчика 13 адреса к следующему изменению последовательности номеров модулей программ.

Технологический процесс представляет собой бесконечную последовательность циклов, такую последовательность невозможно разместить в блоке 14 памяти, да и нецелесообразно. Поэтому за два такта до завершения одного цикла и началом другого в предлагаемое устройство по входу 21 подается сигнал Сброс, который устанавливает счетчиц 12 адреса в О , что и является началом нового цикла.

Формула изобрет е н и я

I. Устройство для контроля последовательности выполнения модулей программ, содержащее блок оперативной памяти, три элемента задержки, элемент И, первую схему сравнения, первый и второй регистры, отличающееся тем, что, с целью повышения достоверности контроля, в устройство введены вторая схема сравнения, счетчик адреса, триггер, блок индикации и преобразователь адреса в код номера модуля программ, причем входы адреса и признака адреса устройства соединены соответственно с информационным входом и входом записи преобразователя адреса в код но- м ера модуля программ, выход которого соединен с первыми входами первой и второй схем сравнения, тактовый вход устройства соединен непосредственно с тактовым входом преобразователя адреса в код номера модуля программ и через первый элемент задержки - с входом считывания шифратора адреса и

элемента И, и через второй элемент задержки - с входом записи второго регистра, с входом признака считыв ния блока оперативной памяти, чере третий элемент задержки - со счетн входом счетчика адреса, вход начал ной установки устройства соединен входом установки начального адреса п счетчика адреса и вторым входом ус новки нуля триггера, выход которог соединен с входом блока индикации вход признака изменения адреса уст ройства соединен со счетным входом 15 счетчика адреса, выход которого со динен с адресным входом блока опер тивной памяти, выход которого соед нен с информационным входом второг регистра, информационный вход уст- 20 ройства, вход признака записи устр ства соединены . соответственно с и формационным входом и входом запис блока оперативной памяти, вход счи тывания эталонной последовательнос 25 устройства соединен с входом второ элемента задержки.

35

тактовым входом первой схемы сравне- единены соответственно с выходами

ния, выходы равенства и неравенства которой соединены соответственно с первым входом установки нуля триггера и с тактовым входом второй схемы сравнения, выход первого элемента И соединен с информационным входом первого регистра, выход которого соединен с вторым входом первой схемы сравнения, выход второго регистра соединен с первым входом элемента И и вторым входом второй схемы сравнения, выход равенства которой соединен непосредственно с признаком записи первого регистра и вторым входом

50

55

первого и второго регистров i-ro ка анализа адресов программ, инфо ционные входы регистров i-ro блок анализа адресов программ подключе к соответствующему выходу формиро теля сигналов начальной установки вход разрешения которого является входом записи преобразователя, вы ды первой и второй схем сравнения го блока анализа адресов программ соединены соответственно с первым вторым входами элемента И, выход торого подключен к соответствующе входу шифратора, входы разрешения

325

элемента И, и через второй элемент задержки - с входом записи второго регистра, с входом признака считывания блока оперативной памяти, через третий элемент задержки - со счетным входом счетчика адреса, вход начальной установки устройства соединен с входом установки начального адреса счетчика адреса и вторым входом установки нуля триггера, выход которого соединен с входом блока индикации, вход признака изменения адреса устройства соединен со счетным входом 5 счетчика адреса, выход которого соединен с адресным входом блока оперативной памяти, выход которого соединен с информационным входом второго регистра, информационный вход уст- 0 ройства, вход признака записи устройства соединены . соответственно с информационным входом и входом записи блока оперативной памяти, вход считывания эталонной последовательности 5 устройства соединен с входом второго элемента задержки.

единены соответственно с выходами

50

55

первого и второго регистров i-ro блока анализа адресов программ, информационные входы регистров i-ro блока анализа адресов программ подключены к соответствующему выходу формирователя сигналов начальной установки, вход разрешения которого является входом записи преобразователя, выходы первой и второй схем сравнения i- го блока анализа адресов программ соединены соответственно с первым и вторым входами элемента И, выход которого подключен к соответствующему входу шифратора, входы разрешения

71462325

первой н второй схем сравнения i-ro ключеиы к тактовому входу преобразо- блока анализа адресов программ под- вателя .

29

9Н 5 / / S I

г«

фие. 2

| Устройство для контроля выполненияпРОгРАММы | 1979 |

|

SU842823A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля последовательности выполнения программ | 1985 |

|

SU1254493A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-02-28—Публикация

1986-12-02—Подача