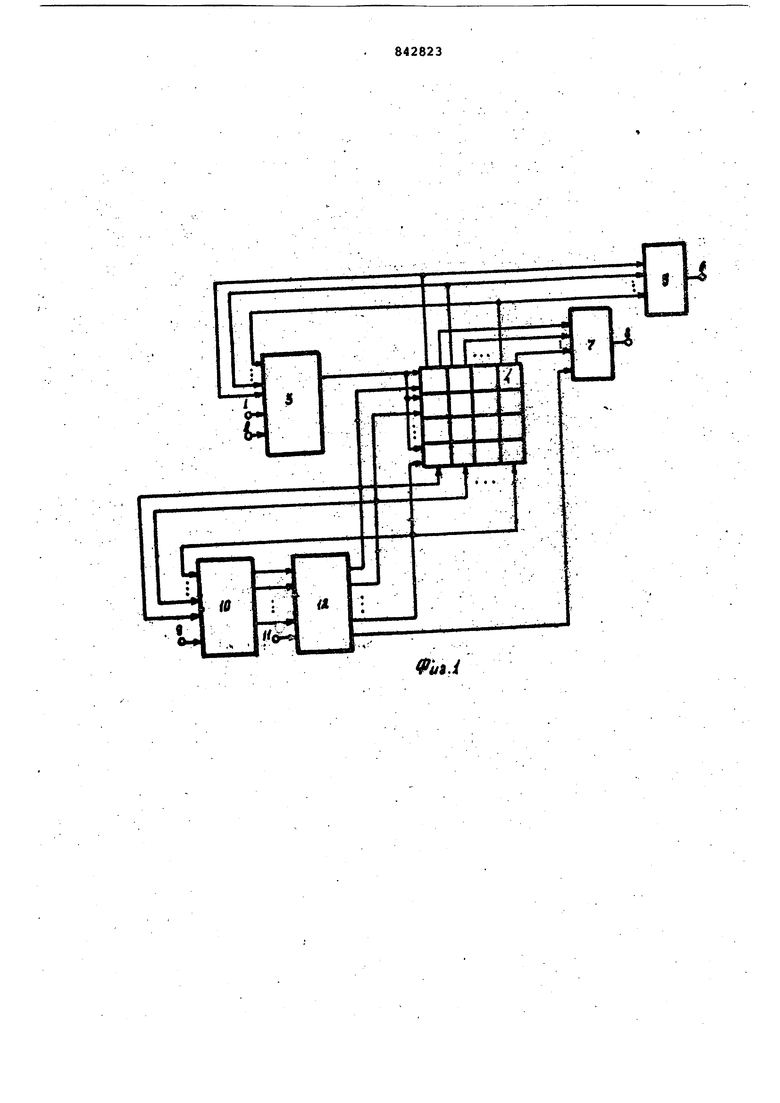

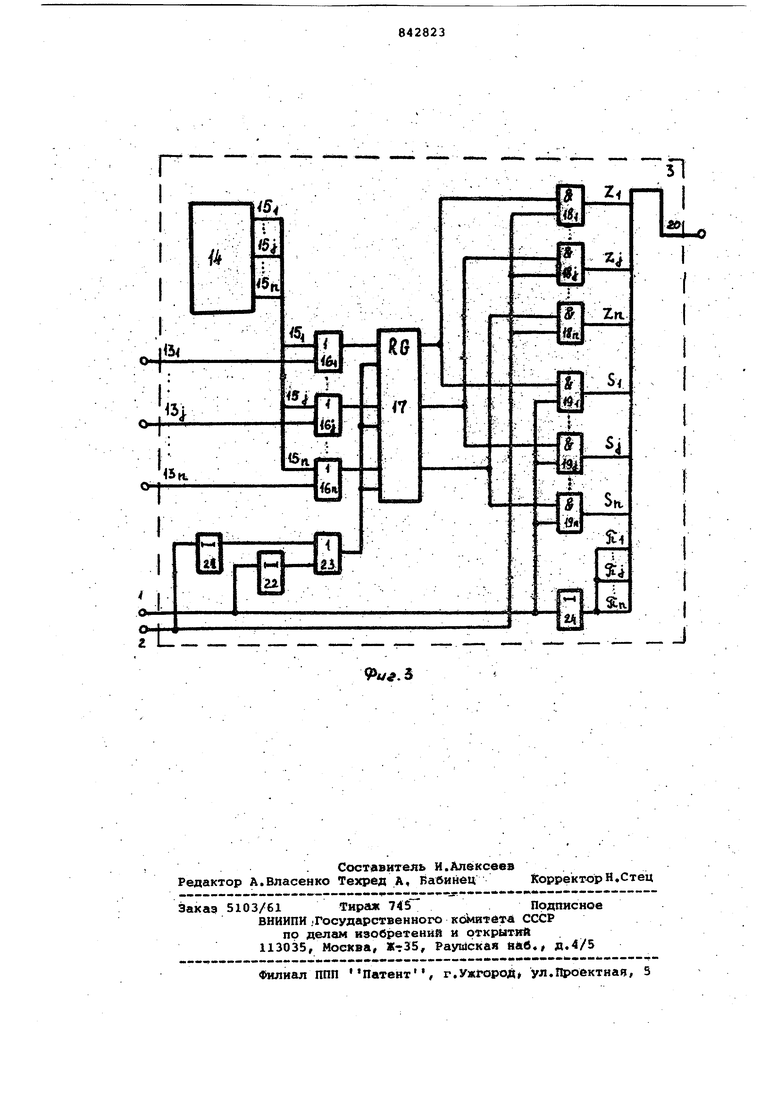

(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ВЫПОЛНЕНИЯ ПРОГРАММЫ диненас.группой входов второго эле мента ИЛИ, выход которого подключен к выходу Норма устройства, выход .Брак которого подключен к выходу первого элемента ИЛИ, допол нительно .содержит второй блок памяти признаков программы, третий элемент ИЛИ, группу элементов ИЛИ, первую и вторую, группы элементов И, первый, второй,третий элементы задержки и регистр, информационные входы которого подключены к выходам группы элементов ИЛИ, пербая группа входов которой соединена с группой выходов второго блока памят признаков программы, вторая группа входов - со второй группой выходов блока оперативной памяти, первый уп равляющий выход устройства подключе к первым входам элементов И первой группы, через первый элемент задерж к первому входу третьего элемента ИЛИ и к входу второго элемента задержки, второй управляющий вход уст ройства соединен с первыми входгили элементов И второй группы, через третий элемент задержки - со вторым входом третьего элемента ИЛИ, выход которого подключен к группе входов Сброс регистра, группа выходов которого соединена со вторыми входа ми элементов И первой и второй груп пы, выходы элементов И первой групп выхоры элементов И второй группы и выход второго элемента задержки сое динены соответственно с группами входов блока оперативной памя-ги Стирание, Запись и Опрос группа информационных выходов блока сравнения соединена с группой входо первого блока памяти признаков программы, группой входов строк и группой входов столбцов блока оперативной памяти. Сущность изобретения состоит в увеличении полноты контроля Путем обнаружения ошибочного повторного включения модулей программы. Для этого в устройстве после поступлени очередного модуля фиксируется его ном.ер (признак) и при повторном поступлении выполненного ранее модуля формируется сигнал ошибки. С этой целью группа информационных выходов блока сравнения соединена с группой входов первого блока памяти признаков программы. Это соединение позво ляет после первого прихода модуля тц записывать метку в соответствующую ячейку первого блока памяти , признаков программа и считать мог дуль п) в дальнейшем запрешеимым, т.е. не входящим в состав модулей контролируемой программы. Введение второго блока памяти признаков програм «1 позволяет храийт признаки, указывающие на последовательность выполнения модулей, и переписывать их затем в блок оперативной памяти. На фиг.1 приведено устройство, функциональная схема; на фиг.2 блок оперативной памяти, функциональная схема; на фиг.З - узел формирования управляющих сигналов, в который входит часть элементов устройства, предназиаченных для выдачи сигналов управления на блок опера тийной памяти, функциональная схема. Функциональная схема (фиг.1) устройства для контроля выполнения программы содержит управляющие входы 1 ртирания и записи 2 информации, узел 3 формирования управляющих сигналов , блок 4 оперативной памяти, второй элемент ИЛИ 5, выход б которого является выходом Норма устройства, первый элемент ИЛИ 7, выход 8 которого является выходом Брак устройства установочный вход 9, первый блок 10 памяти признаков ttporpaKnvnj, информационный вход 11 и блок 12 сравнения. На фиг.2 обозначены ячейки 4 ij j-той строки j-Toro столбца блока оперативной памяти (,njn - число модулей в программе), вход Zj Запись j-той строки, вход Sj Стй- рание j-той строки, вход J.,- Опрос j-той строки, вход M.J- выбор j-THx строки и столбца блока. На функциональной схеме узла формирования управляющих сигналов 3 (фиг.З) обозначены входы 13,.,. ........13 узла, соединенные с выходами столбцов блока 4 оперативной памяти, второй блок 14 памяти признаков программы 15,. группа элементов 16,....,16 ИЛИ; регистр 17; вторая и первая группы элементов 18 ........ 18, и 19 ... ...,19,, И соответственно; выходы 20 узла; третий и первый элементы 21 и 22 задержки третий элемент 23 ИЛИ; второй элемент 24 задержки. Узел 3 формирования управляющих игналов предназначен для формирования сигналов Запись, подаваемых а соответствующие входы строк блока 4, сигналов Опрос и сигналов Стирание, подаваемых одновремено на все входы строки блока 4. Поясним назначение элементов уз:а. 3 (фиг.2,3) . Из второго бх.:ока 14 гшгти признаков программы в Запись устройства считываются требуемые коды зависимостей модулей, которые хра нятся регистром 17. Со входов 131, .... .. .13, поступают сигнаы выголнения соответствующих модулей, KOTOpbie Через элементы ИЛИ 16 ...1бу, записываются в регистр 17 и спользуются в режиме Стирание. Элементы И la, .,18„ и и 19 ......... г19 предназначены, для орФйфованмя сигналов Запись ,Z и Стирание S . .,SH rio сигналам, поступающим на входы 2 и 1 соответственно. Элемент ИЛИ 23 и элементы 21, 22 задержки позволяют формировать сигнал сброса регистра 17 после вьщачи информации на выход 20. Элемент 24 задержки предназначен для сигналов Опрос J ,......., J через заданное время после прихода сигнала Стирание . Блок 4 оперативной памяти служит для хранения информации о зависимости модулей программы. В столбце, с оответствующему модулю т , записывают ся единицы в ячейках строк блока. соответствующих модулей m ,m,OT которых зависит m (после которых выполняется . Второй 5 и первый 7 элементы ИЛИ формируют сигналы Норма и Брак на выходах устройства 6 и 8 соответственйо. Первый блок 10 памяти признаков программы предназначен для хранения номеров модулей контролируемой программы и меток выполненных ранее модулей. Блок 12 сравнения используется для сравнения номеров модулей, пающих на вход устройства 11 и храни мых в блоке 10 с учетом значений меток повтора. Устройство функционирует в трех режимах: записи зависимостей модулей (режим ЗаписьУ, контроля правиль ности включения модуля (режим Конт роль ) и стирания зависимостей модуля после его; выполнения (режим Стирание). В режиме Запись на вход 11 блока 12 сравнения поступает номер модуля т, для которого необходимо записать зависимости,а на вход 2 сигнал управления. В результате срав нения возбуждается один из выходов блока 12 и соответствующий столбец М блока 4 оперативной памяти. Узел 3 формирования управляющих сигналов формирует сигналы Запись Z на соответствующих модулям;предшественн кам модуля т строках. В результате на пересечении возбужденных столбцов и строк записываются единицы. В режиме Контроль проверяетс принадлежность модуля выполняемой программе, правильная очередность включения модуля после модулей-предшественников, отсутствие ошибочного повторного включения модуля. Контроль принадлежности модуля выполняемой програм ле осуществляется путем сравнения блоком 12 номера модуля, поступающего на вход 11 , и номеров, хранящихся в блоке 10. При их несовпадении на выходе блока 12 сравнения возникает сигнал поступающий через элемент ИЛИ 7 на выход 8 и информируккций об ошибоч ном включении Модуля в работу. Если номер поступающего модуля совпадает с одним из номеров, хранящихся в блоке 10, возбуждается один из выходов блока 12 и соответствующий столбец блока 4.Под действием управляющих сигналов Опрос JT из узла 3 проверяется нулевое состояние ячеек-возбужденного столбца. Если в столбце отсутствуют единицы, то возбуждается выход N и через элемент ИЛИ 5 разрешается выполнение следующего модуля программы. Сигнал с выхода N поступает в узел 3 для запоминания номера модуля, включаемого в работу. Если в проверяемом столбце имеется хотя бы одна единица, возникает сигнал на выходе N, который через элемент ИЛИ 7 поступает на выход 8. Контроль ошибочного повторного включения модуля производится следующим образом. После первого включения модуля сигнал с соответствующего выхода блока 12 сравнения поступает также и в блок 10 памяти признаков программы, где он запоминается в виде метки.При повторном поступлении модуля на вход 11 на выходе несовпадения блока 12 сравнения вырабатывается сигнал ошибки. В режиме Стирание после выполнения модуляна вход 11 поступает номер этого модуля, а на вход 1 упра вляющий сигнал. В Е езультате сигналов с выхода блока 12 возбуждается одна из строк матрицы 4, в которой под- действием сигнала Стирание S с.выхода узла 3 происходит стирание единиц во всех столбцах возбужденной строки. Одновременное возбуждение j-той строки и j-Toro столбца блока 4 не / нарушает нормального функционирования устройства во всех режимах. Поскольку модуль не может зависеть сам От себя, т.е. т. f т,, то при записи зависимостей в диагональных ячейках 4зj блока 4 всегда будут записаны нули. Узел 3 формирования управляющих сигналов (фиг.З) работает следующим образом. В режиме Запись из блока 14 памяти признаков программы считываются соответствующие коды, которые через элементы ИЛИ 16 ,...,16„ записываются в регистр 17, а затем по сигналу Запись на входе 2 через элементы И 18 ,, 18 поступают на выходы 20. После считывания из регистра 17 очередного кода он обнуляется сигналом, проходящим через элемеМт 21 задержки и элемент ИЛИ 23. И режиме Контроль узел 3 формирует сигналы Опрос f... tfn йд выходах 20. Сигналы . . Опрос формируются путем задержки на эащанное время сигнала Сти рание на входе 2. Если очередной модуль т- выполнен правильно, то на соответствующий вход llj поступает сигнал, который записывается в j-THfl разряд регистра, В реж.име Стирание на вход 1 поступает управляющий сигнал 1, по которому, на 20 через элемент И 19,| выдается сигнал стирания Sv. После этого осуществляется уста 1Ювка в исходное (нулевое) бостояви регистра 17, Таким образом, предлагаемое устройство для контроля выполнения про граммы отличается от известных устройств большей полнотой контроля, поскольку позволяет контролировать шшбочное повторное включение модулей программы. Формула изобретения Устройство для контроля выполнения программы, содержащее первый бл памяти признаков программы, установочный вход которого является установочным входом устройства, а групп выходов соединена с группой входов блока сравнения, информационный вхо которого является информационным вх дом устройства, выход соединен со входом первого элемента ИЛИ, группа входов которого подключена к первой группе выходов блока оперативной па мяти, вторая группа выходов которог соединена с группой входов второго элемента ИЛИ, выход которого подклю чен к выходу Норма устройства. которого подключен к выходу первого элемента ИЛИ, отличающееся тем, что, с целью увеличения полноты контроля дополнительно содержит второй блок памяти признаков программы, третий элемент ИЛИ, группу элементов ИЛИ, первую и вторую группы элементов И, первый, второй, третий элементы задержки и регистр, информационные входы которого подключены к выходам элементов ИЛИ группы, первая группа входов которой соединена с группой выходов второго блока памяти признаков программы, вторая группа входов-. со второй группой выходов блока оперативной пёмяти, первый управляющий вход устройства подключен к первым входам элементов и первой группы,через первый элемент задержки - к первому входу третьего элемента ИЛИ и к входу, второго элемента задержки, второй управляющий вход устройства соединен с первыми входами элементов И второй группы, через третий элемент задержки - со вторым входом третьего элемента ИЛИ,.выход которого подклюСбросчен к группе входов гистра, группа выходов которого соединена со вторыми входами элементов И первой и второй группы, выходы элементов И первой группы, выходы элементов И второй группы и выход третьего элемента задержки соединены соответственно с группами входов блока оперативной памяти Стирание Запись Опрос, группа информационных выходов блока сравнения соединена с группой входов первого блока памяти признаков программы, группой входов строк и группой входов столбцов блока оперативной памяти. Источники информации, принятые во внимание при экспертизе 1.Клямко Э.И. Схемный и тестовый контроль автоматических цифровых вычислительных машин. М., Советское радио , 1963,с.87,рис.14. 2.Авторское свидетельство СССР 516040, кл. G 06 F 11/30, 1976 (прототип).

, о

.5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля последовательности выполнения программ | 1985 |

|

SU1254493A1 |

| Устройство для контроля операций над полем общих данных | 1984 |

|

SU1254490A1 |

| Устройство для контроля последовательности выполнения программ | 1988 |

|

SU1674134A1 |

| Процессорный модуль | 1985 |

|

SU1343421A1 |

| АССОЦИАТИВНЫЙ ПРОЦЕССОР | 1988 |

|

SU1521118A1 |

| УСТРОЙСТВО СБОРА И РЕГИСТРАЦИИ ПОЛЕТНОЙ ИНФОРМАЦИИ | 1990 |

|

SU1825189A1 |

| Устройство для фиксации трассы выполнения программы | 1983 |

|

SU1136170A1 |

| Устройство формирования маршрута сообщения в однородной вычислительной системе | 1985 |

|

SU1287172A1 |

| Сигнатурный анализатор | 1983 |

|

SU1140123A1 |

| Распределенная система для программного управления технологическими процессами | 1990 |

|

SU1797096A1 |

Авторы

Даты

1981-06-30—Публикация

1979-08-01—Подача