Изобретение относится к вычислительной технике и может быть использовано при отладке программ в вычислительных комплекса,, а также для контроля и трассировки программ

Цель изобретения - сокращение - времени отладки программы.

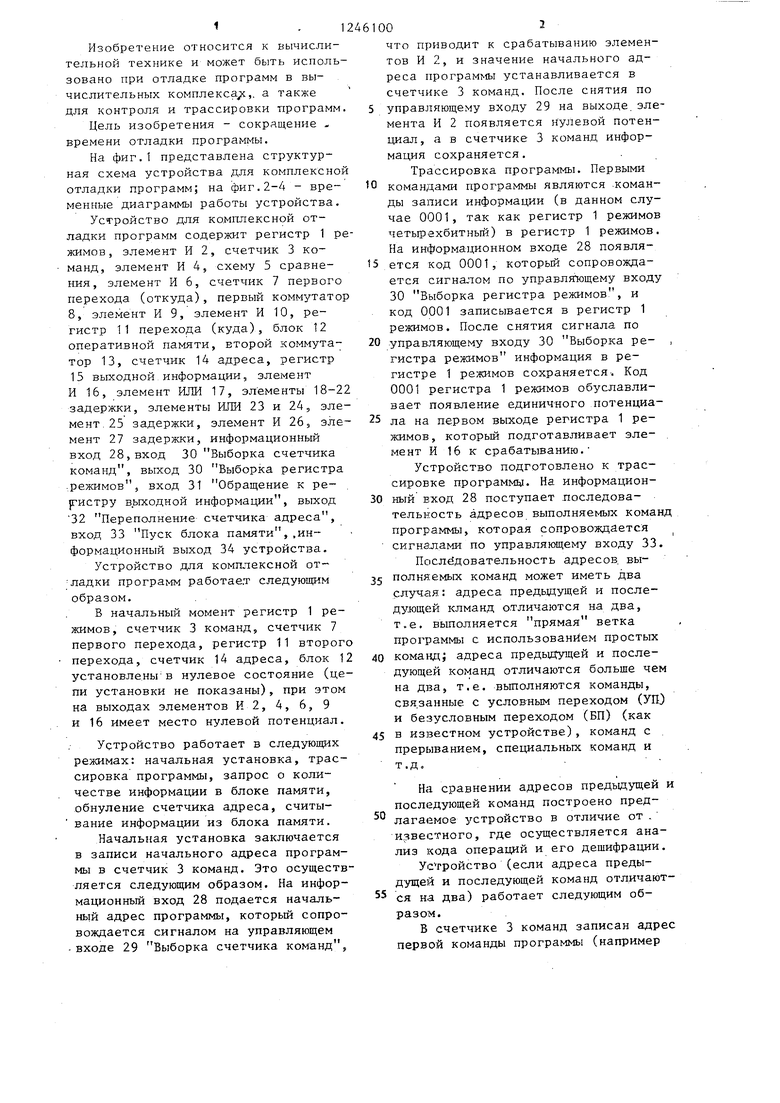

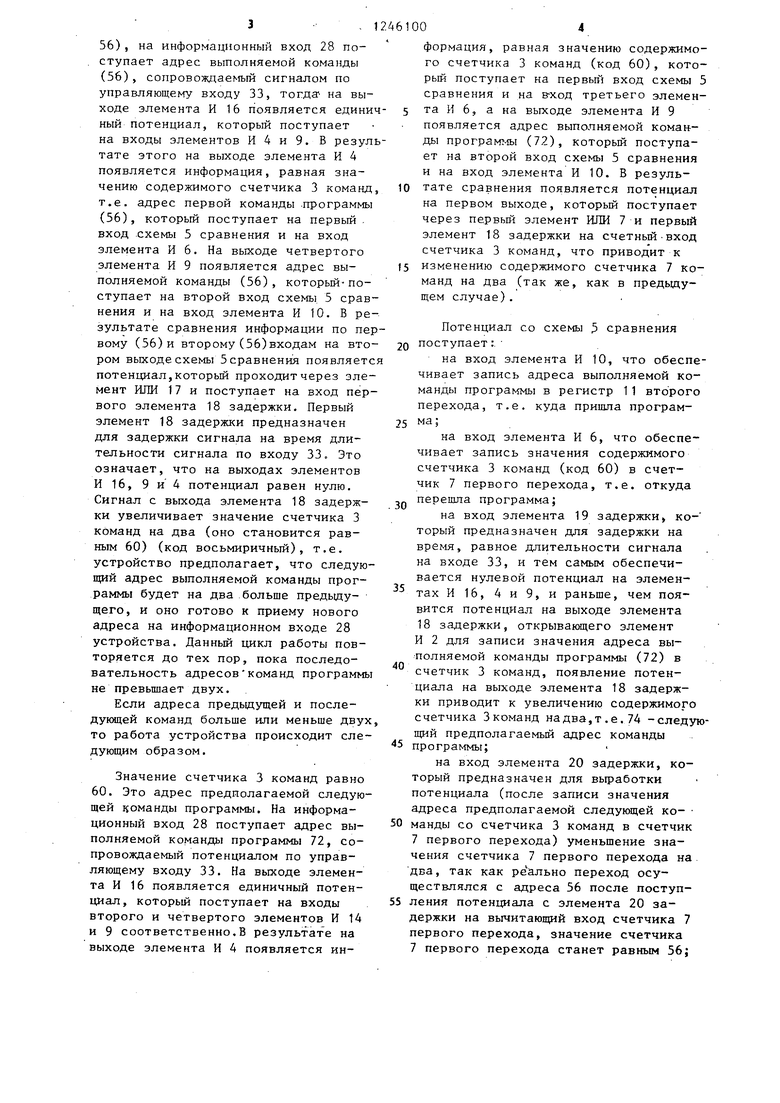

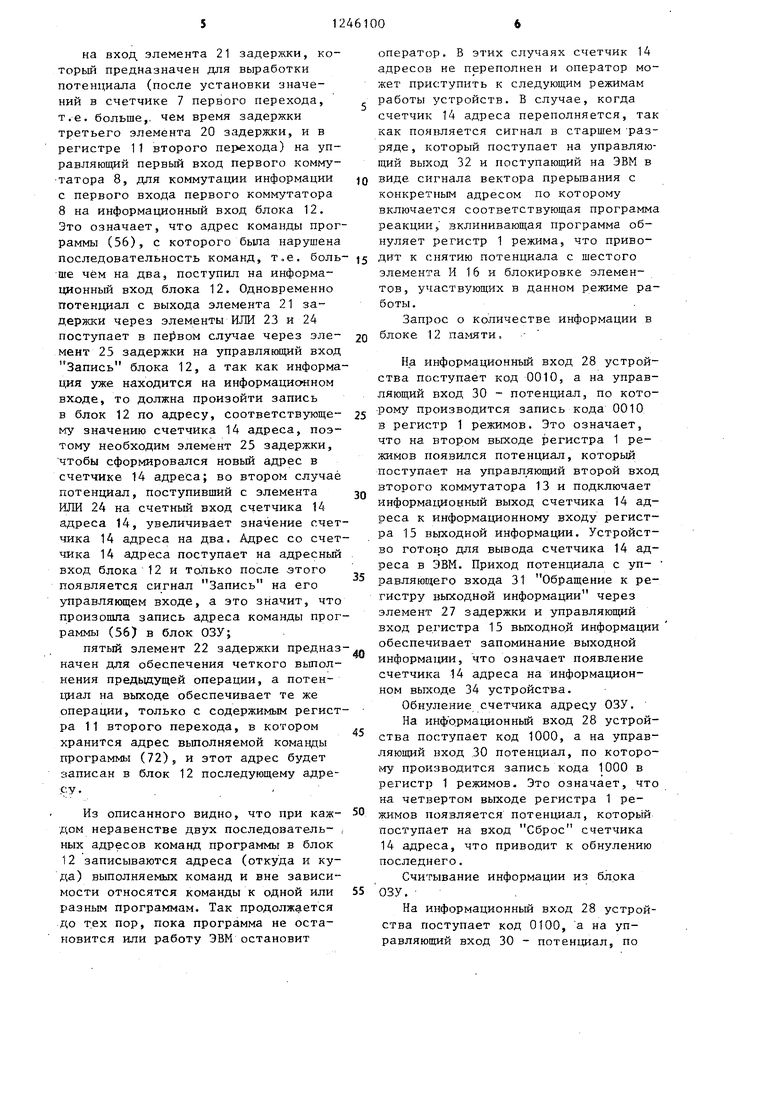

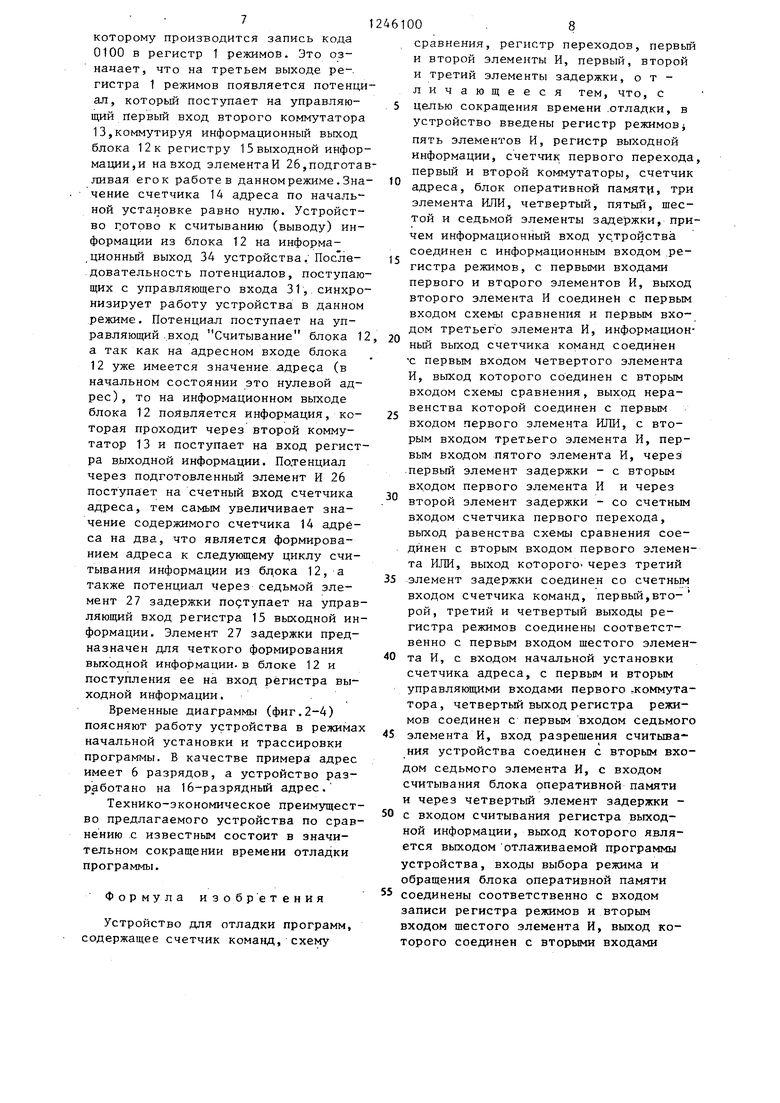

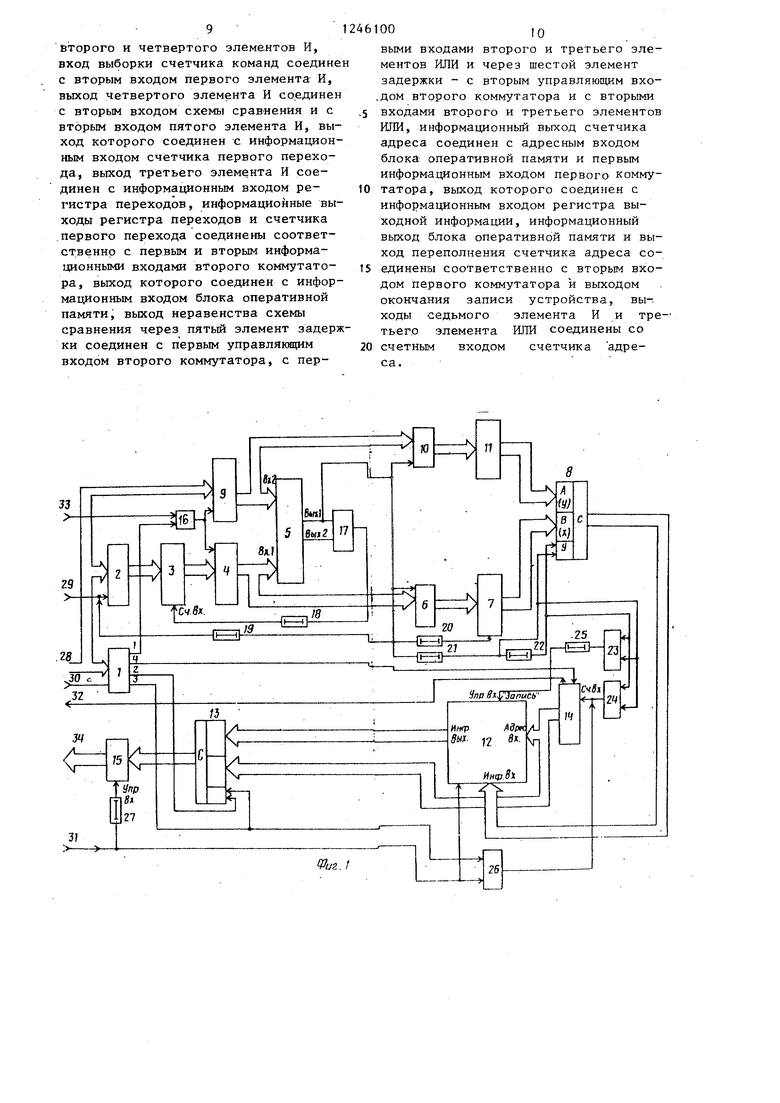

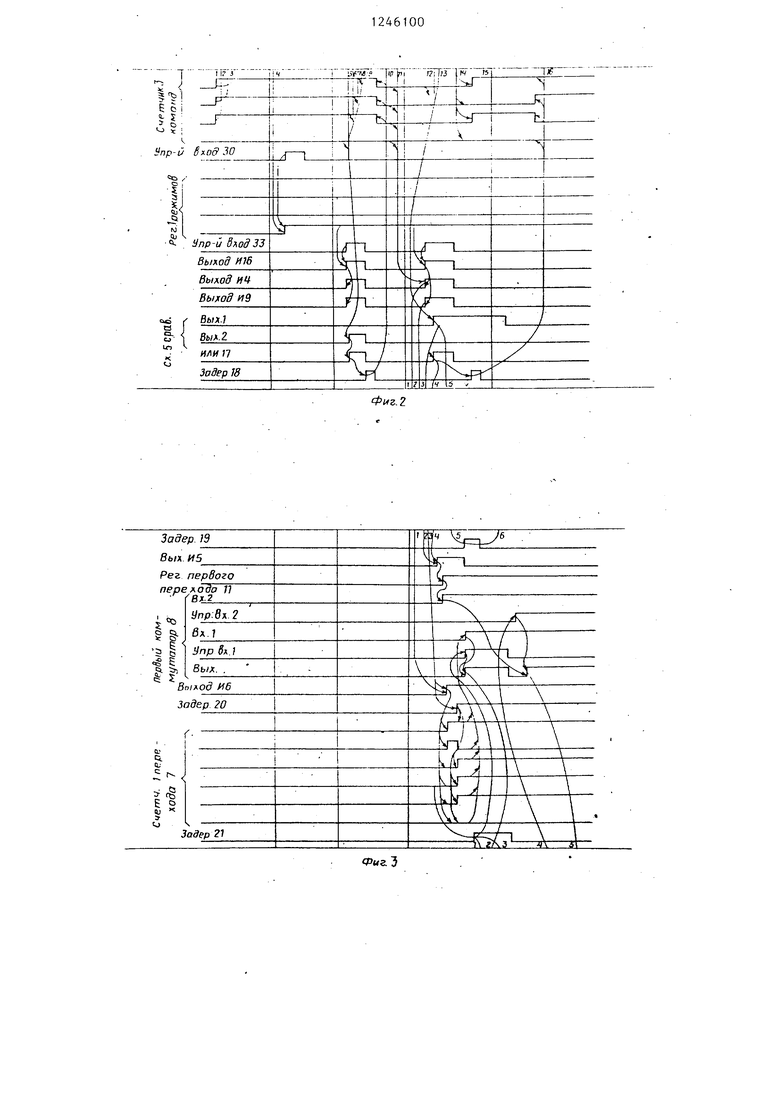

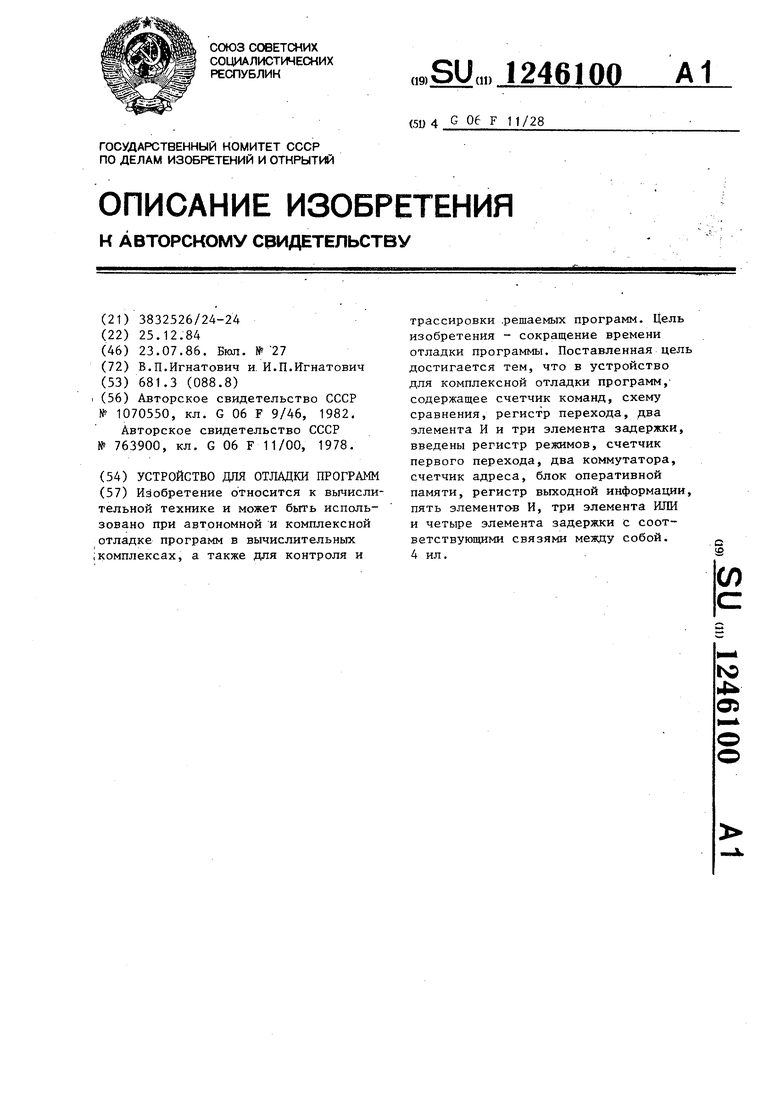

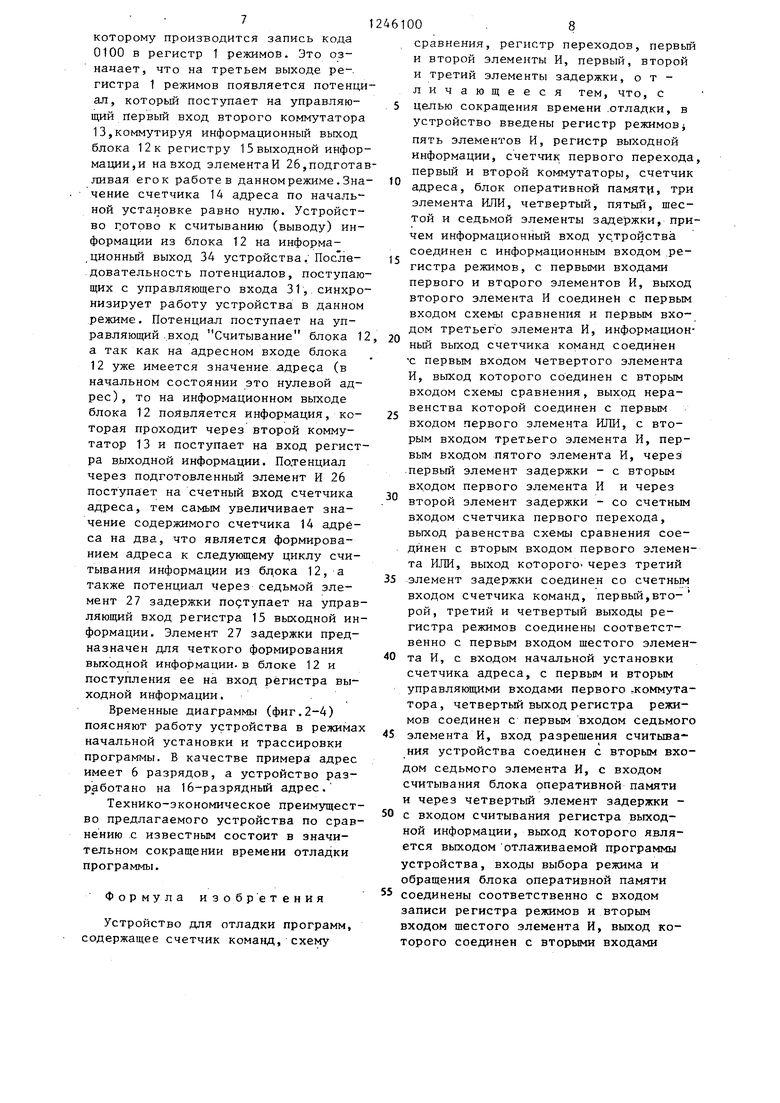

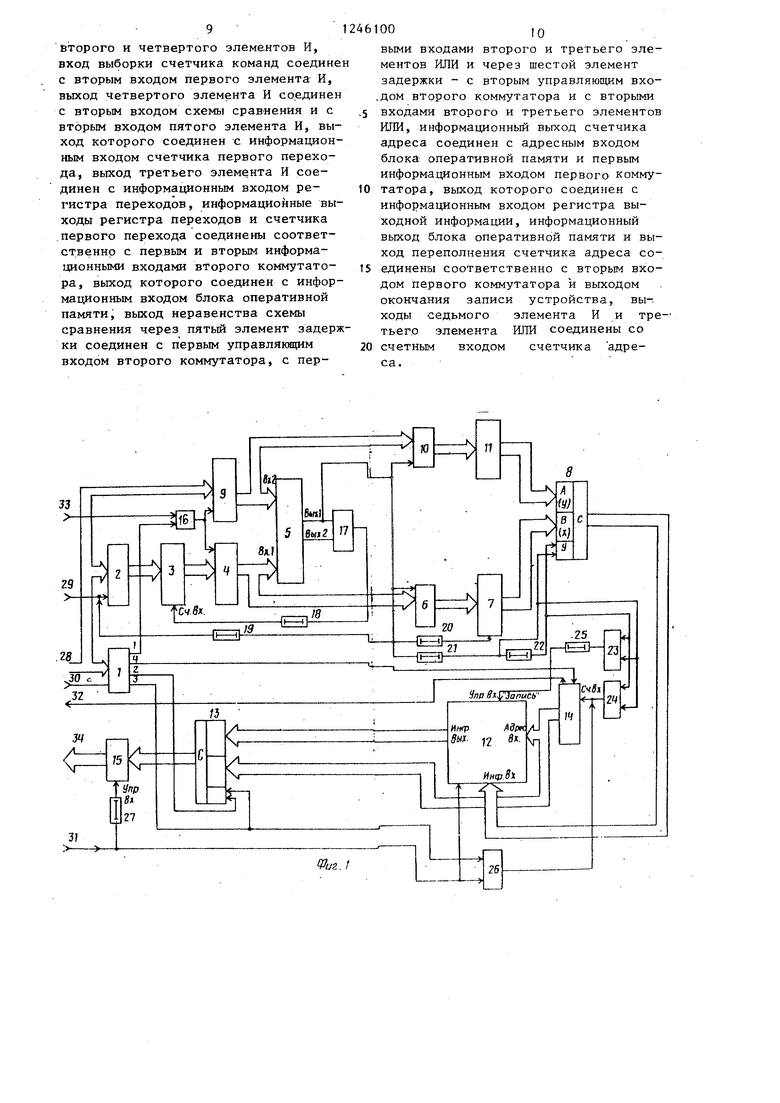

На фиг.1 представлена структурная схема устройства для комплексной отладки программ; на фиг.2-А - временные диаграммы работы устройства.

Устройство для комплексной отладки программ содержит регистр 1 режимов, элемент И 2, счетчик 3 команд, элемент И 4, схему 5 сравнения, элемент И 6, счетчик 7 первого перехода (откуда), первый коммутатор 8, элемент И 9, элемент И 10, регистр 11 перехода (куда), блок 12 оперативной памяти, второй коммутатор 13, счетчик 14 адреса, регистр 15 выходной информации, элемент И 16, элемент ИЛИ 17, элементы 18-22 задержки, элементы ИЛИ 23 и 24, элемент. 25 задержки, элемент И 265 элемент 27 задержки, информационный вход 28,вход 30 Выборка счетчика команд, выход 30 Выборка регистра -.режимов, вход 31 Обращение к ре- {гистру в.ыходной информации, выход 32 Переполнение счетчика адреса, вход 33 Пуск блока памяти,.информационный выход 34 устройства.

Устройство для комплексной от- ;ладки программ работае.т следующим образом.

В начальный момент регистр 1 режимов, счетчик 3 команд, счетчик 7 первого перехода, регистр 11 второго перехода, счетчик 14 адреса, блок 12 установле.ны в нулевое состояние (цепи установки не показаны), при этом на выходах элементов И 2, 4, 6, 9 и 16 имеет место нулевой потенциал.

Устройство работает в следующих режимах: начальная установка, трассировка программы, запрос о количестве информации в блоке памяти, обнуление счетчика адреса, считывание информации из блока памяти.

Начальная установка заключается в записи начального адреса программы в счетчик 3 команд. Это осуществляется следующим образом. На информационный вход 28 подается началь- нь1й адрес программы, который сопровождается сигналом на управляющем -входе 29 Выборка счетчика команд.

что приводит к срабатыванию элементов И 2, и значение начального адреса программы устанавливается в счетчике 3 команд. После снятия по

управляющему входу 29 на выходе, элемента И 2 появляется нулевой потенциал, а в счетчике 3 команд информация сохраняется.

Трассировка программы. Первыми

командами программы являются .команды записи информации (в данном случае 0001, так как регистр 1 режимов четырехбитньш) в регистр 1 режимов. На информационном входе 28 появляется код 0001, которьш сопровождается сигналом по управляющему входу 30 Выборка регистра режимов, и код 0001 записывается в регистр 1 режимов. После снятия сигнала по

.управляющем.у входу 30 Выборка ре- , гистра режимов информация в регистре 1 режимов сохраняется-. Код 0001 регистра 1 режимов обуславливает появление единичного потенциала на первом выходе регистра 1 режимов, который подготавливает эле- . мент И 16 к срабатыванию.

Устройство подготовлено к трассировке программы. На информационный вход 28 поступает .последовательность адресов выполняемых команд пpoгpaм ы, которая сопровождается сигналами по управляющему входу 33. Последовательность адресов, выполняемых команд может иметь два случая: адреса предьщущей и после- ду-ющей клманд отличаются на два, т.е. выполняется прямая ветка программы с использованием простьпс

команд; адреса предыДу1цей и последующей команд отличаются больше чем на два, т.е. вьшолняются команды, свя.занные с условным переходом (УП) и безусловным перех.одом (БП) (как

в известном устройстве), команд с .

прерыванием, специальных команд и т.д.

На сравнении адресов предыдущей и последующей команд построено предагаемое з стройство в отличие от . азвестного, где осуществляется анализ кода операций и его дешифрации.

Ус гройство (если адреса преды- д-ущей и последующей команд отл.ичают- ся на два) работает следующим образом.

В счетчике 3 команд записан адрес первой команды программы (например

56), на информационный вход 28 поступает адрес выполняемой команды (56), сопровождаемый сигналом по управляющему входу 33, тогда на выходе элемента И 16 появляется едининый потенциал, который поступает на входы элементов И 4 и 9. В резултате этого на выходе элемента И 4 появляется информация, равная значению содержимого счетчика 3 команд т.е. адрес первой команды .программы (56), который поступает на первый . вход -схемы 5 сравнения и на вход элемента И 6, На выходе четвертого элемента И 9 появляется адрес выполняемой команды (56), который-поступает на второй вход схемы 5 сравнения и на вход элемента И 10. В результате сравнения информации по певому (56)и второму(56)входам на втором выходе схемы 5 сравнения появляетс потенциал,который проходит через элемент ИЛИ 17 и поступает на вход первого элемента 18 задержки. Первый элемент 18 задержки предназначен для задержки сигнала на время длительности сигнала по входу 33. Это означает, что на выходах элементов И 16, 9 и 4 потенциал равен нулю. Сигнал с выхода элемента 18 задержки увеличивает значение счетчика 3 команд на два (оно становится равным 60) (код восьмиричный), т.е. устройство предполагает, что следующий адрес выполняемой команды программы будет на два больше предыдущего, и оно готово к приему нового адреса на информационном входе 28 устройства. Данный цикл работы повторяется до тех пор, пока последовательность адресов команд программы не превьппает двух.

Если адреса предыдущей и последующей команд больше или меньше двух то работа устройства происходит следующим образом.

Значение счетчика 3 команд равно 60. Это адрес предполагаемой следующей команды программы. На информационный вход 28 поступает адрес выполняемой команды программы 72, сопровождаемый потенциалом по управляющему входу 33. На выходе элемента И 16 появляется единичный потенциал, который поступает на входы второго и четвертого элементов И 14 и 9 соответственно.В результате на выходе элемента И 4 появляется ин

формация, равная значению содержимого счетчика 3 команд (код 60), который поступает на первый вход схемы 5 сравнения и на в-ход третьего элемента И 6, а на выходе элемента И 9 появляется адрес выполняемой команды програм -1ы (72), которьй поступает на второй вход схемы 5 сравнения и на вход элемента И 10. В результате сравнения появляется потенциал на первом выходе, который поступает через первый элемент ИЛИ 7 и первый элемент 18 задержки на счетный-вход счетчика 3 команд, что приводит к изменению содержимого счетчика 7 команд на два (так же, как в предьвду- щем случае).

Потенциал со схемы 5 сравнения поступает:

на вход элемента И 10, что обеспечивает запись адреса выполняемой команды программы в регистр 11 второго перехода, т.е. куда пришла программ ;

на вход элемента И 6, что обеспечивает запись значения содержимого счетчика 3 команд (код 60) в счетчик 7 первого перехода, т.е. откуда перешла программа;

на вход элемента 19 задержки ко- торый предназначен для задержки на время, равное длительности сигнала на входе 33, и тем самым обеспечивается нулевой потенциал на элементах И 16, 4 и 9, и раньше, чем появится потенциал на выходе элемента 18 задержки, открывающего элемент И 2 для записи значения адреса выполняемой команды программы (72) в счетчик 3 команд, появление потенциала на выходе элемента 18 задержки приводит к увеличению содержимого счетчика 3 команд надва,т.е.74 -следующий предполагаемый адрес команды программы;

на вход элемента 20 задержки, который предназначен для выработки потенциала (после записи значения адреса предполагаемой следующей ко-

манды со счетчика 3 команд в счетчик 7 первого перехода) уменьшение значения счетчика 7 первого перехода на два, так как ре ально переход осуществлялся с адреса 56 после поступления потенциала с элемента 20 задержки на вычитающий вход счетчика 7 первого перехода, значение счетчика 7 первого перехода станет равным 56;

на вход, элемента 21 задержки, который предназначен для выработки потенциала (после установки значений в счетчике 7 первого перехода, т.е. больше,, чем время задержки третьего элемента 20 задержки, и в регистре 11 второго перехода) на управляющий первый вход первого комму- -татора 8, для коммутации информации с первого входа первого комментатора 8 на информационный вход блока 12, Это означает, что адрес команды программы (56), с которого была нарушена последовательность команд, т.е. боль ше чём на два, поступил на информационный вход блока 12. Одновременно потенциал с выхода элемента 21 задержки через элементы ИЛИ 23 и 24 поступает в neiiBOM случае через эле- мент 25 задержки на управляющий вход Запись блока 12, а так как информация уже находится на информационном входе, то должна произойти запись в блок 12 по адресу, соответствующе- му значению счетчика 14 адреса, поэтому необходим элемент 25 задержки, чтобы сформировался новый адрес в счетчике 14 адреса; во втором случае потенциал, поступивший с элемента ИЛИ 24 на счетный вход счетчика 14 адреса 14, увеличивает значение счетчика 14 адреса на два. Адрес со счетчика 14 адреса поступает на адресный вход блока 12 и только после этого появляется сигнал Запись на его управляимцем входе, а это значит, что произошла запись адреса команды программы (56) в блок ОЗУ;

пятый элемент 22 задержки предназначен для обеспечения четкого выполнения предыдущей операции, а потенциал на выходе обеспечивает те же операции, только с содержимым регистра 11 второго перехода, в котором хранится адрес выполняемой команды программы (72), и этот адрес будет записан в блок 12 последующему адре- су, ..

Из описанного видно, что при каж- дом неравенстве двух последователь- ных адресов команд программы в блок 12 записываются адреса (откуда и куда) выполняемых команд и вне зависимости относятся команды к одной или разным программам. Так продолжается до тех пор, пока программа не остановится или работу ЭВМ остановит

Q 5 20 5 о

0 5

5

0

5

оператор. В этих случаях счетчик 14 адресов не переполнен и оператор может приступить к следующим режимам работы устройств. В случае, когда счетчик 14 адреса переполняется, так как появляется сигнал в старшем разряде, который поступает на управляющий выход 32 и поступающий на ЭВМ в виде сигнала вектора прерьшания с конкретньот адресом по которому включается соответствующая программа реакции, вкхшнивающая программа обнуляет регистр 1 режима, что приводит к снятию потенциала с шестого элемента И 16 и блокировке элементов , участвующих в данном режиме работы.

Запрос о Количестве информации в блоке 12 памяти,

На информационный вход 28 устройства поступает код 0010, а на управляющий вход 30 - потенциал, по которому производится запись кода 0010 в регистр 1 режимов. Это означает, что на втором выходе регистра 1 режимов появился потенциал, который поступает на управляющий второй вход второго коммутатора 13 и подключает информадаонный выход счетчика 14 адреса к информационному входу регистра 15 выходной информации. Устройство готово для вывода счетчика 14 адреса в ЭВМ. Приход потенциала с уп- равляюс1его входа 31 Обращение к регистру выходной информации через элемент 27 задержки и управляющий вход регистра 15 выходной информации обеспечивает запоминание выходной информазщи, что означает появление счетчика 14 адреса на информационном вьпсоде 34 устройства.

Обнуление счетчика адресу ОЗУ.

На информационный вход 28 устройства поступает код 1000, а на управ- ляюшд й вход 30 потенциал, по которо- 1чу производится запись кода 1000 в регистр 1 режимов. Это означает, что на четвертом выходе регистра 1 режимов появляется потенциал, который поступает на вход Сброс счетчика 14 адреса, что приводит к обнулению последнего.

Считывание информации из блока

ОЗУ.

На информационный вход 28 устройства поступает код 0100, а на управляющий вход 30 - потенциал, по

7

которому производится запись кода 0100 в регистр 1 режимов. Это означает, что на третьем выходе ре-, гистра 1 режимов появляется потенциал, который поступает на управляющий первый вход второго коммутатора 13,коммутируя информационный выход блока 12 к регистру 15 выходной информации, и на вход элементам 26,подготаливая его к работе в данномрежиме.Значение счетчика 14 адреса по начальной установке равно нулю. Устройство готово к считыванию (выводу) информации из блока 12 на информа- ,ционньй выход 34 устройства.; Последовательность потенциалов, поступающих с управляющего входа 31, синхронизирует работу устройства в данном режиме. Потенциал поступает на управляющий .вход Считывание блока 1 а так как на адресном входе блока 12 уже имеется значение адреса (в начальном состоянии это нулевой адрес) , то на информационном выходе блока 12 появляется информация, которая проходит через второй коммутатор 13 и поступает на вход регистра выходной информации. По.тенциал через подготовлеиньш элемент И 26 поступает на счетный вход счетчика адреса, тем самым увеличивает значение содержимого счетчика 14 адреса на два, что является формированием адреса к следующему циклу считывания информации из бдока 12, а также потенциал через седьмой элемент 27 задержки по(;:тупает на управляющий вход регистра 15 выходной информации. Элемент 27 задержки предназначен для четкого формирования выходной информации, в блоке 12 и поступления ее на вход регистра выходной информации.

Временные диаграммы (фиг.2-4) поясняют работу устройства в режимах начальной установки и трассировки программы. В качестве примера адрес имеет 6 разрядов, а устройство разработано на 16-разрядный адрес.

Технико-экономическое преимущество предлагаемого устройства по сравнению с известным состоит в значительном сокращении времени отладки программы.

Формула изобр е тения

Устройство для отладки программ, содержащее счетчик команд, схему

10

15

20

25

46100 . 8

сравнения, регистр переходов, первый и второй элементы И, первый, второй и третий элементы задержки, отличающееся тем, что, с 5 целью сокращения времени .отладки, в устройство введены регистр режимовj пять элементов И, регистр выходной информации, счетчик первого перехода, первый и второй коммутаторы, счетчик адреса, блок оперативной памят 1, три элемента ИЛИ, четвертый, пятый, шестой и седьмой элементы задержки, причем информационный вход устройства соединен с информационным входом .регистра режимов, с первыми входами первого и второго элементов И, выход второго элемента И соединен с первым входом схемы сравнения и первым входом третьего элемента И, информационный выход счетчика команд соединен с первым входом четвертого элемента И, выход которого соединен с вторым входом схемы сравнения, выход неравенства которой соединен с первым входом первого элемента ИЛИ, с вторым входом третьего элемента И, первым входом пятого элемента И, через .первый элемент задержки - с вторым входом первого элемента И и через второй элемент задержки - со счетным входом счетчика первого перехода, выход равенства схемы сравнения сое- динен с вторым входом первого элемента ИЛИ, выход которого- через третий 35 элемент задержки соединен со счетным входом счетчика команд, первый,вто- рой, третий и четвертый выходы регистра режимов соединены соответственно с первым входом шестого элемен- 40 та И, с входом начальной установки счетчика адреса, с первым и вторым управляющими входами первого -коммутатора, четвертый выход регистра режимов соединен с первым входом седьмого 45 элемента И, вход разрешения считывз ния устройства соединен с вторым входом седьмого элемента И, с входом считывания блока оперативной памяти и через четвертый элемент задержки - 50 с входом считывания регистра выходной информации, выход которого является выходом отлаживаемой программы устройства, входы выбора режима и обращения блока оперативной памяти 55 соединены соответственно с входом записи регистра режимов и вторым входом шестого элемента И, выход которого соединен с вторыми входами

30

9

Второго и четвертого элементов И, вход выборки счетчика команд соедине с вторым входом первого элемента И, выход четвертого элемента И соединен с вторым входом схемы сравнения и с вторым входом пятого элемента И, выход которого соединен с информационным входом счетчика первого перехода, выход третьего элеме.нта И соединен с информационным входом ре- гистра переходов, информационные выходы регистра переходов и счетчика первого перехода соединены соответственно с первым и вторым информационными входами второго коммутато- pa, выход которого соединен с информационным входом блока оперативной памяти, выход неравенства схемы сравнения через пятьй элемент задержки соединен с первым управляющим входом второго коммутатора, с пер

10

вьши входами второго и третьего элементов ИЛИ и через шестой элемент задержки - с вторым управляющим вхо- .дом второго коммутатора и с вторыми входами второго и третьего элементов ИЛИ, информационный выход счетчика адреса соединен с адресным входом блока оперативной памяти и первым информационным входом первого коммутатора, выход которого соединен с информационным входом регистра выходной информации, информационный выход блока оперативной памяти и выход переполнения счетчика адреса соединены соответственно с вторым входом первого коммутатора и выходом окончания записи устройства, вы-, ходы седьмого элемента И и третьего элемента ИЛИ соединены со счетныу входом счетчика адреса.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля последовательности выполнения модулей программ | 1986 |

|

SU1462325A1 |

| Устройство для отладки программ | 1984 |

|

SU1166122A1 |

| Устройство для отладки программ | 1988 |

|

SU1583744A1 |

| Устройство для отладки программно-аппаратных блоков | 1987 |

|

SU1497617A1 |

| Устройство для отладки программ | 1983 |

|

SU1104521A1 |

| Устройство для отладки программ | 1984 |

|

SU1238086A1 |

| Устройство для отладки программ | 1982 |

|

SU1049914A1 |

| Устройство для коррекции программ | 1982 |

|

SU1092514A1 |

| Имитатор абонентов | 1986 |

|

SU1325490A2 |

| Устройство для отладки программ | 1986 |

|

SU1363221A1 |

Изобретение относится к вычислительной технике и может быть использовано при автономной и комплексной отладке программ в вычислительных ;комплексах, а также для контроля и трассировки .решаемых программ. Цель изобретения - сокращение времени отладки программы. Поставленная цель достигается тем, что в устройство для комплексной отладки программ,- содержащее счетчик команд, схему сравнения, регистр перехода, два элемента И и три элемента задержки, введены регистр режимов, счетчик первого перехода, два коммутатора, счетчик адреса, блок оперативной памяти, регистр выходной информации, пять злементо-в И, три элемента ИЛИ и четыре элемента задержки с соответствующими связями между собой. 4 ил. . о (С (Л ьс 4 О)

Задер. J9 бь/л. И5

Рег первого

пере дода П

Вл2

Х°ь §|1

I Г

Упр,8д.2

бд.7

пр 8х.1

Вых.

ВтАод Иб

Задер 20

о. 15. Ч;

Г

1|

(J к

Задер 21

Задер. 22 Выход НЛИ2д Выход или 24

Задер. 25 - Счетчик адреса ОЗУ /V Запись ОЗУ - Мнформ.Вк, - ОЗИ

Ф(г.

Редактор Н.Тупица

Составитель И.Сигалов

Техред Н.Бонкало Корректор С, Шекмар

4002/42

Тираж 671 Подписное ВНИИПИ Государственного ко1 1итета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие,, г.Ужгород, ул.Проектная, 4

| Устройство для прерывания программ | 1982 |

|

SU1070550A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для отладки программ | 1978 |

|

SU763900A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-07-23—Публикация

1984-12-25—Подача