Изобретение относится к вычисли- тельной технике и может быть использовано в автоматизированных системах идентификации информации, работающих в реальном масштабе времени и является усовершенствованием устройства по авт. св. № 928358.

Цель изобретения - повьшение быстродействия ,

На чертеже представлена структурная схема предлагаемого устройства.

Предлагаемое устройство содержит входной регистр 1, коммутаторы ,

10

18 - в единичном состоянии. На вход 21 устройства подается код номера информации (объекта, состоящий из К одов знаков (рангов). Сигнал начала формирования адреса подается на вход 19 устройства и устанавливает триггер 5 в единичное состояние, разрешая тем самым прохождение синхроимпульсов с входа 20 устройства через элемент И 6 на счетный вход счетчика 7. Первьш синхроимпульс, прошедший через элемент И 6, изменит содержимое счетчика 7 и вызовет появление на первом выходе дешифратора 8 сигнала, по которому

дешифраторы 3 -t., кода адреса, сумматор 4, триггер 5, элемент И 6, счет-15 триггер 18 перейдет в нулевое состоя- чик 7, дешифратор 8, мультиплексор 9, регистры , элементы Задержки, элемент ИЛИ 12, элемент И 13, регистр 14, схемы сравнения, шифратор 16, триггеры 17 и 18, 20 входы 19-21, выход 22, элемент 23 задержки,

Предлагаемое устройство работает следующим образом.

После включения триггер 5, счетчик 25

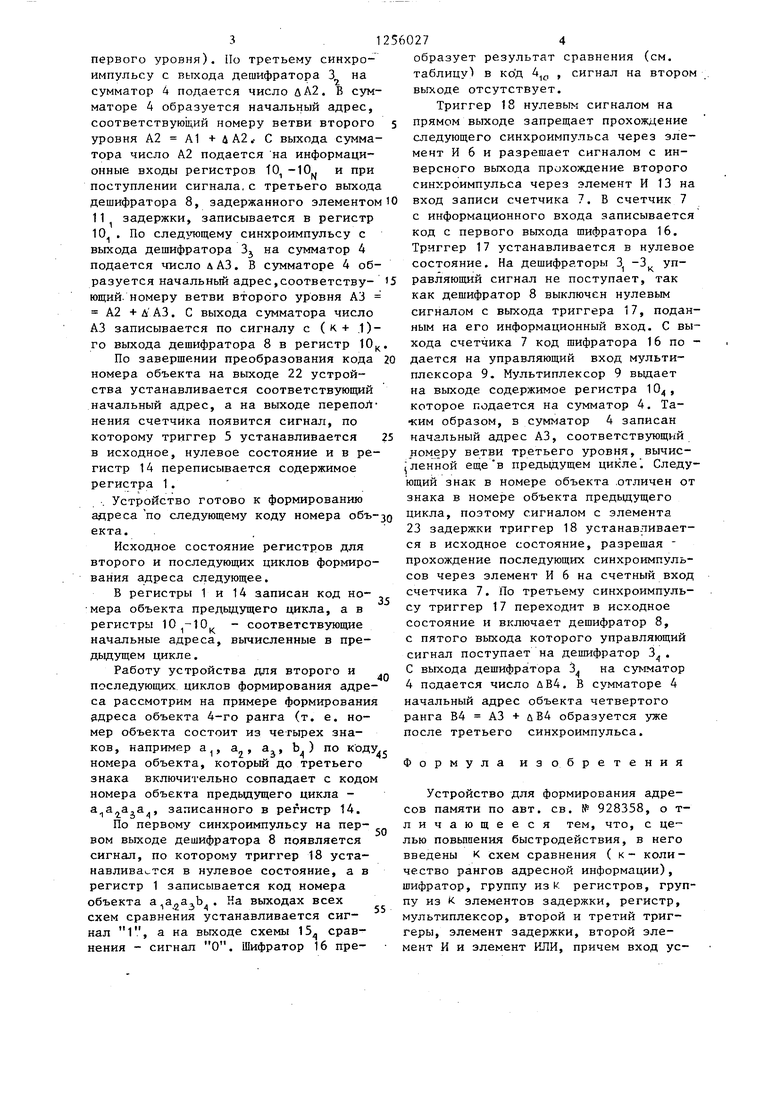

ние, а в регистр 1 запишется код номера объекта. За время до следующего синхроимпульса сх емы 15,-15 сравнения сравнивают коды знаков, входящих в номер объекта, регистров 1 и 14. Результат сравнения шифратор 16 преобразует в код на первом выходе и i сигнал на втором выходе в соответствии с таблицей, где О - коды i-ro

знака не совпали, 1 - коды j-ro знака

Так как записанный в регистр 1 код номера объекта не равен нулю, а регистр 14 обнулен, то на выходах схем 15.-15ц сравнения устанавливается нулевой сигнал. Шифратор 16 преобразует результат сравнения в сигнал на втором выходе, который сбрасывает триггер 18 через элемент ИЛИ 12 в исходное состояние, разрешая прохождение следующего синхроимпульса через элемент И 6.

18 - в единичном состоянии. На вход 21 устройства подается код номера инормации (объекта, состоящий из К одов знаков (рангов). Сигнал начала формирования адреса подается на вход 19 устройства и устанавливает триггер 5 в единичное состояние, разрешая тем самым прохождение синхроимпульсов с входа 20 устройства через элемент И 6 на счетный вход счетчика 7. Первьш синхроимпульс, прошедший через элемент И 6, изменит содержимое счетчика 7 и вызовет появление на первом выходе дешифратора 8 сигнала, по которому

триггер 18 перейдет в нулевое состоя-

триггер 18 перейдет в нулевое состоя-

ние, а в регистр 1 запишется код номера объекта. За время до следующего синхроимпульса сх емы 15,-15 сравнения сравнивают коды знаков, входящих в номер объекта, регистров 1 и 14. Результат сравнения шифратор 16 преобразует в код на первом выходе и i сигнал на втором выходе в соответствии с таблицей, где О - коды i-ro

знака не совпали, 1 - коды j-ro знака

Второй синхроимпульс вызовет появ- ление управляющего сигнала на втором выходе дешифратора 8. На коммутаторы и дешифраторы З.-З., подаются коды знаков (номеров ветвей). При этом с выходов коммутаторов 2 -2 на дешифраторы 3 -З подаются сигналы, обеспечивающие их работу, а с выхода дешифратора 3 на сумматор 4 подается начальный адрес А 1, соответствующий коду первого знака (номеру ветви

3

первого уровня). По третьему синхроимпульсу с вьтхода дешифратора 3 на сумматор 4 подается число лА2. В сумматоре 4 образуется начальный адрес, соответствующий номеру ветви второго уровня А2 А1 + лА2.- С выхода сумматора число А2 подается на информационные входы регистров tO, -10 и при поступлении сигнала,с третьего выход дешифратора 8, задержанного элементо 11 задержки, записывается в регистр 10 . По следующему синхроимпульсу с выхода дешифратора 3j на сумматор 4 подается число дАЗ. В сумматоре 4 образуется начальный адрес,соответству- ющий. номеру ветви второго уровня A3 А2 +л АЗ. С выхода сумматора число A3 записывается по сигналу с (к+ ,1)- го выхода дешифратора 8 в регистр Ю

По завершении преобразования кода номера объекта на выходе 22 устройства устанавливается соответствующий начальный адрес, а на выходе перепоЛ нения счетчика появится сигнал, по которому триггер 5 устанавливается в исходное, нулевое состояние и в регистр 14 переписывается содержимое регистра 1.

. Устройство готово к формированию адреса по следующему коду номера объекта.

Исходное состояние регистров для второго и последующих циклов формирования адреса следующее,

В регистры 1 и 14 записан код но- мера объекта предьщущего цикла, а в регистры - соответствующие начальные адреса, вычисленные в предыдущем цикле.

Работу устройства для второго и последующих циклов формирования адреса рассмотрим на примере формирования адреса объекта 4-го ранга (т. е. номер объекта состоит из четырех зна

ков, например а, а, а, Ъ ) по код

а.

номера объекта, который до третьего знака включительно совпадает с кодо номера объекта предьщущего цикла - записанного в регистр 14. По первому синхроимпульсу на первом выходе дешифратора 8 появляется сигнал, по которому триггер 18 уста- навлива1.тся в нулевое состояние, а в регистр 1 записывается код номера объекта , На выходах всех схем сравнения устанавливается сигнал 1, а на выходе схемы 15, сравнения - сигнал О. Шифратор 16 пре

gЮ 5 .

20

25

зд

2560274

образует результат сравнения (см. таблицу 1 в ко д 4, , сигнал на втором выходе отсутствует.

Триггер 18 нулевым сигналом на прямом выходе запрещает прохождение следующего синхроимпульса через элемент И 6 и разрешает сигналом с инверсного выхода прохождение второго синхроимпульса через элемент И 13 на вход записи счетчика 7. В счетчик 7 с информационного входа записывается код с первого выхода шифратора 16. Триггер 17 устанавливается в нулевое состояние. На дешифраторы 3 -3 управляющий сигнал не поступает, так как дешифратор 8 выключен нулевым сигналом с выхода триггера 17, поданным на его информационный вход. С выхода счетчика 7 код шифратора 16 по - дается на управляющий вход мультиплексора 9. Мультиплексор 9 выдает на выходе содержимое регистра 10, которое подается на сумматор 4. Та- ким образом, в сумматор 4 записан начальный адрес A3, соответствующий номеру ветви третьего уровня, вычис- ленной еще в предьщущем цикле. Следующий знак в номере объекта .отличен от знака в номере объекта предыдущего цикла, поэтому сигналом с элемента 23 задержки триггер 18 устанавливается в исходное состояние, разрешая - прохождение последующих синхроимпульсов через элемент И 6 на счетный вход счетчика 7. По третьему синхроимпульсу триггер 17 переходит в исходное состояние и включает дешифратор 8, с пятого выхода которого управляющий сигнал поступает на дешифратор 3. С выхода дешифратора 3. на сумматор 4 подается число ДВ4. В сумматоре 4 начальный адрес объекта четвертого ранга В4 A3 + йВ4 образуется уже после третьего синхроимпульса.

5

0

Формула изобретения

Устройство для формирования адресов памяти по авт. св. № 928358, о т- личающееся тем, что, с целью повышения быстродействия, в него введены К схем сравнения (к- количество рангов адресной информации), шифратор, группу из К регистров, группу из i элементов задержки, регистр, мультиплексор, второй и третий триггеры, элемент задержки, второй элемент И и элемент ИЛИ, причем вход установки в О первого триггера соединен с выходом переполнения счетчика, информационный вход которого соединен с первым выходом шифратора, второй выход которого соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом элемента задержки, вход которого соединен с выходом второго элемента И, входом записи счетчика И входом установки в О второго триггера, вход установки в 1 которого соединен с выходом первого элемента И, информационный выход счетчика соединен с управляющим входом мультиплексора, стробирующий вход которого соединен с прямым выходом третьего триггера и первым входом второго элемента И, второй и третий входы которого соединены соответствен но с выходом первого триггера и входом синхронизации устройства, вЬпсод элемента ИЛИ соединен с входом установки в О третьего триггера, инверсный выход которого соединен с тре- тьим входом первого элемента И,вход

Редактор С.Патрушева

Составитель Ю.Ланцов .

Техред Л.Сердюкова Корректор В.Синицкая

Заказ 4824/48Тираж 671 . Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

установки в 1 третьего триггера соединен с первым выходом дешифратора, выход второго триггера - со стробиру- ющим входом дешифратора, с третье -f го по (к+1)-й выходы которого соединены с входами Соответственно с первого по . элементов задержки группы выходы которых соединены с входами |записи одноименных регистров группы, информационные входы которых соединены с выходом сумматора, (к+1)-й вход которого соединен с выходом мультиплексора, с первого по к-и информационные входы которого соедине 1ы с .выходами одноименных регистров группы, с первого по к-и выходы входного регистра соединены с первыми входами одноименных схем сравнения группы и с одноименными информационными входами регистра, с первого по К-и выходы Которого соединены с вторыми входами одноименных схем сравнения группы, выходы которых соединены с одноименными входами шифратора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для распределения заданий процессорам | 1987 |

|

SU1462315A1 |

| Устройство для контроля цифровых объектов | 1988 |

|

SU1691841A1 |

| Двухкаскадное устройство для ранговой фильтрации | 1985 |

|

SU1304036A1 |

| Устройство для распределения заданий процессорам | 1987 |

|

SU1441399A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1991 |

|

RU2015550C1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1711167A1 |

| Устройство для контроля цифровых узлов | 1987 |

|

SU1571593A1 |

| Устройство для задержки информации с контролем | 1990 |

|

SU1795442A1 |

| Система динамической синхронизации и корректировки рангов объектов в АСУ | 1985 |

|

SU1305630A1 |

| Устройство для сопряжения ЭВМ с периферийным устройством | 1986 |

|

SU1363226A1 |

Изобретение относится к вычислительной технике, может быть использовано в автоматизированньгх системах идентификации информации, работающих в реальном масштабе времени. Цель изобретения - повышение быстродействия. Устройство содержит входной регистр 1, группу коммутаторов 2 -2 , группу дешифраторов 3, -3, кода адреса, сумматор 4, три триггера 5, 17, 18, два элемента И 6, 13, счетчик 7, дешифратор 8, мультиплексор 9, группу , регистров, группу злемен- тов задержки , злемент ИЛИ 12, регистр 14, группу схем сравнения, шифратор 16, элемент задержки 23. Указанная совокупность признаков позволяет достигнуть цели изобретения. 1 ил, 1 табл. (Л tc СП о о tc N3

| Устройство для формирования адресов памяти | 1980 |

|

SU928358A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-09-07—Публикация

1984-02-16—Подача