Изобретение относится к вычислительной технике и может быть использовано при построении надежных микропроцессорных систем.

Цель изобретения - повышение достоверности контроля программ в процессе их выполнения.

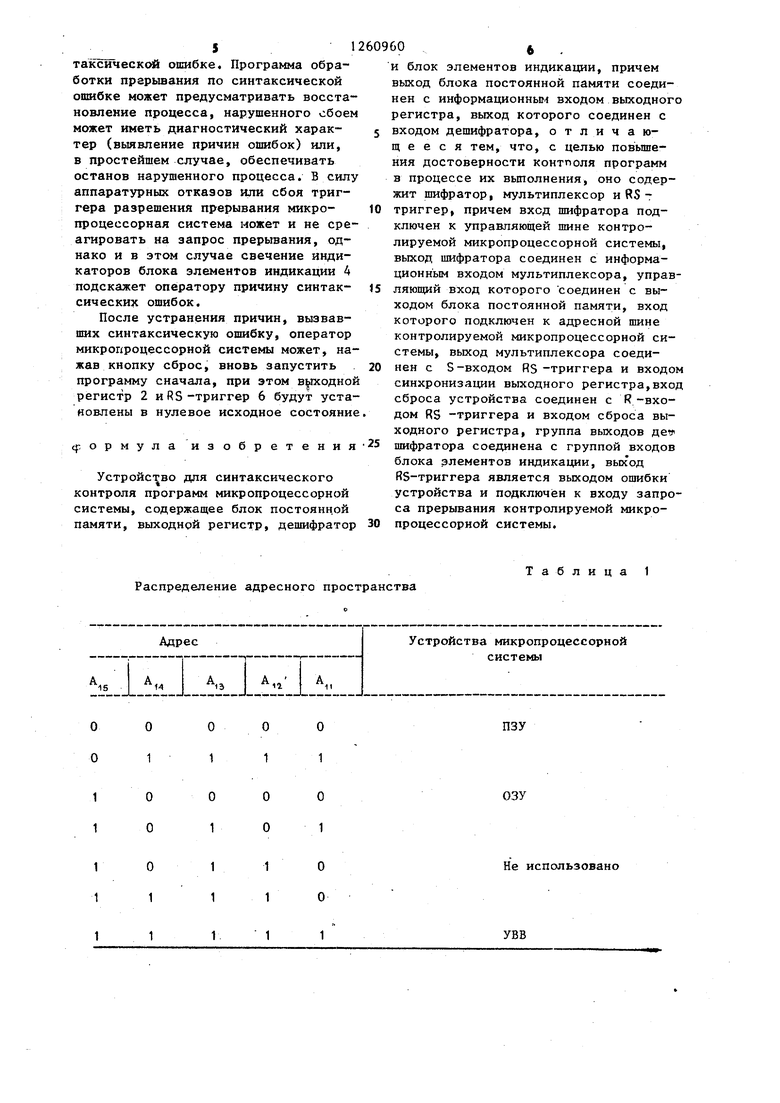

На чертеже представлена функциональная схема устройства для синтаксического контроля програм 5 микропроцессорной системы.

Устройство для синтаксического контроля программ т кропроцессорной системы содержит (фиг„1) блок постоянной памяти 1, вь содной регистр 2, дешифратор 3, блок 4 элементов индикации, шифратор 5,RS -триггер 6, мультиплексор 7, выход ошибки 8 устройства, шину управления 9 контролируемой микропроцессорной системы, шину адреса 10 контролируемой микропроцессорной системы, вход сброса 1 устройства.

Все блоки предлагаемого устройства являются стандартными и легко реализуются на интегральных микросхемах, например серии К155.

Устройство работает следующим образом.

Устройство обеспечивает синтаксический контроль программ наиболее распространенной микропроцессорной системы с тремя шинами: шиной адреса, шиной данных и шиной управления. В процессе работы входы ад- ipeca 10 устройства подключаются к старшим разрядам адресной шины ми- .кропроцессорной системы, входы управ ления 9 - к шине управления, выход сигнла синтаксической ошибки 8 к входу запроса прерывания микропроцессора,а вход сброса 11 - к цепи сброса микропро .цессора.

Типовая микропроцессорная система с тремя шинами имеет следующие сигналы в составе шины управления: чтение памяти ЧТ; запись в память ЗП; ввод BB J вьшод ВЫВ, загрузка в стек зет; извлечение из стека ИСТ ; чТе- ние первого байта команды Ml.

При этом предполагается, что эти сигналы стробированы со ответствую- ш;ими строб-сигналами микропроцессора Прием (DBIN) тли Запись (WR).

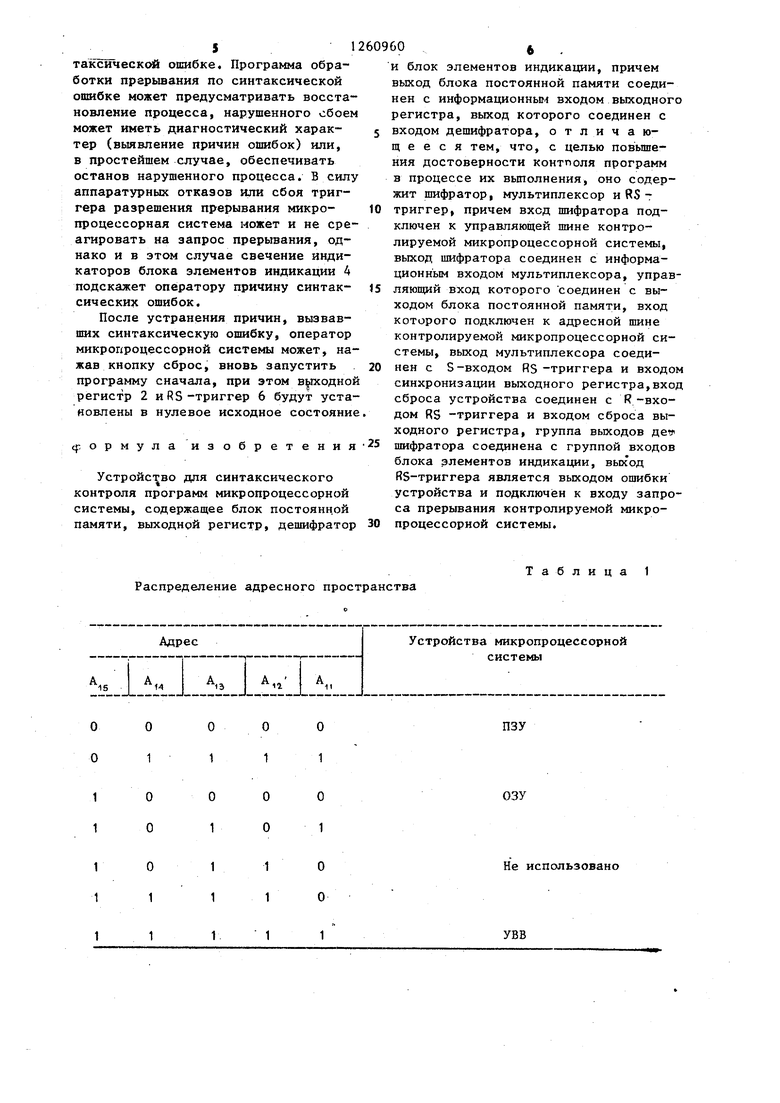

В общем случае микропроцессорная система содержит постоянную память (ПЗУ), оперативную память (ОЗУ) и устройства ввода-вывода (УВВ) . На

стадии программирования программист распределяет зону адресного пространства микропроцессора и закрепляет за каждым из устройств системы определенную адресную зону.

Для обращения к конкретному устройству микропроцессор формирует на шине адреса соответствующий код, обеспечивающий активацию выбранного

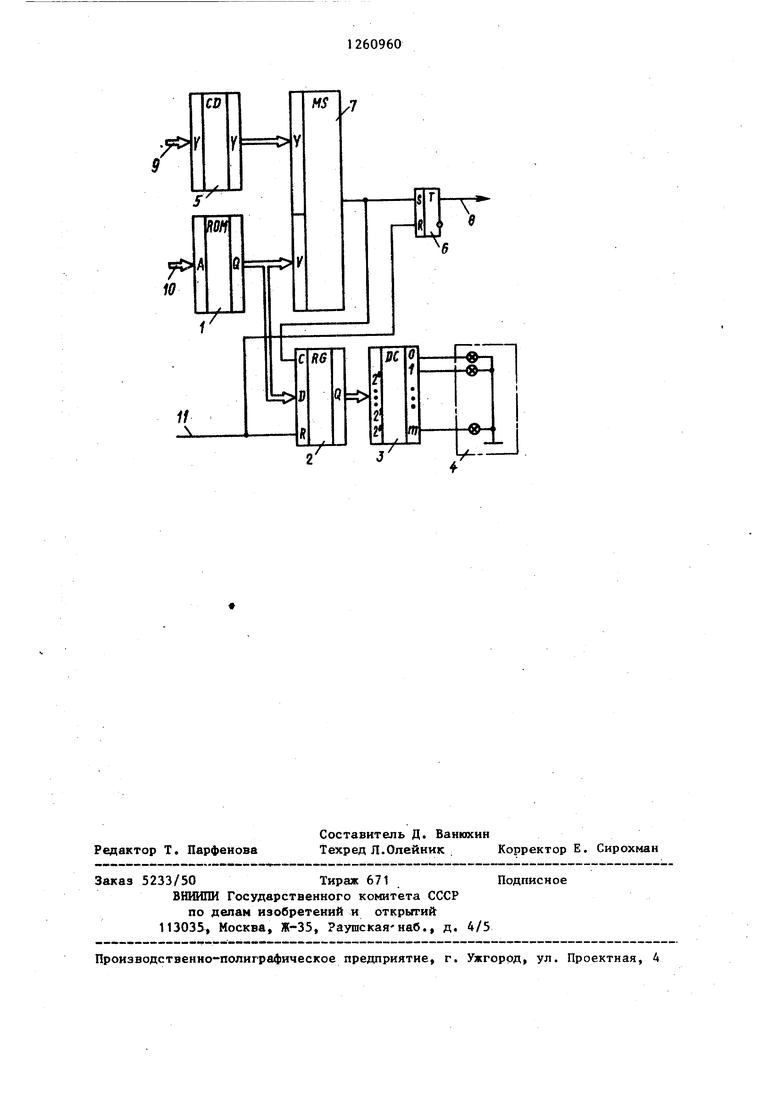

устройства. При этом, для упрощения селекции выбираемого устройства распределение адресов осуществляется таким образом, чтобы по старшим разрядам адреса можно, быпо бы определить устройство, к которому осуществляется обращение. Пусть, например, для идентификации выбираемого устройства системы использрвано 5 разрядов адреса А , А , А , А,,, ,

А и зоны адресного пространства распределены в соответствии с табл.1.

При таком составе контролируемой микропроцессорной системы устройство,

к которому осуществляется обращение, может быть указано двухразрядньм кодом. Перекодирование входного многоразрядного кода на старших разрядах шины адреса в код, указывающий тип

выбираемого устройства, осуществляется блоком постоянной памяти 1. Для этого в нем по соответствующим адресам хранятся коды устройства микропроцессорной системы. Пусть код ПЗУ-01, код ОЗУ-10, код УВВ-11, а

код неиспользованной зоны - 00. Тогда в блоке постоянной памяти 1 должны храниться коды в соответствии с табл. 2.

Таким образом, при обращении микропроцессора какому-либо конкретному устройству системы на выходах блока постоянной памяти 1 формируется соответствунлций код и мультиплексор 7 выбирает соответствукяций

информационный вход, подключенный

к одному из выходов шифратора 5. Шифратор 5 должен обеспечивать кодирование синтаксически некорректных ситуаций, например, в соответствии

с табл. 3.

Каждый разряд выходного кода шифратора 5 соответствует устройству микропроцессорной системы, г единицы в нем соответствуют некорректным входным сигналам для этого устройства. Например, разряд У, соответствует ПЗУ и некорректными входными сигналами для него являются ЗП, ВВ, ВЫВ, ЗСТ,

3 . ИСТ. Для неиспользованной зоны адреного пространства любой управляющий сигнал будет некорректным. При нормальной работе микропроцесссрной системы исполняемые команды синтаксически корректны, поэтому на выходе шифратора 5 и на выходе мультиплексора 7 будет постоянньй уровень логического нуля. Это связано с тем.

что на управляющих входах мультиплек сора 7 блок постоянной памяти 1 устанавливает код устройства, к которому идет обращение, и выбирается соответствующий информационный вход мультиплексора 7. Последний подключен к соответствующему выходу шифратора 5 (табл. 2), где закодированы только некорректные обращения (табл. 3). Поскольку на выход мультиплексора 7

25

сигнал не поступает, выходной регистр 20 сорной системы, к которому произошло

некорректное обращение. Этот код будет декодирован дешифратором 3, и в блоке элементов индикации будет высвечен соответствующий элемент, свидетельствующий о том, что произошла синтаксическая ошибка определенного типа (например, красного цвета).

Так например, при попытке извлечения команды из зоны ОЗУ на выходе блока постоянной памяти 1 будет согласно табл. 2. установлен код 10 и, соответственно, будет выбран вход мультиплексора 7, связанный с вы- При исполнении процессором микро- 35 ходом У . шифратора 5 (). Со2 остается в обнуленном состоянии, которое было установлено при сбросе микропроцессорной системы через вход сброса 11 устройства. Нулевой код с выхода выходного регистра поступает на вход дешифратора 3, в результате чего на его выходе О устанавливается активньш потенциал. Это- приводит к засветке соответствующего элемента индикации блока элементов индикации 4, свидетельствующего о синтаксически правильной работе процессора (например, зеленого цвета).

30

процессорной системы программы, в результате сбоя или отказа его элементов возможны выборка или исполнение синтаксически некорректных команд. К таким ситуациям относится 40 попытка извлечения команды из зоны оперативной памяти в результате сбоя программного счетчика процессора, попытка записи числа в зону ПЗУ в результате отказа одного из разрядов 45 шины данных и искажения адреса в команде с прямой адресацией и т.п. Некорректным является также любое обращение к неиспользуемой зоне адрес- ног© пространства.50

В случае появления указанных синтаксических искажений работа устройства описывается следующей последовательностью событий.

Блок постоянной памяти 1 устана в- ния микропрессорной системы, возниливает на управлякяцих входах мультиплексора 7 код соответствующего устройства микропроцессорной системы,

к которому должно производиться обращение. Благодаря этому, среди информационных входов мультиплексора 7 выбирается тот, который связан с соответствующим выходом шифратора 5. При некорректной ситуации, т.е. когда адресу не соответствует состояние входов управления 9, на соответствующем выходе шифратора 5 и выбранном входе мультиплексора 7 появится импульс и он пройдет на5 гвход Д8 триг- гера 6. Последний перейдет в состояние логической единицы, сигнал которой поступит на выход синтаксичес- 5 кой ошибки устройства 8. Одновременно этот импульс поступит на вход синхронизации выходного регистра 2. Благодаря этому в него будет записан код устройства микропроцес10

25

35

30

гласно табл. 3 сигнал Ml, поступивший на вход шифратора 5, при извлечении команды пройдет на выход шифратора УГ, и через мультиплексор 7 поступит на S -вход -триггера 6, что приведет к установке его в состояние логической единицы и вьща- че активного сигнала на выход синта- тической ошибки устройства 8. Этот же сигнал с выхода мультиплексора 7 запишет в выходной регистр 2 код 10, и дешифратор 3 выберет и засветит третий сверху элемент индикации блока элементов индикации 4. Этот элемент можно назвать Синтаксическая ошибка при обращении к ОЗУ.

Кроме световой индикации, благодаря связи выхода синтаксической ошибки 8 со входом запроса прерывакает прерывание текущей программы и уход микропроцессорной системы на программу обработки прерывания по синтаксической ошибке. Программа обработки прерывания по синтаксической ошибке может предусматривать восстановление процесса, нарушенного сбоем может иметь диагностический харак- тер (выявление причин ошибок) или, в простейшем случае, обеспечивать останов нарушенного процесса. В силу аппаратурных отказов или сбоя триггера разрешения прерывания микро- процессорная система может и не среагировать на запрос прерывания, однако и в этом случае свечение индикаторов блока элементов индикации 4 подскажет оператору причину синтак- сических ошибок.

После устранения причин, вызвавших синтаксическую ошибку, оператор микропроцессорной системы может, нажав кнопку сброс, вновь запустить программу сначала, при этом вводной регистр 2 и RS-триггер 6 будут установлены в нулевое исходное состояние

cf. ормула изобретения

Устройс во для синтаксического контроля программ микропроцессорной системы, содержащее блок постоянной памяти, выходной регистр, дешифратор

Распределение адресного пространства

О

1

О О

1 1

о

1

о 1

о о

и блок элементов индикации, причем выход блока постоянной памяти соединен с информационным входом выходного регистра, выход которого соединен с входом дешифратора, отличающееся тем, что, с целью повьште- ния достоверности контполя программ в процессе их вьшолнения, оно содержит шифратор, мультиплексор и RS- триггер, причем вход шифратора подключен к управляющей шине контролируемой микропроцессорной системы, выход шифратора соединен с информационным входом мультиплексора, управляющий вход которого соединен с выходом блока постоянной памяти, вход которого подключен к адресной шине контролируемой микропроцессорной системы, выход мультиплексора соединен с S-входом RS -триггера и входо синхронизации выходного регистра,вхо сброса устройства соединен с R -входом RS -триггера и входом сброса выходного регистра, группа выходов де шифратора соединена с группой входов блока элементов индикации, выход RS-триггера является выходом ошибки устройства и подключён к входу запроса прерывания контролируемой микропроцессорной системы.

Таблица 1

ПЗУ

ОЗУ

Не использовано

Кодовые соотношения устройства

Код на входах Тип Код на выходе Выбираемый информационный адреса 10 устройства постоянного вход мультиплексора 7

системы запоминакнцего устройства 1

000О О ПЗУ .011

011110,1 .

1о о о о ОЗУ102

1010110.

1 о 1 1 о -00о

.

1111000

1 1 1 1 1 УВВ ,113

1--, :

ТаблицаЗ Таблица истинности 1ш1фратора 5

Входные сигналы шифратора 5Выходные сигналы шифратора 5

ЧТ ЗПВВ ВЫВ зет ИСТ г

о 1 о о о о о о

о о 1 о о о о о

о о о 1 о о о о

о о о о 1 о о о

Д а б л и ц а 2

о о о о о о 1 о

1 1 1 1 1 1 I о

о 1 1 1 1 1 о о

о о 1 1 о о 1 о

о о 1 1 1 о

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля программ | 1986 |

|

SU1332323A1 |

| Устройство для контроля микропроцессорной системы | 1988 |

|

SU1536384A1 |

| Устройство для контроля микропроцессорной системы | 1987 |

|

SU1474650A2 |

| Устройство для контроля микропроцессорной системы | 1988 |

|

SU1545221A1 |

| Устройство для контроля микропроцессорной системы | 1989 |

|

SU1640693A1 |

| Устройство для контроля микропроцессорной системы | 1987 |

|

SU1460722A1 |

| Устройство прерываний микропроцессорной системы | 1988 |

|

SU1621030A1 |

| Устройство для контроля хода программ | 1988 |

|

SU1545223A1 |

| Устройство для контроля микропроцессора | 1988 |

|

SU1599862A1 |

| СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМ ОБОРУДОВАНИЕМ | 2000 |

|

RU2189623C2 |

Изобретение относится к вычислительной технике и может быть ис- пользовано при построении надежных микропроцессорных систем. Цель изобретения - повыпение достоверности контроля за счет выявления синтаксически некоррективных процедур. Устройство содержит блок постоянной памяти, выходной регистр, дешифратор, блок элементов индикации, шифратор, мультиплексор иК8 -триггер. Устройство подключено к шинам адреса и уп- равле ния контролируемой микропроцессорной системы, выход сигнала синтаксической ошибки устройства подключен к входу запроса прерывания контролируемой микропроцессорной системы. 1 ил., 3 табл. (Л С

Редактор Т. Парфенова

Составитель Д. Ванкжии

Техред Л.Олейник . Корректор Е. Сирохман

Заказ 5233/50Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская-наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Дж | |||

| Коффрон | |||

| Техничес кне средства микропроцесГсорных систем | |||

| М.: Мир, 1983 | |||

| Устройство для синтаксическогоКОНТРОля пРОгРАММ | 1978 |

|

SU807299A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-09-30—Публикация

1985-03-07—Подача