1

Изобретение относится к вьтчисли- тельной технике и может быть использовано при построении высокопроизводительных вычислительных систем, таких как суперкомпьютеры, цифровые фильтры, процессоры быстрого преобразований Фурье.

Цель изобретения - расширение « функциональных возможностей за счет декодиро-вания множителя в процессе умножения.

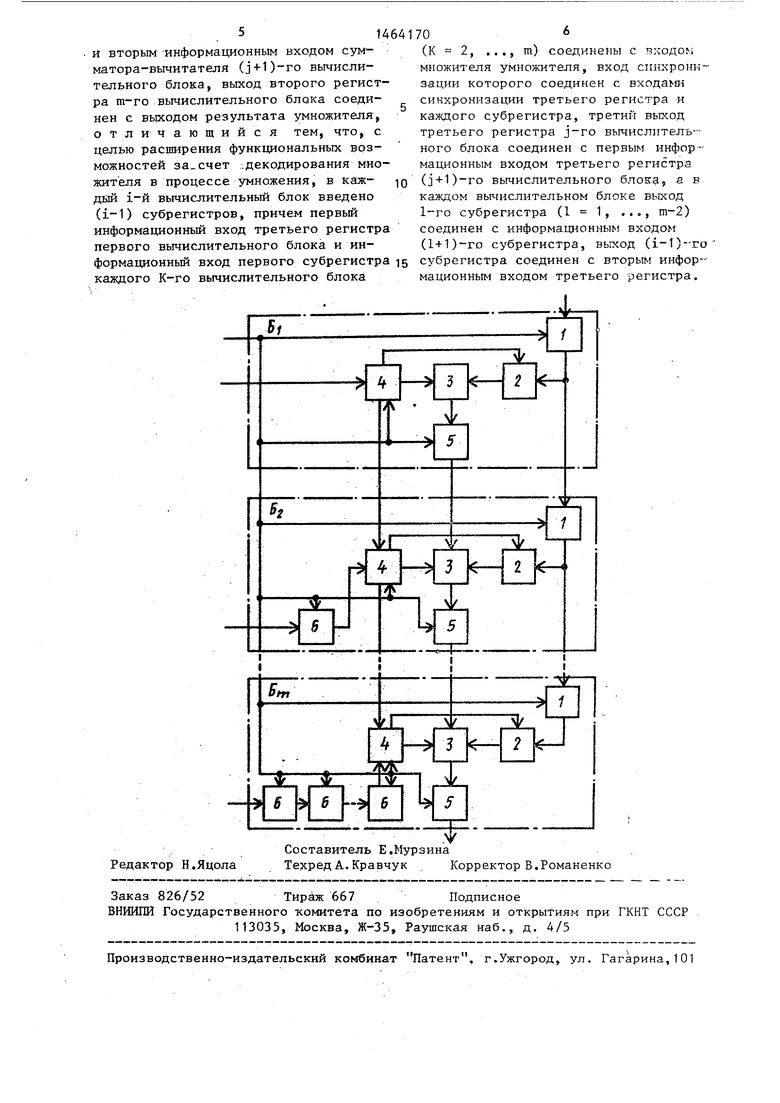

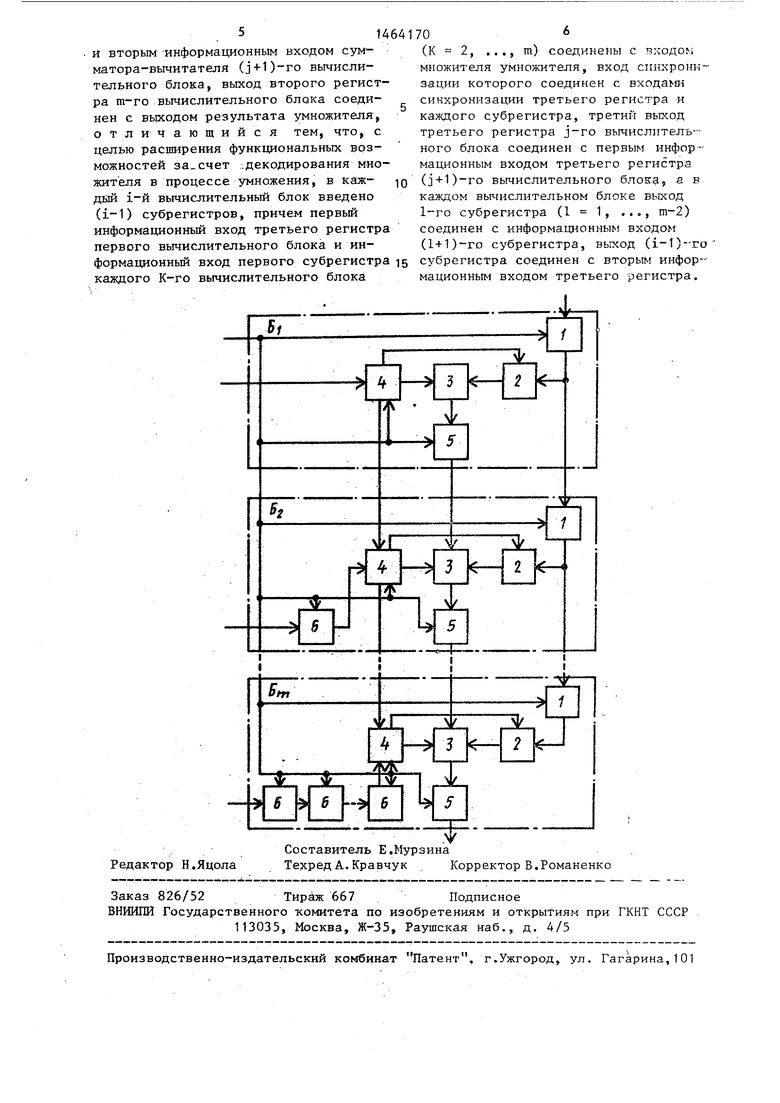

На чертеже представлена функциональная схема конвейерного цифрового умножителя.

Умножитель содержит m вычислительных блоков Б,, Б, ..., Б (где m

г, п - количество разрядов множит) вычислителя), каждый из которых содержит первый регистр 1, коммутатор 2, сум- матор-вьр итатель 3, второй регистр 4 и третий регистр 5. Кроме того, .каждый К-й (К 2, .. тельный блок входит цепочка из (К-1) субрегистров 6.

Первый регистр 1 блоков служит для хранения и передачи множителя. Вто- рой регистр 4 блоков служит для декодирования частичных множителей, поступающих на его входы согласно модифицированному алгоритму Бута. Тре- тий регистр 5 блоков служит для хранения частичных произведений. Субрегистры 6 служат для хранения частичных множителей, разрядность которых в соответствии с модифицированным алгоритмом Бута равна 2.

Конвейерный умножитель работает следующим образом.

Пусть необходимо перемножитель

операнды А

( J is

А„ и В

В разрядностью, равной 4. Следовательно, умножитель содержит два вычислительных блока, Калщый умножитель условно разбиваем на два частичВ третьем такте операнд А заме-т щает операнд А, которьм, в свою очередь, выталкивает А.. В регистрах 5

блоков Б, и Б„

Ь-и Ь|

)j и о запоминаются суммы частичных произведений, полученные

ных множителя

причем младшая пара битов I by поступает на регистр 4 блока Бд, а старшая пара битов Ь| подается на вход субрегистра 6 блока Б,„ В общем случае цепочки субрегистров 6 работают is по принципу FIFO первый вошел - первый вьппел, благодаря чему в К-м вычислительном блоке организуется очередь частичных множителей с дисциплиной FIFO, Множимое поступает на вход регистра 1 первого блока. Умножитель управляется синхронно от тактового генератора конвейерной системы .

В регистрах 4 блоков Б, и Б, фиксируются инструкции fS 1 опре- делягош:не функционирова та е сумматора- вычитателя 3 и коммутатора 2 блоков

(s 1, .., r),io во втором тактовом периоде, при этом

на выход умножителя поступает произведение операндов А, и В, Кроме того, инструкции fj и f загружаются в

ственно, а частичный множитель Ь.

В четвертом такте операнд AJ, очередная сумма частичных произведений и инструкция f заносятся в соответ 2

3 2 регистры 4 блоков Б и Б соответсубрегистр 6 фиксирует

20

ствуюшре узлы первого блока. Операнд А, полученная сумма частичных произведений, частичньй множитель Ы и инструкция f| запоминаются в соответствующих узлах блока Bg, при.этом на 25 выходе конвейерного умно.жителя появляется произведение операндов А и.К .

Таким образом, умножитель вьщает произведение двух операдцов в каждом тактовом периоде. Формула изобретения

и

Ъ соответственно. При этом в

формировании инструкции f| участвует один бит частичного множителя Ъ , который поступает на вход регистра 4 блока Б с выхода регистра 4 блока Б , в котором он фиксируется вместе с инструкцией fg.

В первом такте работы конвейера умножения в регистры 1 и 4 блока Б загружаются операнд А и инструкция f, , соотйетствующая частичному множителю Ь| , а в субрегистр 6 блока Б, заносится частичный множитель Ь. Таким образом, вычисление первой суммы частичных произведений, соответ- ствующ.ей умножению А, на В, , в перразрядностьтеля) , каждый из которых сод регистра, сумматор-вычитател мутатор, причем вход множимо жителя соединен с информацио 40 дом первого регистра первого тельного блока, вход синхрони умножителя соединен с входами низации первого и второго ре всех вычислительных блоков,

вом блоке и декодирование bf во вто- g дом i-м вь слительном блоке

блоке происходит параллельно. Во втором такте инструкция f, операнд А и первая сумма частичных произведений заносятся соответственно в регистр 4 и регистры 1 и 5 блока Б « Операнд А| пересылается в регистр множимого второго блока, в субрегистр 6 которого записывается частичньй множитель Ь, а в регист- 1, ..., m) выход первого р соединен с первым информацион дом ком1 1утатора, выход которо динен с первым информационным 50 сумматора-вычитателя, вькод к соединен с информационным вхо рого регистра, первый и второ ды третьего регис-тра соединен ветственно с управляющими вхо

- 1, ..., m) выход первого регистра соединен с первым информационным вх дом ком1 1утатора, выход которого сое динен с первым информационным входо 50 сумматора-вычитателя, вькод которог соединен с информационным входом вт рого регистра, первый и второй выхо ды третьего регис-тра соединены соот ветственно с управляющими входами

ре 4 фиксируется инструкция 2. Сле- 55 коммутатора и сумматора-зычитателя, довательно, в первом блоке вычисляется первая сумма частичных произвевыходы первого и второго регистров j-ro вычислительного блока (j 1, . m-1) соединены соответственно с информационным входом первого регистр

дений для операндов А и В, а в о втором блоке вычисляется вторая сумма частичных произведений для операн- дов А, и В, и формируется инструк1ЩЯ 2.

В третьем такте операнд А заме-т щает операнд А, которьм, в свою очередь, выталкивает А.. В регистрах 5

блоков Б, и Б„

)j и о запоминаются суммы частичных произведений, полученные

во втором тактовом периоде, при это

s

на выход умножителя поступает произведение операндов А, и В, Кроме того, инструкции fj и f загружаются в

ственно, а частичный множитель Ь.

В четвертом такте операнд AJ, очередная сумма частичных произведений и инструкция f заносятся в соответ 2

3 2 регистры 4 блоков Б и Б соответсубрегистр 6 фиксирует

0

ствуюшре узлы первого блока. Операнд А, полученная сумма частичных произведений, частичньй множитель Ы и инструкция f| запоминаются в соответствующих узлах блока Bg, при.этом на 5 выходе конвейерного умно.жителя появляется произведение операндов А и.К .

Таким образом, умножитель вьщает произведение двух операдцов в каждом тактовом периоде. Формула изобретения

0

Конвейерный цифровой умножитель, содержащий m вычислительных блоков

35

/ Т

(т 2

где п разрядность множителя) , каждый из которых содерхсит три регистра, сумматор-вычитатель и коммутатор, причем вход множимого умножителя соединен с информационным вхо- 40 дом первого регистра первого вычислительного блока, вход синхронизации умножителя соединен с входами синхронизации первого и второго регистров всех вычислительных блоков, а в дом i-м вь слительном блоке

(i

- 1, ..., m) выход первого регистра соединен с первым информационным входом ком1 1утатора, выход которого соединен с первым информационным входом 50 сумматора-вычитателя, вькод которого соединен с информационным входом второго регистра, первый и второй выходы третьего регис-тра соединены соответственно с управляющими входами

55 коммутатора и сумматора-зычитателя,

коммутатора и сумматора-зычитателя,

выходы первого и второго регистров j-ro вычислительного блока (j 1, ... m-1) соединены соответственно с информационным входом первого регистра

514

и вторым -информационным входом сум- матсра-вычитателя (j+1)-ro вычислительного блока, выход второго регистра т-го вычислительного блока соединен с выходом результата умножителя, отличающийся тем, что, с целью расширения функциональных возможностей .декодирования множителя в процессе умножения, в каж- дай i-й вычислительный блок введено (i-1) субрегистров, причем первый информационный вход третьего регистра первого вычислительного блока и информационный вход первого субрегистра каждого К-го вычислительного блока

706

(К 2т) соединены с 5xoдo i

множителя умножителя, вход синхронизации которого соединен с входаш синхронизации третьего регистра и каждого субрегистра, третий выход третьего регистра j-ro вычислительного блока соединен с первым информационным входом третьего регистра (j+1)-ro вычислительного блока, а в каждом вычислительном блоке выход 1-го субрегистра (, ..., т-2) соединен с информационным входом (1+1)-го субрегистра, выход (i-l)-TO субрегистра соединен с вторьм информационным входом третьего регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Конвейерный умножитель | 1988 |

|

SU1575175A1 |

| Конвейерное вычислительное устройство | 1987 |

|

SU1432512A1 |

| Конвейерное множительное устройство | 1980 |

|

SU903866A1 |

| Устройство для умножения | 1976 |

|

SU651341A1 |

| Устройство для умножения чисел | 1990 |

|

SU1714595A1 |

| Вычислительное устройство | 1980 |

|

SU957203A1 |

| Устройство для умножения @ -разрядных двоичных чисел | 1990 |

|

SU1783519A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Вычислительное устройство | 1988 |

|

SU1532917A1 |

| Устройство для вычисления функций | 1990 |

|

SU1709304A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении высокопроизводительньгх вычислительных систем, таких как суперкомпьютеры, цифровые. фильтрЕ т, процессоры быстрого преобразования Фурье. Цель изобретения - расширение функциональных возможностей за счет декодирования множителя в процессе умножения. Устройство содержит три регистра, комм: татор и сумматор-вычитатель. Новым в устрой- стве является введение в каждый К-й вычислительный блок цепочки из. К-1 субрегистров, работающей по принципу FIFO, благодаря чему обеспечивается временной сдвиг множителя для поддержки конвейерного режима работы устг ройства, а также декодирование час- . тичных множителей в процессе его функционирования. 1 ил. Ф

| Коугли П.М | |||

| Архитектура конвейер ньсх ЭВМ: Перев | |||

| с англ.- М.: Радио и связь, 1985, с | |||

| Нефтяной конвертер | 1922 |

|

SU64A1 |

| Авторское свидетельство СССР № 1206800, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-03-07—Публикация

1987-07-01—Подача