ел

00

-а

00

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сдвига и нормализации | 1989 |

|

SU1667045A1 |

| Устройство для сдвига данных | 1983 |

|

SU1140113A1 |

| Устройство для быстрого преобразования Фурье | 1988 |

|

SU1524066A1 |

| Устройство для формирования сигналов | 1989 |

|

SU1651294A1 |

| Разрядно-модульное арифметическое устройство | 1989 |

|

SU1649534A1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1985 |

|

SU1315969A1 |

| Устройство для побитовой обработки чисел,представленных в форме с плавающей запятой | 1980 |

|

SU938284A1 |

| Генератор случайного импульсного процесса | 1981 |

|

SU955047A1 |

| Устройство для нормализации чисел | 1986 |

|

SU1307454A1 |

| Арифметическое устройство | 1989 |

|

SU1647557A1 |

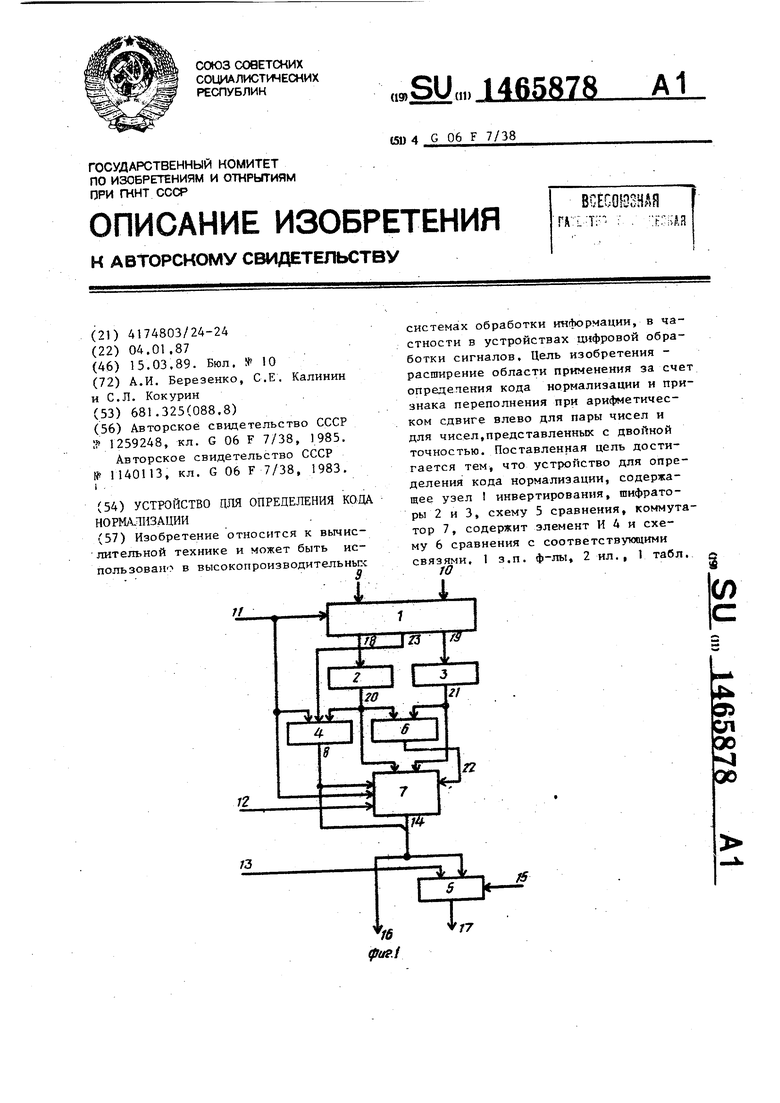

Изобретение относится к вычис . „„и Tovuuu-p и может быть иссистемах обработки информации, в частности в устройствах Щ1фровой обработки сигналов. Цель изобретения - расширение области применения за счет определения кода нормализации и при знака переполнения при арифметичес ком сдвиге влево для пары чисел и для чисел,представленных с двойной точностью. Поставленная цель достигается тем, что устройство для определения кода нормализации, содержащее узел 1 инвертирования, шифраторы 2 и 3, схему 5 сравнения, коммутатор 7, содержит элемент И 4 и схему 6 сравнения с соответствующими 1 з.п. ф-лы, 2 ил., 1 табл. i (Л

Г6

«я/

Изобретение,относится к вычислительной технике и может быть использовано в высокопроизводительных системах обработки информаили, в частности в устройствах цифровой обработки сигналов.

Цель изобретения - расширение области применения за счет определения кода нормализации и признака переполнения (при арифметическом сдвиге влево) для пары чисел и для чисел, представленных с двойной точностью.

Г

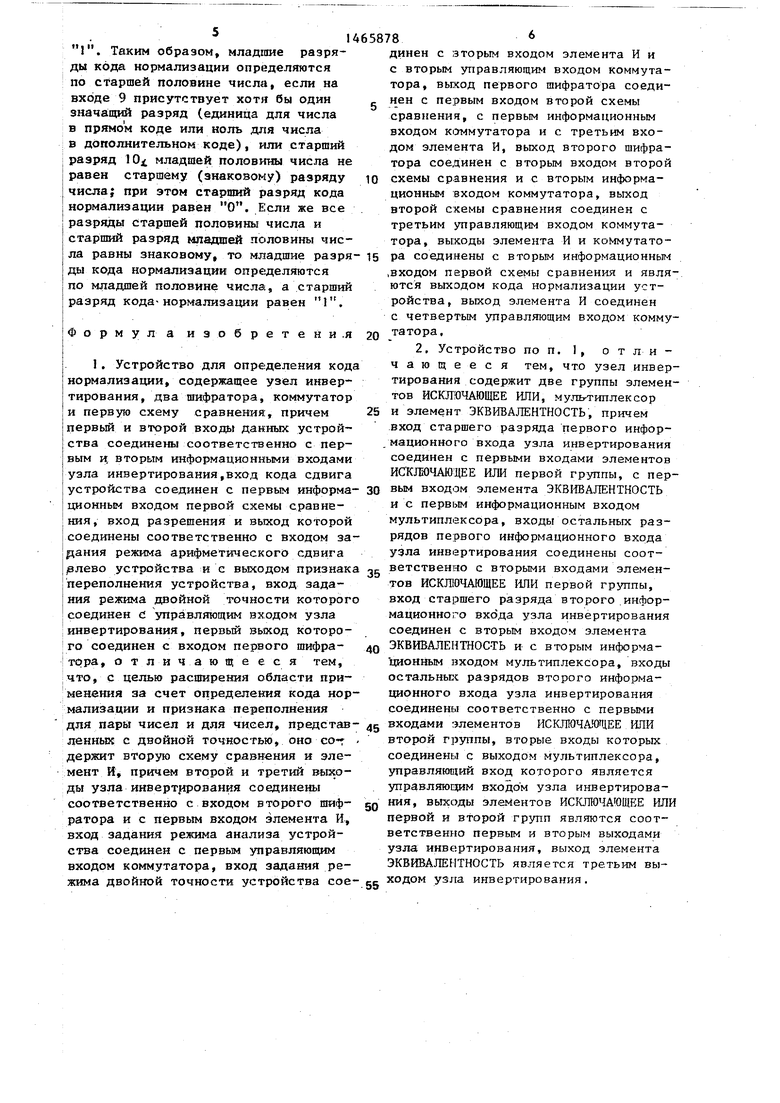

На фиг,1 приведена схема устройства для определения кода нормализации; на фиг, 2 - схема узла инвертирования .

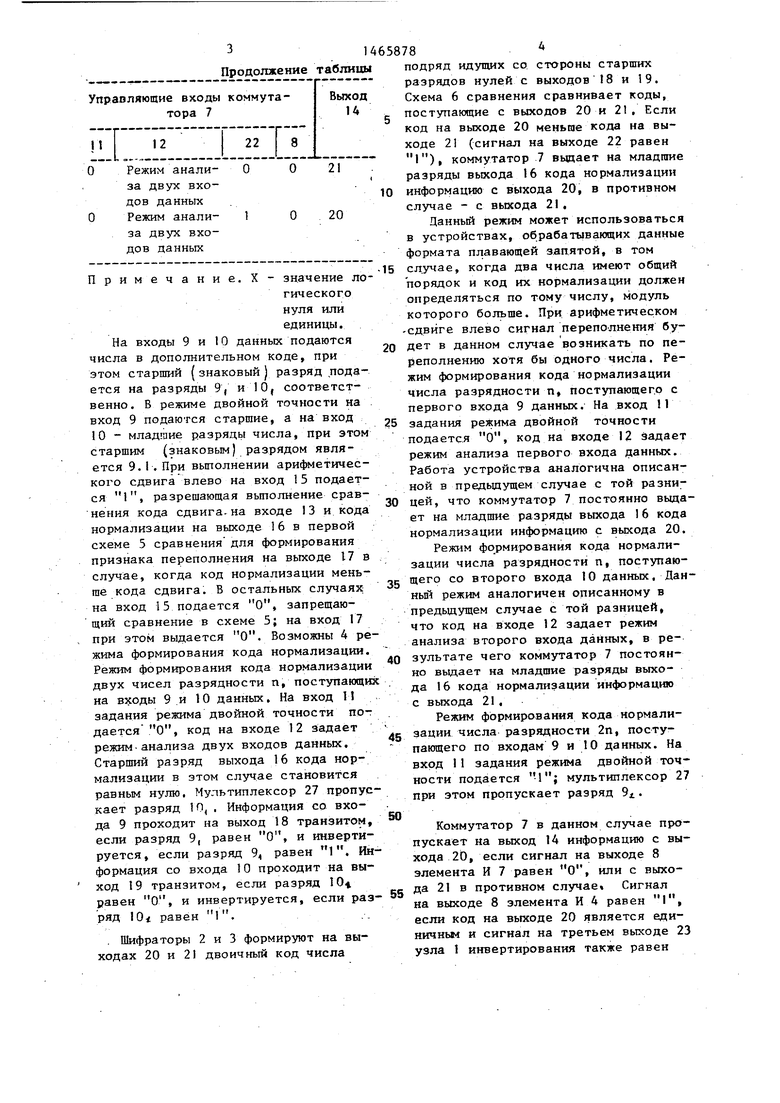

Устройство для определения кода нормализации (фиг.1) содержит узел 1 инвертирования, первьй шифратор 2, второй шифратор 3, элемент И 4, первую и вторую схемы 5 и 6 сравнения, коммутатор 7, выход 8 элемента И 4, первый и второй входы 9 и 10 данных устройства вход I1 задания режима двойной точности устройства, вход I2 задания режима анализа устройства, вход 13 кода сдвига устройства,выход 14 коммутатора 7, вход 5 задани режима арифметического сдвига влево устройства, выход 16 кода нормализации устройства, выход 17 признака переполнения устройства, первый выход 18 узла инвертирования, второй выход 19 узла инвертирования, выход 20 первогр шифратора 2, выход 21 второго шифратора 3, выход 22 второй схемы 6 сравнения, третий выход 23 узла 1 инвертирования.

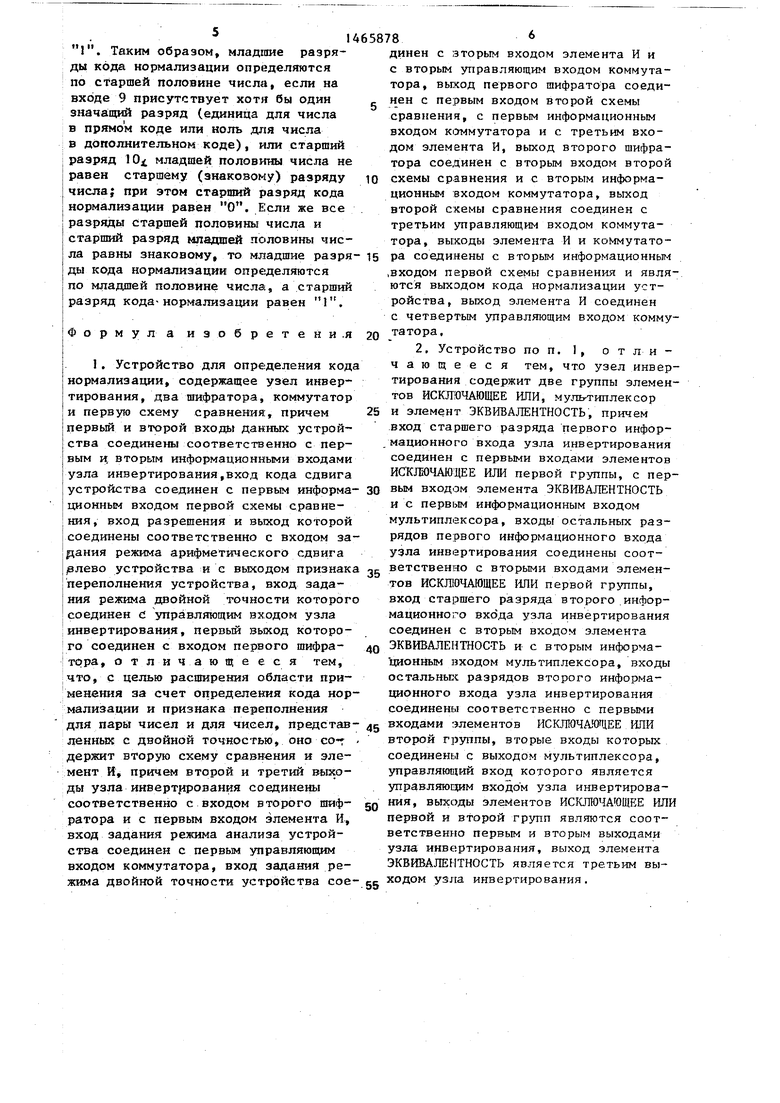

Узел I инвертирования (фиг. 2) содержит элемент 24 ЭКВИВАЛЕНТНОСТЬ, первую группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 25,-25„.1 , вторую группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 26 ,-26., , мультиплексор 2-7 (где п - разрядk

ность входов 9 и 0, причем , где k - целое положительное число).

Устройство (фиг. 1) работает следующим образом,

Узел I инвертирования осут ествля- ет транзитную передачу информации со входов 9 и 10 или ее инвертирование в том случае, когда на выходе находится отрицательное число в дополнительном коде, т.е. старший знаковый разряд числа на входах 9( или 10, равен единице. Информация со входа 9 (разряды ) передается

на вькод 18 (разряды 18,-1,8„., ) транзитам, если разряд 9 равен О, и инвертируется, если разряд 9. равен 1. Если сигнал на входе П равен 1, то на выход мультиплексора 27 вьщается сигнал разряда 9,, в противном случае - сигнал разряда 10,,

Информация со входа 10 (разряды ) передается на выход 19 (разряды 19,- 9,, ) транзитом, если сигнал на выходе мультиплексора 27 равен О, и инвертируется, если этот сигнал равен 1. На выходе элемента ЭКВИВАЛЕНТНОСТЬ 24 сигнал, равный 1, возникает при равенстве сигналов разрядов 9 и 10,.

Шифраторы 2 и 3 предназначены для формирования на выходах 20 и 21 двоичного кода числа подряд идущих со стороны старших разрядов нулей.

Первая схема 5 сравнения предназначена для выработки признака пере- полнения при левом арифметическом сдвиге. В схеме 5 происходит сравнение кодов нормализации и сдвига. Если код нормализации меньше кода сдвига и сигнал на выходе 15 зада- ния режима арифметического сдвига влево равен 1, вырабатывается признак переполнения. В том случае,: когда код на выходе 20 меньше кода на выходе 21, вырабатывается соот-; ветствук1щий сигнал (1) на выходе 22 второй схемы 6 сравнения.

Коммутатор 7 выдает на младшие разряды выхода 16 кода нормализации информацию с выходов 20 или 21, -Значения управляющих сигналов со входов 11 и 12 и с выходов 22, 8 и соответствующие им выполняемые коммутатором 7 функции приведены в таблице .

за первого входа данных Режим анализа второго входа данных

21

Продолжение таблицы

20

Примечание

входы

X - значение логическогонуля или единицы. 9 и 10 данных подаются

На

числа в дополнительном коде, при этом старший (знаковый ) разряд подается на разряды 9, и 10, соответственно. В режиме двойной точности на вход 9 подаются старшие, а на вход 10 - младшие разряды числа, при этом старшим (знаковым) разрядом является 9.1. При выполнении ари етичес- кого сдвига влево на вход 15 подается 1, разрешающая выполнение сравнения кода сдвига.на входе 13 и кода нормализации на выходе 16 в первой схеме 5 сравнения для формирования признака переполнения на выходе 17 в случае, когда код нормализации меньше кода сдвига. В остальных случаях на вход 15 подается О, запрещающий сравнение в схеме 5; на вход 17 при этом выдается О. Возможны 4 режима формирования кода нормализации. Режим формирования кода нормализации двух чисел разрядности п, поступающи на входы 9 и 10 данных. На вход 15 задания режима двойной точности подается О, код на входе 12 задает режим.анализа двух входов данных. Старший разряд выхода 16 кода нормализации в этом случае становится равным нулю. Мультиплексор 27 пропускает разряд 10 , Информация со входа 9 проходит на выход 18 транзитом, если разряд 9, равен О, и инвертируется, если разряд 9, равен 1. Информация со входа 10 проходит на выход 19 транзитом, если разряд 10 равен О, и инвертируется, если разряд 10 равен 1.

Шифраторы 2 и 3 формируют на выходах 20 и 21 двоичный код числа

0

15

20

25

30

35

40

45

50

55

подряд идущих со стороны старших разрядов нулей с выходов 18 и 19. Схема 6 сравнения сравнивает коды, поступающие с выходов 20 и 21, Если код на выходе 20 меньше кода на выходе 21 (сигнал на выходе 22 равен I), коммутатор 7 вьщает на младшие разряды выхода 16 кода нормализации информацию с выхода 20, в противном случае - с выхода 21,

Данный режим может использоваться в устройствах, обрабатывающих данные формата плавающей запятой, в том случае, когда два числа имеют общий порядок и код их нормализации должен определяться по тому числу, модуль которого больше. При арифметическом -сдвиге влево сигнал переполнения будет в данном случае возникать по переполнению хотя бы одного числа. Режим формирования кода нормализации числа разрядности п, поступающего с первого входа 9 данных. На вход 11 задания режима двойной точности подается О, код на входе 12 задает режим анализа первого входа данных. Работа устройства аналогична описанной в предьщущем случае с той разницей, что коммутатор 7 постоянно выдает на младшие разряды выхода 16 кода нормализации информацию с выхода 20. Режим формирования кода нормализации числа разрядности п, поступающего со второго входа 10 данных, Дан- Hbrfi режим аналогичен описанному в предьщущем случае с той разницей, что код на входе 12 задает режим анализа второго входа данных, в результате чего коммутатор 7 постоянно выдает на младшие разряды выхода 16 кода нормализации информацию с выхода 21,

Режим формирования кода нормализации числа разрядности 2п, поступающего по входам 9 и 10 данных. На вход 11 задания режима двойной точности подается мультиплексор 27 при зтом пропускает разряд 9j(..

Коммутатор 7 в данном случае пропускает на выход 14 информацию с выхода 20, если сигнал на выходе 8 элемента И 7 равен О, или с выхода 21 в противном случае. Сигнал на выходе 8 элемента И 4 равен I, если код на выходе 20 является единичные и сигнал на третьем выходе 23 узла 1 инвертирования также равен

1465878

. Таким образом, младгаие разря- динен ды кода нормализации определяются по старшей половине числа, если на входе 9 присутствует хотя бы один значащий разряд (единица для числа в прямом коде или ноль для числа В дополнительном коде), или старший разряд 10 младшей половины числа не равен старшему (знаковому) разряду числа; при этом старший разряд кода нормализации равен О. Если же все разряды старшей полорины числа и старший разряд мпадцпей половины чиса равны знаковому, то младшие разря- is ы кода нормализации определяются о младшей половине числа, а старший разряд кода-нормализации равен 1.

10

с втор тора, нен с сравн входом дом эл тора схемы ционн второ треть тора, ра со ,входом ются ройст с чет татор

Формула изобретени.я

тора, о тличающе ее я тем, что, с целью расширения области применения за счет определения кода нормализации и признака переполнения

для пары чисел и для чисел, представ- 45 входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ

денньк с двойной точностью, оно со-г держит вторую схему сравнения и элемент и, причем второй и третий выходы узла инверт|фования соединены соответственно с входом второго шифратора и с первым входом элемента И, вход задания релсима анализа устройства соединен с первым управляющим входом коммутатора, вход задания режима двойной точности устройства сое- gg ходом узла инвертирования,

s

0

0

0

с вторым входом элемента И и с вторым управляющим входом коммутатора, вьгкод первого шифратора соединен с первым входом второй схемы сравнения, с первым информационным входом К1 ммутатора и с третьим входом элемента И, выход второго шифратора соединен с вторым входом второй схемы сравнения и с вторым информационным входом коммутатора, выход второй схемы сравнения соединен с третьим управляющим входом коммутатора, выходы элемента И и коммутатора соединены с вторым информационным ,входом первой схемы сравнения и являются выходом кода нормализации устройства, выход элемента И соединен с четвертым управляющим входом коммутатора,

вход старшего разряда первого инфор- . мационного входа узла инвертирования соединен с первыми входами элементов ИСКЛОЧАЮДЕЕ ИЛИ первой группы, с первым входом элемента ЭКВИВАЛЕНТНОСТЬ и с перВ1)1м информационным входом мультиплексора, входы остальных разрядов первого информационного входа узла инвертирования соединены соответственно с вторыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы, вход старшего разряда второго .информационного Входа узла инвертирования соединен с вторым входом элемента ЭКВИВАЛЕНТНОСТЬ и с вторым информационным входом мультиплексора, входы остальньЕС разрядов второго информационного входа узла инвертирования соединены соответственно с первыми

5

0

0

второй группы, вторые входы которых соединены с выходом мультиплексора, управляюв1ий вход которого является управляюгдам входом узла инвертирования, выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ первой и второй групп являются соответственно первым и вторым выходами узла инвертирования, выход элемента ЭКВИВАЛЕНТНОСТЬ является третьим выСоставитель А, Клюев Редактор И. Сегляник Техред Л.ОлийныкКорректор С. Черни

Заказ 947/49

Тираж 667

ВНШШИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат Патент, г. Ужгород, ул. Гагарина,101

Подписное

| Арифметическое устройство с плавающей точкой | 1985 |

|

SU1259248A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сдвига данных | 1983 |

|

SU1140113A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| . | |||

Авторы

Даты

1989-03-15—Публикация

1987-01-04—Подача