1

(21)4697792 24

(22)29,05„83

(46) 15.05.91. Бюл. № 18 (72) С„В,Ильин и А.В.Юсупов

(53)681.325(088.8)

(56)Авторское свидетельство СССР К 1348822, кл. G 06 F 7/38, 1986.

Мик Дк., Брик Лж. Проектирование микропроцессорных устройств с разряд- но-модульной организацией.т.1 -м.: Мир, 1984, с. 149, рис. 3.19, с„134, рис о 3.12„

(54)РАЗРЯДИО-МОДУЛЬИОК АРИФМПТНЧЕС- КОЕ УСТРОЙСТВО

(57)Изобреч ние относится к вычислительной технике и может быть использовано для выполнения операций сложения-накопления со сдвигом с чнсллгш в дополнительном коде и с числами без знака, в особенности при выполкс нии в виде болымих интегральных схем. Целью изобретения является повышение быстродействия. Разрядно-модульное арифметическое устройство содерясит операционные модули 1 и , регистр 3 состояния, элемент ИСКЛОЧАОДЕЕ ИЛН , перчын и второй коммутаторы 5 и 7, элемент 6 задержки с соогиатствугопси-п- связями о 1 з„Паф-лы, 2 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство с плавающей точкой | 1985 |

|

SU1259248A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| Устройство для умножения | 1976 |

|

SU651341A1 |

| АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1992 |

|

RU2035064C1 |

| Устройство для выполнения арифметических и логических операций над словами | 1978 |

|

SU767757A1 |

| Устройство для выполнения арифметических и логических операций | 1977 |

|

SU674017A2 |

| Устройство для умножения | 1989 |

|

SU1667061A1 |

| Арифметическое устройство | 1971 |

|

SU522497A1 |

| Устройство для обработки информационных полей переменной длины | 1978 |

|

SU767769A1 |

| Устройство для поворота вектора | 1983 |

|

SU1132285A1 |

Л

$6

с «э

л

S

rf-m ш

рггж.

Ь СО

Л дЭ

Изобретение относится к вычислительной технике и может быть применено для выполнения операций сложения-накопления со сдвигом, в особен- ности при выполнении его в виде больших интегральных схем.

Цель изобретения - повышение быстродействия.

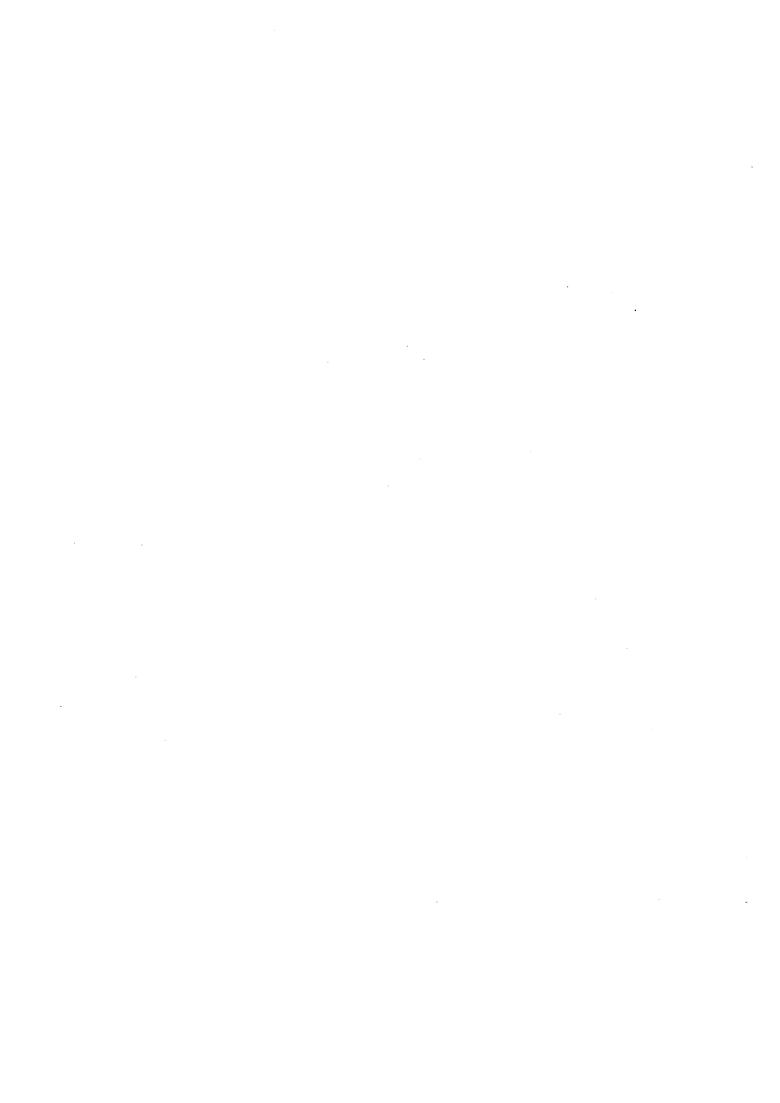

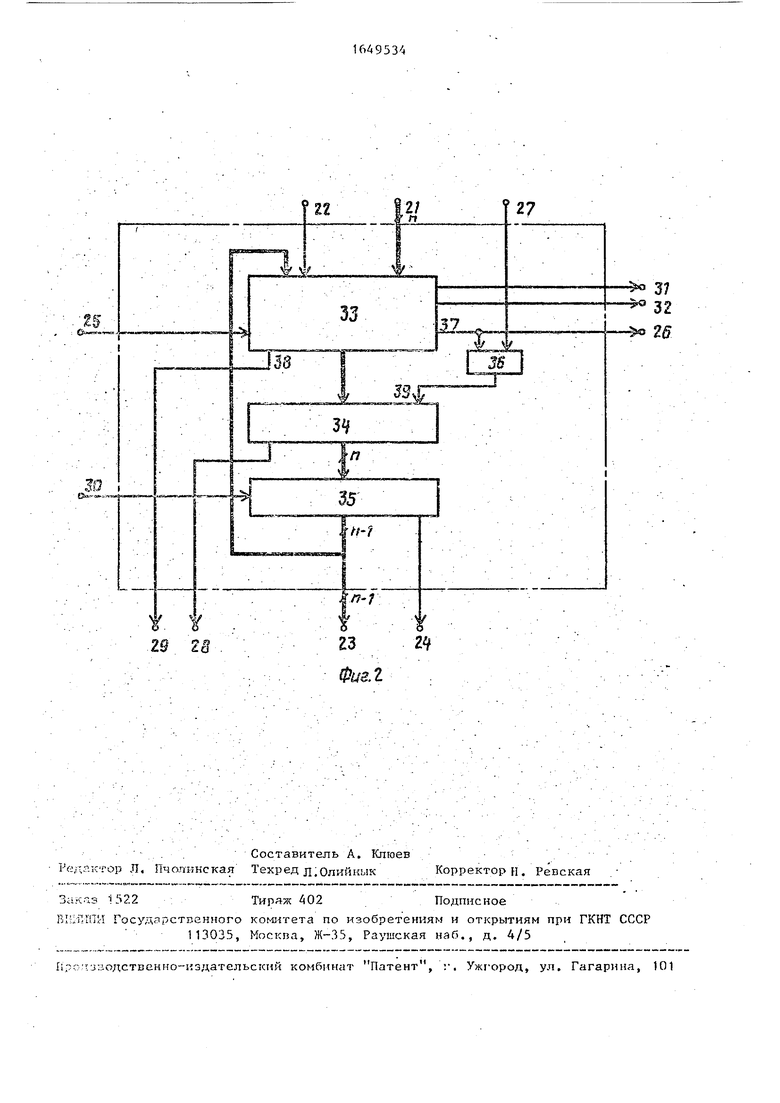

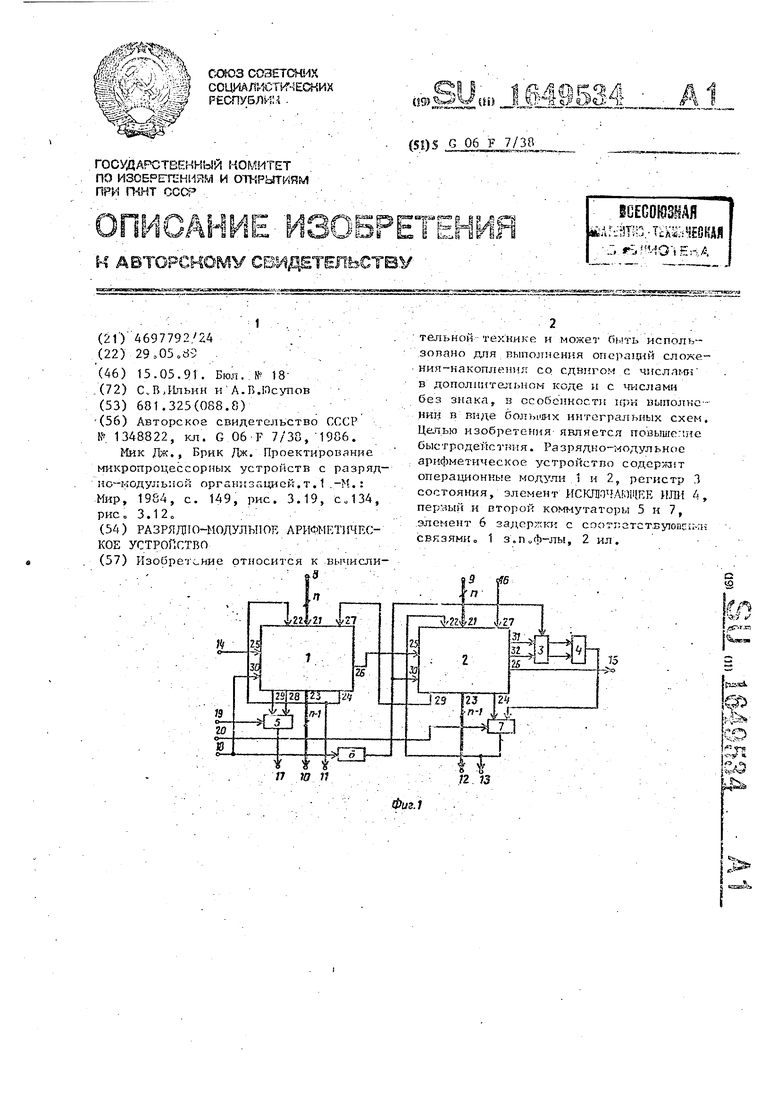

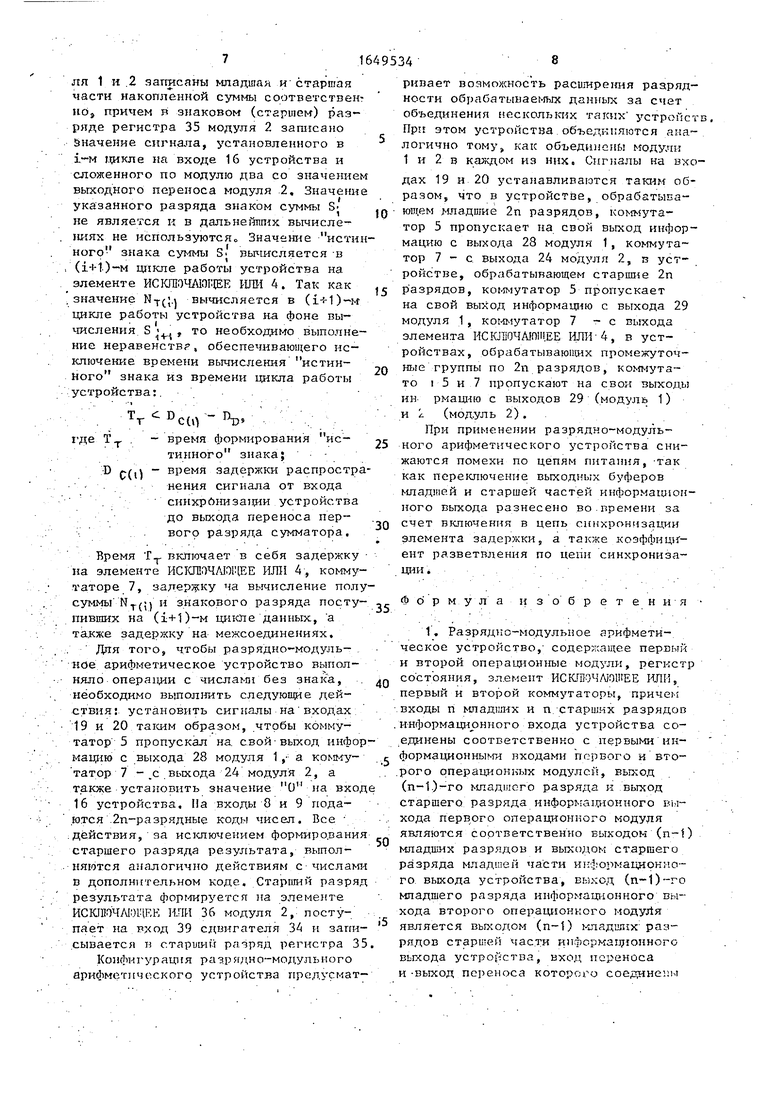

На фиг. 1 представлена структур- ная схема разрядио-модульного арифметического устройства; на фиг. 2 - ,. функциональная схема операционного модуля.

Разрядно-модульное арифметическое устройство содержит первый 1 и второй 2 операционные модули, регистр 3 состояния, элеме.1- ИСКЛЮЧАЮЩЕЕ ИЛИ 4, первый коммутатор 5, элемент 6 задержки, второй коммутатор 7, входы 8 и 9 п младших и п старших разрядов информационного входа устройства, выход 10 (п-1) младших разрядов младшей части информа щонного выхода устройства, выход 11 старшего разряда млад- шей части информационного вькода устройства, выход 12 (п-1) младших разрядов старшей части информационного выхода устройства, выход 13 знакового разряда информационного выхода устрой ства, вход 14 переноса устройства, выход 15 переноса устройства, вход 16 сдвига устройства, выход 17 сдвига устройства, вход 18 синхронизации устройства, первый 19 и второй 20 входы задания режима устройства, первый информационный вход 21 операционного модуля 1 (2), второй информационный вход 22 операционного модуля 1 (2), выход 23 (п-1)-го младшего раз- ряда информационного выхода операционного модуля 1 (2), выход 24 старшего разряда информационного выхода операционного модуля 1 (2), вход 25 переноса операционного модуля 1 (2), выход 26 переноса операционного модуля 1 (2), вход 27 сдвига операционного модуля 1 (2), выход 28 сдвига операционного модуля 1 (2), выход 29 младшего разряда полусуммы операционного модуля 1 (2), вход 30 син- хроиизацин операционного модуля 1 (2) выход 31 знака операционного модуля 1 (2), выход 32 переполнения операционного модуля 1 (2)«

Операционный модуль 1 (2) состоит из комбинационного сумматора 33, комбинационного сдвигателя 34, ре- . гистра 35, элемента ИСЮООЧЛЩЕЕ ИЛИ

Q

5 0 5 .0

5

5

36, выхода 37 переноса комбинационного сумматора 33, выхода 38 младшего разряда полусуммы комбинационного сумматора 33 и последовательный вход 39 комбинационного сдвига- - теля 34.

Разрядно-модульное арифметическое устройство выполняет операции с числами со знаком в дополнительном коде и с числами без знака и работает следующим образом.

Перед началом работы регистры 35 модулей 1 и 2 и регистр 3 состояния устанавливаются в нулевое состояние (вход начальной установки устройства не показан). Дпя работы с числами в дополнительном коде на входы 19 и 20 подаются сигналы таким образом, что первый 5 и второй 7 коммутаторы пр пускают на свои выходы информа- ци с выхода 28 модуля 1 и с выхода ЭЛ1 ента ИСКЛЮЧАЮЩЕЕ ИЛИ 4 соответственно, Числа разрядностью 2п, подлежащие сложению с накоплением и со сдвигом, подаются в дополнительном коде на информационный вход устройства таким образом, что младшие п разрядов поступают по входу 8 в модуль 1, а старшие п разрядов - по входу 9 в модуль 2С Результат операции сложения-накопления со сдвигом выдается в каждом цикле работы устройства на информационный выход, причем младшие п разрядов - на выход 10 и выход 11 (стятэлий разряд младшей части), старшие п разрядов - на выход 12 и выход 13 (знак результата). Выдвиге±емые в каждом цикле младшие разряды выдаются на выход 17 устройства.

В i-м цикле работы двоичное число, подлежащее сложению с накоплением, поступает через вход 21 каждого модуля на вход первого слагаемого сумматора 33. На вход второго слагаемого сумматора 33 поступает накопленное в предыдущих (i-1) циклах работы устройства значение суммы из регистра 35, В модуле 1 старики разряд второго слагаемого поступает через вход 22 с выхода 24 модуля 1. На вход 22 модуля 2 и на выход знака 13 арифметического устройства поступает значение истинного знака суммы S ,.,. Истинный знак вычисляется в i-м шпсле кз элементе ИСКЛЮЧАЮЩЕЕ ИЛИ 4 в соответствии с выражением:

ля 1 и 2 записаны младшая и старшая части накопленной суммы соответственно, причем в знаковом (старшем) разряде регистра 35 модуля 2 записано значение сигнала, установленного в цикле на входе 16 устройства и сложенного по модулю два со значением выходного переноса модуля 2. Значение указанного разряда знаком суммы S- не является к в дальнейших вычислениях не используются Значение истинного знака суммы S вычисляется в (i-i-1)- м цикле работы устройства на элементе ИСКЛЮЧАЮЩЕЕ ИЛИ 4. Так как значение вычисляется в (i-H)-M цикле работы устройства на фоне вы-

числения S

1-Й

то необходимо выполнение неравенств, обеспечивающего исключение времени вычисления истинного знака из времени цикла работы устройства:

де Т.

D

ТГ CDC( -V

- время формирования истинного знака; время задержки распространения сигнала от входа синхронизации устройства до выхода переноса первого разряда сумматора.

С(0

Время Тт включает в себя задержку на элементе ИСКЛЮЧАЮЩЕЕ ИЛИ 4, коммутаторе 7, задержку на вычисление полусуммы Мт(;) и знакового разряда посту- пивших на (1+1)-м цикле данных, а также задержку на межсоединениях.

Для того, чтобы разрядно-модуль- ное арифметическое устройство выполняло операции с числам без знака, необходимо выполнить следующие действия: установить сигналы на входах 19 и 20 таким образом, чтобы коммутатор 5 пропускал на свой выход информацию с выхода 28 модуля 1, а коьму- татор 7 - .с выхода 24 модуля 2, а также установить значение О на вход 16 устройства. На входы 8 и 9 подаются 2п-разрядные коды чисел. Все действия, за исключением формирования старшего разряда результата, выполняются аналогично действиям с числами в дополнительном коде. Старший разряд результата формируется на элементе ИСКЛЮЧАЮЩЕЕ ИЛИ 36 модуля 2, поступает на вход 39 сдвигателя 34 и записывается в старший разряд регистра 35

Конфигурация разрядно-модулыюго арифметического устройства предусмат0

5

0

5

0

5

дд $

ривает возможность расширения разрядности обрабатываемых данных за счет объединения нескольких таких устройств, При этом устройства объединяются аналогично тому, как объединены модули 1 и 2 в каждом из них. Сигналы на входах 19 и 20 устанавливаются таким образом, что в устройстве, обрабатывающем младшие 2п разрядов, коммутатор 5 пропускает на свой выход информацию с выхода 28 модуля 1, коммутатор 7 - с выхода 24 модуля 2, в устройстве, обрабатывающем старшие 2п разрядов, коммутатор 5 пропускает на свой выход информацию с выхода 29 модуля 1, коммутатор 7 - с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 4, в устройствах, обрабатывающих промежуточные группы по 2п разрядов, коммута- то 1 5 и 7 пропускают на свои выходы ин рмацию с выходов 29 (модуль 1) и 1 (модуль 2).

При применении разрядно-модуль- ного арифметического устройства снижаются помехи по цепям питания, так как переключение выходных буферов младшей и старшей частей информационного выхода разнесено во времени за счет включения в цепь синхронизации элемента задержки, а также коэффициент разветвления по цепи синхронизации.

Формула изобретения

соответственно с входом переноса первого операционного модуля н с .выходом переноса второго операционного модуля вход переноса которого соединен с выходом переноса первого операционного модуля, выходы знака и переполнения второго операционного модупя подключены к входам первого и второго разрядов регистра состояния соответственно, вход синхронизации первого операционного модуля подключен ко входу синхронизации устройства, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с первым информационным входом второго коммутатора, отличающееся тем, что, с целью повышения быстродействия, оно содержит элемент задержки, причем выходы сдвига и младшего разряда полусум ЕЫ первого операционного модуля подключены соответственно к первому и второму информационным входам первого коммутатора, управляющий вход которого соединен с первым входом задания режима устройства, а выход являтся выходом сдвига устройства, вход сдвига второго операционного модуля является входом сдвига устройства, вход элемента задержки подключен ко входу синхронизации устройства, выход элемента задержки подключен к входу синхронизации второго операционного модуля и к входу разрешения записи регистра состояния, первый и второй входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ под- ключены к выходам первого и второго разрядов регистра состояния соответственно , выход старшего разряда информационного выхода аторого операционного модуля и второй вход задания режима устройства соединены соответственно со вторым информационным и управляющим входами второго коммутатора, выход которого является выходом знакового разряда информационного выхода устройства и соединен с вторым информационным входом второго операционного модуля, выход старшего разряда информационного выхода первого операционного модуля со- единен с вторым информационным входом первого операционного модуля, выход младшего разряда полусуммы

,-

to

15

20

, 2535 5030

40

45

второго операционного модуля соединен с входом сдвига первого операционного модуля о

2, Устройство по п. 1, о т л и- ч а ю щ е с с я тем, что операционный модуль содержит комбинационный сумматор, комбинационный сдвигатель, регистр и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, причем иход первого слагаемого комбинационного сумматора подключен к первому икформаципнному входу операционного модуля, выход суммы комбинационного сумматора подключен к параллельному входу комбинационного сдвигателя, параллельный выход которого подключен к информационному входу регистра, выходы ()-го младшего разряда которого соединены с входами соответствующих разрядов входа второго слагаемого комбинационного сумматора и являются выходом (n-l)-ro младшего разряда информационного выхода операционного модуля, выход старшего разряда регистра является выходом старшего разряда информационного выхода операционного модуля, иход и выход переноса комбинационного сумматора подключены к входу и выходу переноса операционного модуля соответственно, выходы старшего разряда суммы и переполнения комбинационного сумматора подключены к выходам знака и переполнения операционного модуля соответствешю, последовательный выход комбинационного сдвигателя подключен к выходу сдвига операционного модуля, вход разрешения записи регистра подключен к входу синхронизации операционного модуля, первый и второй входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ подключен к выходу переноса комбинационного сумматора и ко входу сдвига операционного модуля соответственно, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ подключен к последовательному входу комбинационного сдвигателя, вход старшего разряда входа второго слагаемого комбинационного сумматоря подключен к второму информационному входу операционного модуля, выход младшего разряда полусуммы комбинационного сумматора яьляется соотиет- ,т1К выходом оперзционн 1го модуля.

20 2В

гъ гц Фиг.г

Авторы

Даты

1991-05-15—Публикация

1989-05-29—Подача