Оч (Л

10

о

Јь

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор случайного процесса | 1983 |

|

SU1111159A1 |

| Генератор случайного процесса | 1983 |

|

SU1100622A1 |

| Генератор случайного процесса | 1985 |

|

SU1739374A1 |

| Формирователь сложного сигнала с частотной и частотно-фазовой манипуляцией | 1982 |

|

SU1136323A1 |

| ИМИТАТОР ДЖИТТЕРА | 2005 |

|

RU2303852C2 |

| Умножитель частоты | 1979 |

|

SU807322A1 |

| Устройство для выполнения преобразования Фурье | 1986 |

|

SU1332331A1 |

| ДЕЛИТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2249846C1 |

| Цифровой синтезатор частот | 1989 |

|

SU1691926A1 |

| Генератор многомерных случайных величин | 1981 |

|

SU966692A1 |

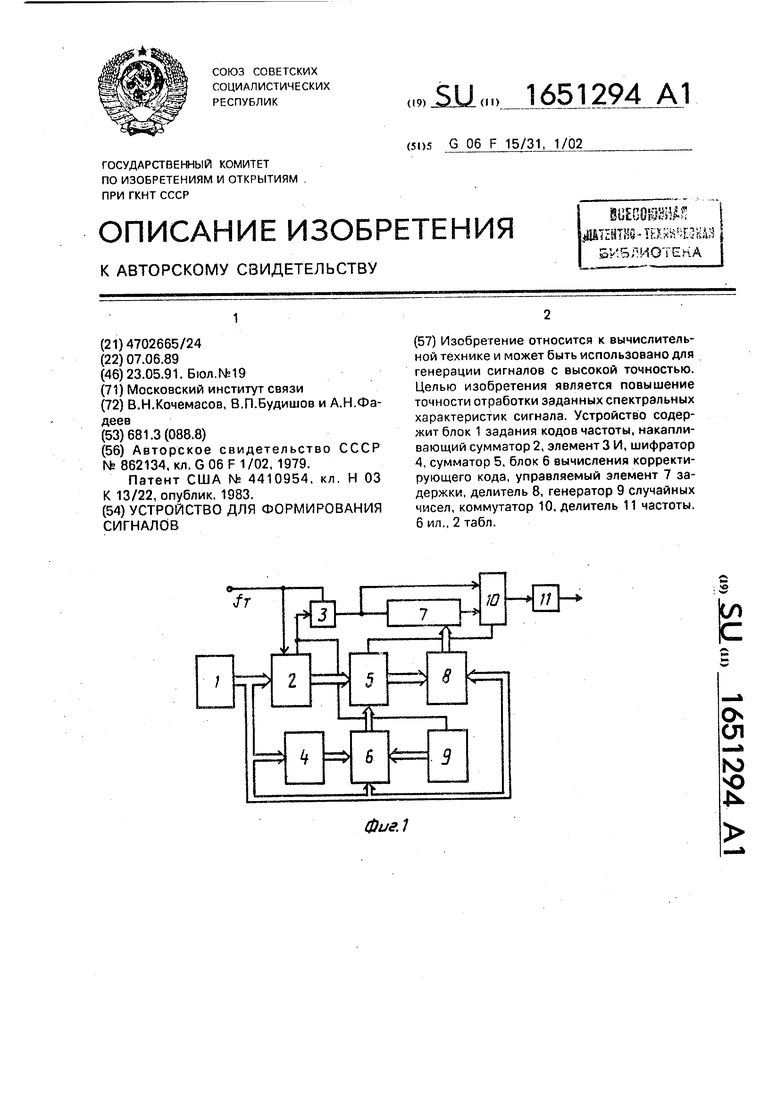

Изобретение относится к вычислительной технике и может быть использовано для генерации сигналов с высокой точностью. Целью изобретения является повышение точности отработки заданных спектральных характеристик сигнала. Устройство содержит блок 1 задания кодов частоты, накапливающий сумматор 2, элемент 3 И, шифратор 4, сумматор 5, блок 6 вычисления корректирующего кода, управляемый элемент 7 задержки, делитель 8, генератор 9 случайных чисел, коммутатор 10, делитель 11 частоты. 6 ил., 2 табл.

Фие.1

Изобретение относится к вычислительной технике и может быть использовано для генерации сигналов с высокой точностью.

Целью изобретения является повышение точности отработки заданных спектральных характеристик сигнала.

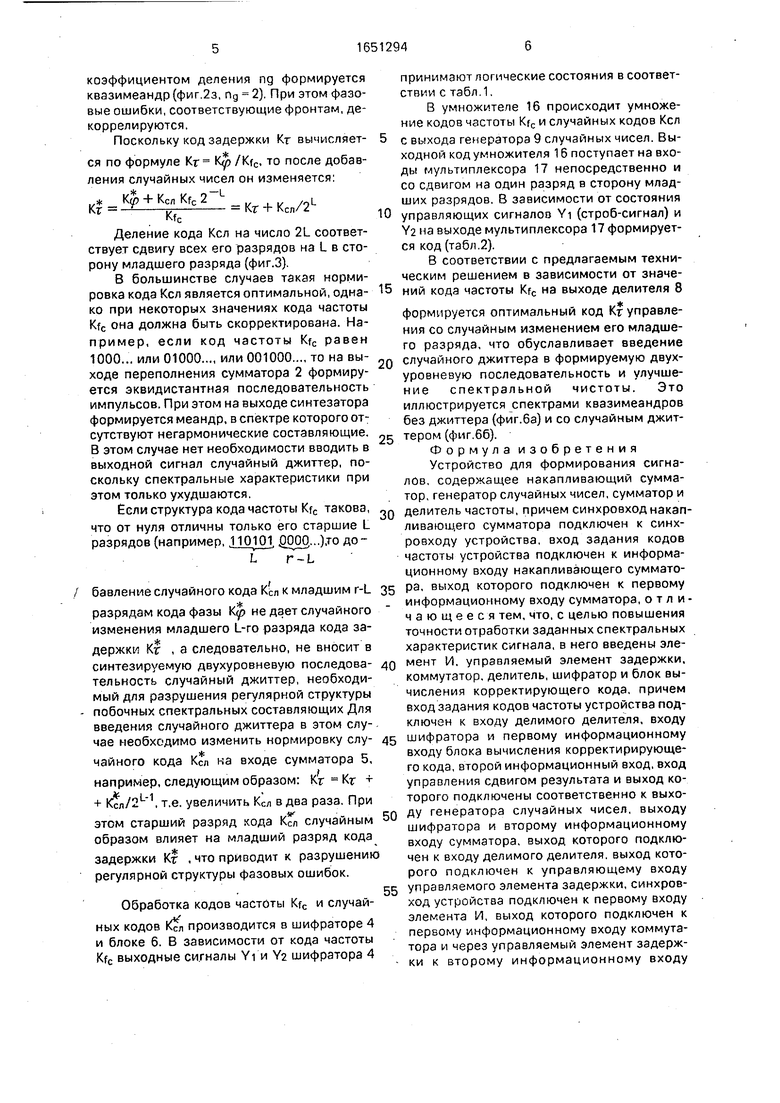

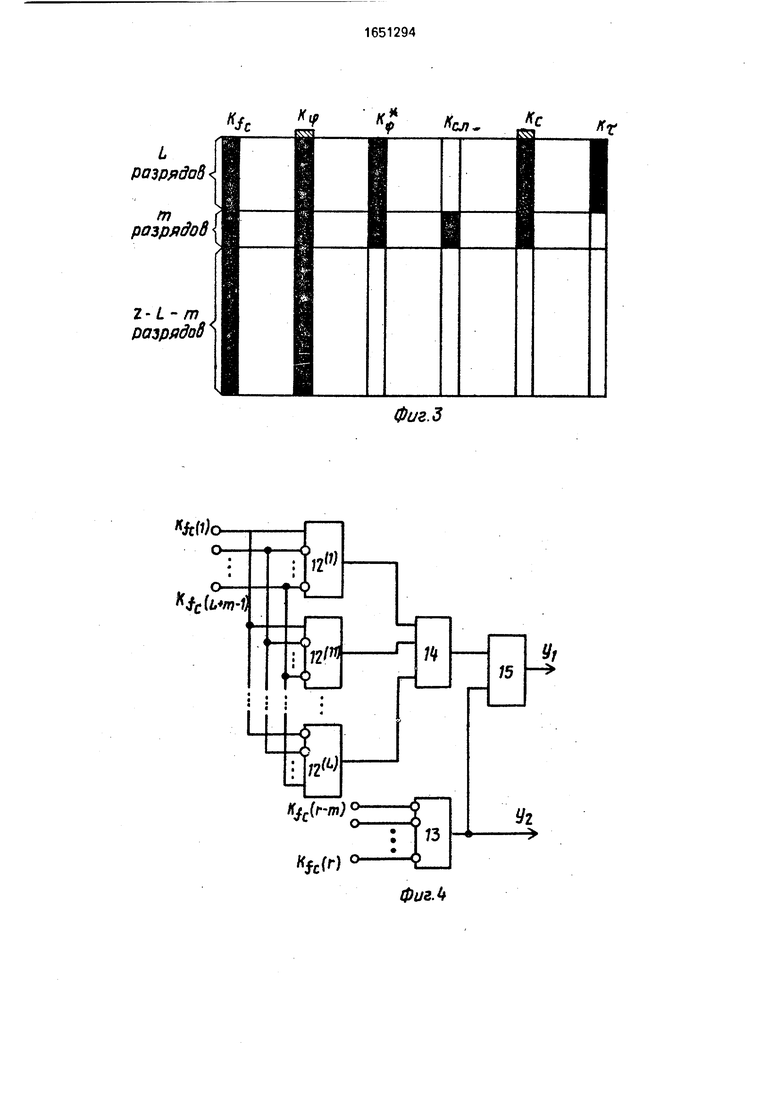

На фиг.1 изображена функциональная схема устройства; на фиг.2 и 3 - диаграммы, поясняющие принцип работы устройства: на фиг.4 - схема шифратора; на фиг.5 - схема блока вычисления корректирующего кода; на фиг,6 - примеры реализуемых спектров сигналов.

Устройство содержит блок 1 задания кодов частоты, накапливающий сумматор 2, элемент И 3, шифратор 4, сумматор 5, блок 6 вычисления корректирующего кода, управляемый элемент 7 задержки, делитель 8, генератор 9 случайных чисел, коммутатор 10 и делитель 11 частоты.

Шифратор 4 содержит элементы И 12 и 13, элемент ИЛИ 14 и элемент И 15.

Блок вычисления корректирующего кода содержит умножитель 16 и мультиплексор 17.

Устройство работает следующим образом.

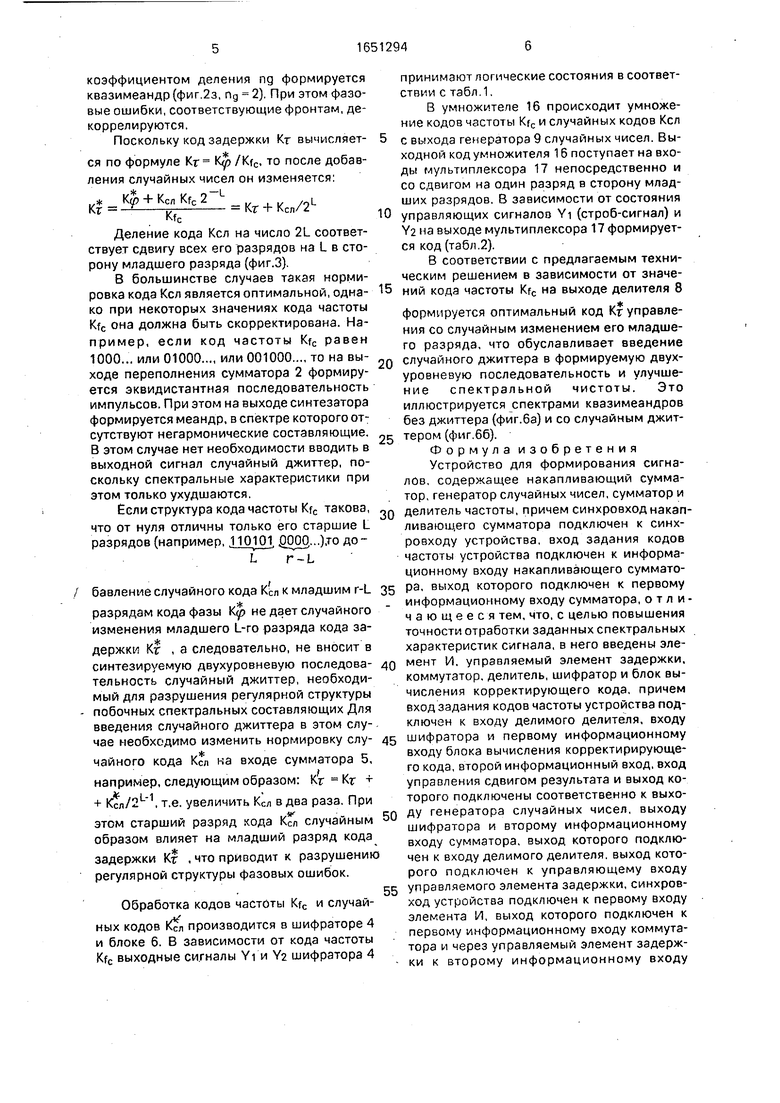

В блоке 1 формируется г-разрядный двоичный код Kfc синтезируемой частоты fc frKfc/ngM, где ng 2 - коэффициент деления делителя 11; М 2Г; fr - тактовая частота. Цифровой синтез сигналов основан на вычислении кодов фазы (I) сумматора 2 в дискретные моменты времени ti i.T, где I 0,1,2,...; Т 1 /fr - длительность тактового интервала. В моменты переполнения сумматора 2 на его выходе переполнения возникают импульсы, которые после прохождения через делитель 11 преобразуются в квазимеандр с частотой следования fc. В общем случае, когда отношение M/Kfc не является целым числом, временные ошибки положения фронтов сформированного квазимеандра относительно фронтов идеального меандра могут достигать длительности тактового интервала Т, а фазовые ошибки- 180°.

Фазовые ошибки приводят к возникно-, вению нежелательных дискретных побочных составляющих высокого уровня. Для их уменьшения применяется компенсация фазовых ошибок с помощью управляемого элемента 7 задержки с разрешающей способностью го T/2L, где L - число управля- ющих входов, и вводится случайный джиггер с помощью генератора 9 случайных чисел. Этот процесс поясняется временными диаграммами, представленными на фиг.2.

Если на тактовый вход сумматора 2 подается тактовый сигнал (фиг.2а), а на его входы - код частоты Kfc (в примере M/Kfc 8/3), то код фазы К р () изменяется по ступенчатому закону (фиг.2б). В моменты переполнения сумматора 2 на его выходе переполнения возникают импульсы (фиг.2в), временное положение которых в общем случае отличается от положения фронтов эквивалентной последовательности импульсов с периодом, равным полупериоду синтезируемого колебания Тс/2 ПдМ/2Кгстт(фиг.2г). Неравномерность формируемых импульсов переполнения эквивалентна наличию паразитной фазовой модуляции, которая приводит к появлению в спектре сигнала побочных дискретных составляющих.

Для повышения диапазона синтезируе- мых частот импульсы переполнения строби- руются сигналом эталонного генератора и с выхода элемента И 3 поступают на вход управляемого элемента 7 задержки, который задерживает входной сигнал на величи5 ну г Т.2 L( 1-Кт). К$ /Kfc - код

.Ј

задержки, вычисляемый в делителе 8; К - значение кода фазы в моменты переполнения сумматора 2. Для дополнительного

5

0

уменьшения спектральной плотности дискретных побочных составляющих вводится случайный джиттер (дрожание) импульсов, поступающих на вход делителя 11. Генератор 9, тактируемый импульсами переполнения сумматора 2, вырабатывает последовательность случайных чисел КСл (фиг.2д). Эта последовательность поступает на вход блока 6 и нормируется в соответствии со следующим алгоритмом: к сл

K.Kfc.

В зависимости от значения кода частоты Kfc в шифраторе 4 вырабатываются управляющие сигналы для блока 6, которые

обеспечивают необходимую нормировку случайных чисел, такую что ошибки в вычислении кода задержки Кг не превышают весового значения младшего разряда (фиг.2е, утолщенная линия означает случайное значение (К т . Если сумматор 5 пере- полняется (код Кс 2L+m), то это свидетельствует о том, что стробированный импульс переполнения должен поступать на вход делителя 11 беззадержки. Дляобеспеченил такого режима служит коммутатор 10. Таким образом осуществляется выравнивание стробированных импульсов переполнения при одновременном введении фазового джиттера (фиг.2ж). После прохождения этих импульсов через делитель 11с

коэффициентом деления ng формируется квазимеандр (фиг.2з, ng 2). При этом фазовые ошибки, соответствующие фронтам, де- коррелируются.

Поскольку код задержки Кг вычисляется по формуле Кг Ку /Kfc, то после добавления случайных чисел он изменяется:

„ K$ + KcnKfc2 L,

Кг -2гх-- Кг + Ксл/2и

I4fc

20

25

30

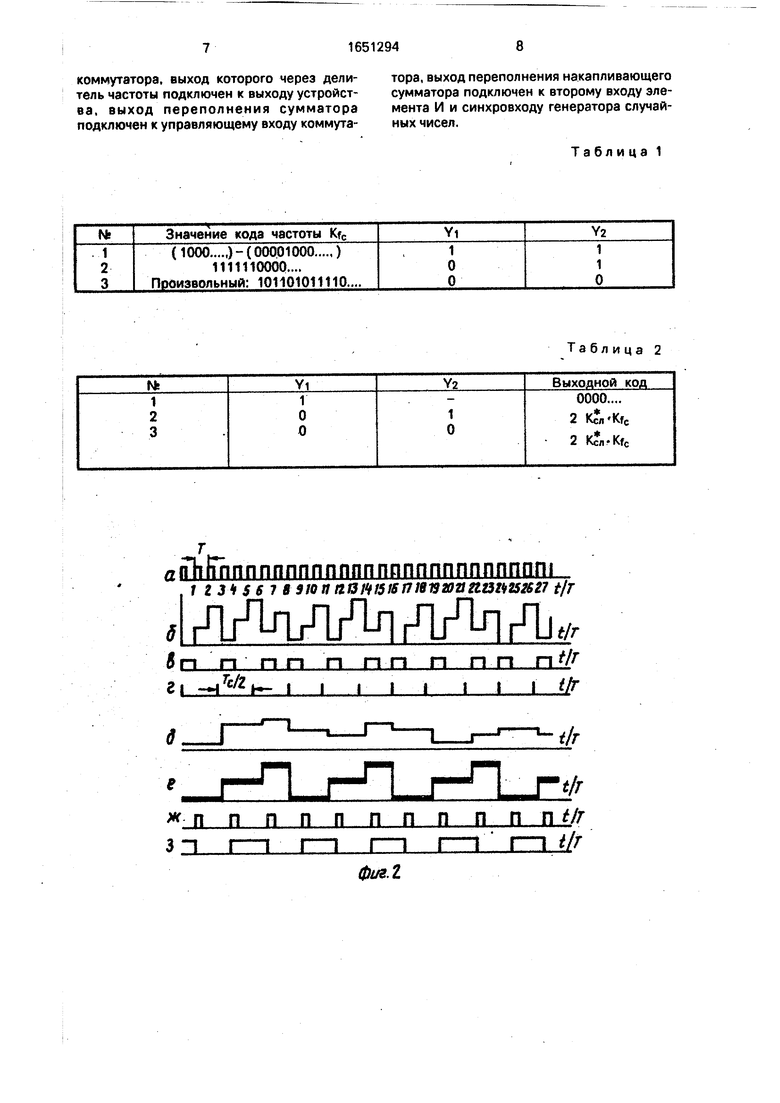

Деление кода Ксл на число 2L соответствует сдвигу всех его разрядов на L в сторону младшего разряда (фиг.З)

В большинстве случаев такая нормировка кода Ксл является оптимальной, одна- 15 ко при некоторых значениях кода частоты Kfc она должна быть скорректирована. Например, если код частоты Kfc равен

Если структура кода частоты Kfc такова, что от нуля отличны только его старшие L разрядов (например, ЦОДОД ЩХХ)...),то доL r-L

бавление случайного кода Ксл к младшим r-L 35

разрядам кода фазы не дает случайного

изменения младшего L-го разряда кода за,. держки Кг , а следовательно, не вносит в

синтезируемую двухуровневую последова- 40 тельность случайный джиттер, необходимый для разрушения регулярной структуры побочных спектральных составляющих Для введения случайного джиттера в этом случае необходимо изменить нормировку слу- 45

f

чайного кода Ксл на входе сумматора 5, например, следующим образом: Кг Кг « + Ксл/21 1. т.е. увеличить Ксл в два раза. При этом старший разряд кода К, случайным 50 образом влияет на младший разряд кода задержки Кг , что приводит к разрушению регулярной структуры фазовых ошибок.

55

Обработка кодов частоты Kfc и случайных кодов Ксл производится в шифраторе 4 и блоке 6. В зависимости от кода частоты Kfc выходные сигналы YI и Y2 шифратора 4

0

0

5

0

5

5

0 5

0

5

принимают логические состояния в соответствии с табл 1,

В умножителе 16 происходит умножение кодов частоты Kfc и случайных кодов Ксл с выхода генератора 9 случайных чисел. Выходной код умножителя 16 поступает на входы мультиплексора 17 непосредственно и со сдвигом на один разряд в сторону младших разрядов. В зависимости от состояния управляющих сигналов YI (строб-сигнал) и Ya на выходе мультиплексора 17 формируется код (табл.2).

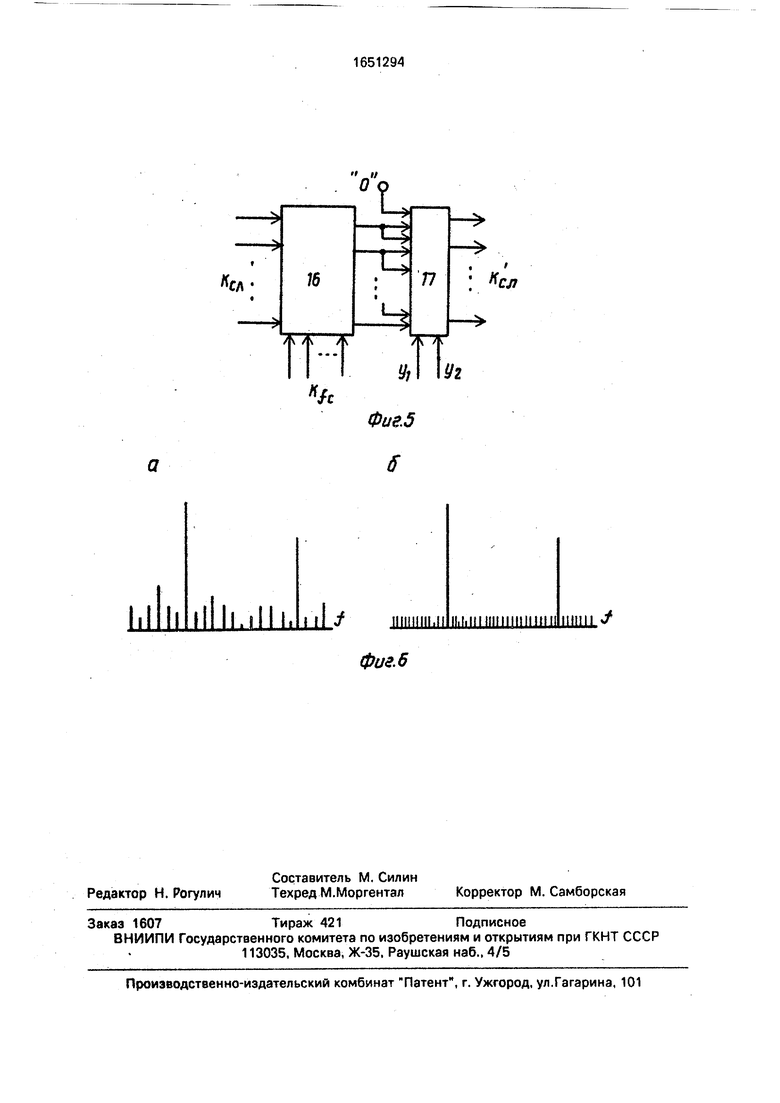

В соответствии с предлагаемым техническим решением в зависимости от значений кода частоты Kfc на выходе делителя 8

формируется оптимальный код К управления со случайным изменением его младшего разряда, что обуславливает введение случайного джиттера в формируемую двухуровневую последовательность и улучшение спектральной чистоты. Это иллюстрируется спектрами квазимеандров без джиттера (фиг.ба) и со случайным джит- тером (фиг.бб).

Формула изобретения Устройство для формирования сигналов, содержащее накапливающий сумматор, генератор случайных чисел, сумматор и делитель частоты, причем синхровход накапливающего сумматора подключен к синх- ровходу устройства, вход задания кодов частоты устройства подключен к информационному входу накапливающего сумматора, выход которого подключен к первому информационному входу сумматора, отличающееся тем, что, с целью повышения точности отработки заданных спектральных характеристик сигнала, в него введены элемент И, управляемый элемент задержки, коммутатор, делитель, шифратор и блок вычисления корректирующего кода, причем вход задания кодов частоты устройства подключен к входу делимого делителя, входу шифратора и первому информационному входу блока вычисления корректирирующе- го кода, второй информационный вход, вход управления сдвигом результата и выход которого подключены соответственно к выходу генератора случайных чисел, выходу шифратора и второму информационному входу сумматора, выход которого подключен к входу делимого делителя, выход которого подключен к управляющему входу управляемого элемента задержки, синхровход устройства подключен к первому входу элемента И, выход которого подключен к первому информационному входу коммутатора и через управляемый элемент задержки к второму информационному входу

коммутатора, выход которого через делитель частоты подключен к выходу устройства, выход переполнения сумматора подключен к управляющему входу коммуталпЪ пппппппппппппппппппппппт

1 г зч s 6 7 8 зю л лв PUS is п ten яя&яп&хг tfT

иЛДоЛгОл лДл Л

t/r

5 п п п п п п п п .. п п п t/r г -чГс/2н- i i I I I I i tlr

е

пп

ппппппппп /г

tlr

3 П 11 I1

тора, выход переполнения накапливающего сумматора подключен к второму входу элемента И и синхровходу генератора случайных чисел.

Таблица 1

Таблица 2

t/r

фиг.1

к

разрядов

т , л разрядов

г-L- т разрядов

кМ)о

v

Kjc(r-m) fcW

сл- JLC

к

Фиг.З

фиг А

СЛ

тн д„

«h

till..III.

iibf

СЛ

Фие.5

inniini.ii

ii.uiimmiiiiiiiiii

шип %/

фиг. 6

| Устройство для формирования импульсных последовательностей с заданным законом изменения фазы | 1979 |

|

SU862134A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Патент США № 4410954, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Гребенчатая передача | 1916 |

|

SU1983A1 |

Авторы

Даты

1991-05-23—Публикация

1989-06-07—Подача