/6 о

VJ

о

СП

Изобретение относится к вычислительной технике и может быть применено в высокопроизводительных систамах обработки информации.

Цепь изобретения - сокращение аппаратурных затрат,

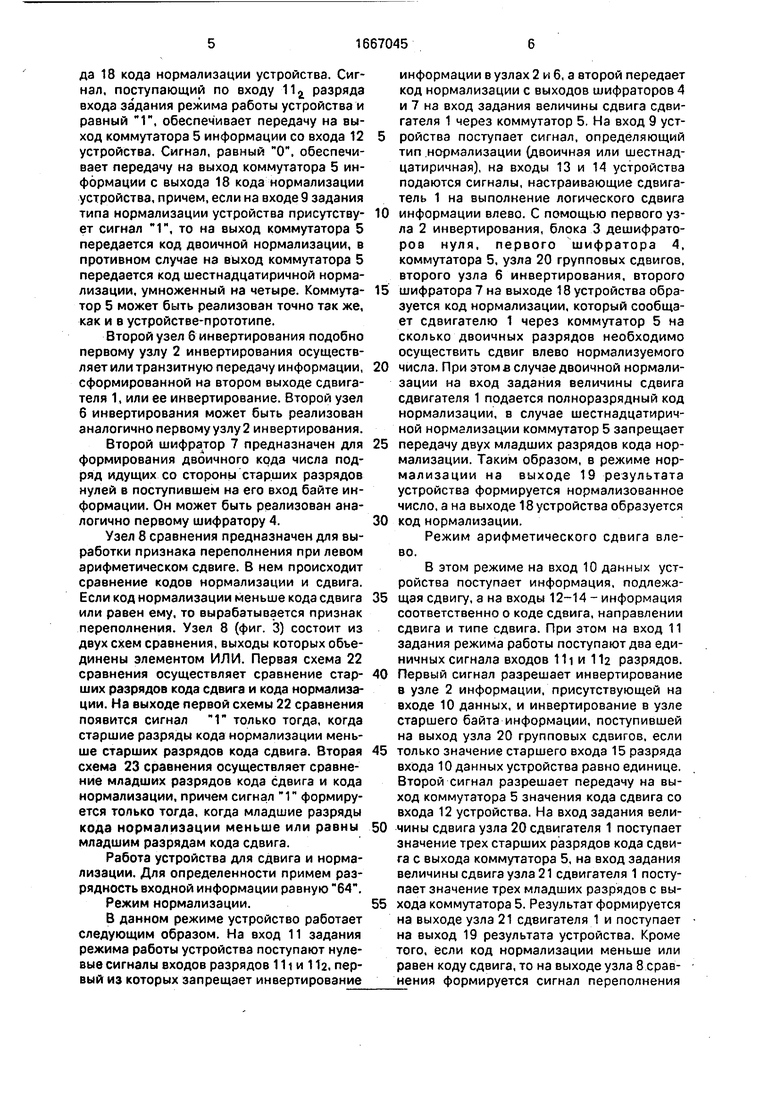

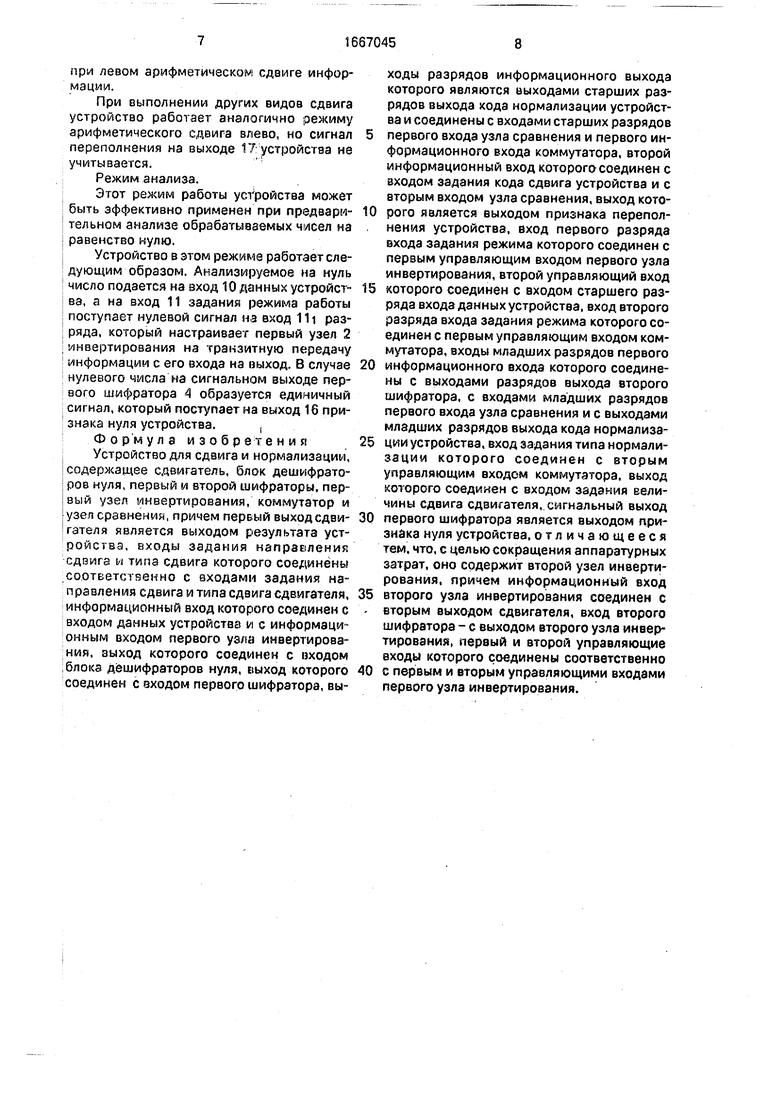

На фиг. 1 приведена сгрукгурнач схема устройства для сдвига и нормализадии; на фиг. ч - структурная схема сдвига геля; на фиг. 3 - структурная схема узла сравнения.

Устройство содержит сдвигатель 1, первый узел 2 инвертирования, блок 3 дешиф- раюров нуля, первый шифратор 4, коммутатор 5, второй узел 5 инвертирования, второй шифратор 7, узел 8 сравнения, вход 9 задания типа нормализации устройства, вход 10 данных устройства, вход 11 задания режиме устройства, входы 111 и 11а первого и второго разрядов входа 11 зада- чия режима устройства, вход 12 задания кода сдвига устройства, вход 13 задания йрпрззления сдвига устройства, вход 14 задание типа сдвига устройс ва, вход 15 стар- шего разряда входа 10 данных устройства, выхо/i 16 признака нуля устройства, выход Т7 признака переполнения устройства, выход 18 .coqa нормализации устройства, выход 1у р Э-зупьтзта устройство.

Сив гатель 1 содержит узел 20 групповых сдвигов, узел 21 разрядных сдвигов, причем информационный входсдвигателя 1 соединен информационным входом узла °0 i р ппозых сдвигов, выход которого является -- -injfvi выходом сдвига геля 1 и соеди- не, с информационным входов узла 21 разрядных сдвигов, выход которого являет- сг мерным выходом сДБИгбтел.ч 1, входы зама.{-.,- направления и типа сдеига которого . с соответствующими входами узла 20 . пупповых сдвигов н узла 21 разрядные : эигор, входы старших и младших раз- рядтг вчода задания величины сдвига ГОЕМГЗТРМЯ соединены соответственно с входят. ре,: рядов входов задания велмчи- ны сдч-: з у -ьш 20 групповых сдвигов и узла Г pr..;x сдвигов.

Уз- л 3 сравнения содержит первую м стору.-о 22 и 23 сравнения и элемент ИЛИ 24, лричем входы старших разрядов первого и ыорого входов уз па 8 сравнения соединены JCCT38TCTE8HHO с; входами р;эз- psAOii первого м второго входов схемы 22 г;рззнен / я, выход которой соединен с пер- йым входом элемента ИЛИ 24, выход которого :;влязтея выходом узла 8 сразнения, oxo/ibi пл- дших разрядов первого и второго в-шдоз которого соединены состветствзнно с ехо/оми разрядов первого и второго вхо- U-,o 2Г( срарньк я, 8,ход которой со- ед| не1 f. тиоым входом элоиента ИЛИ 24.

Рассмотрим функциональное назначение и реализацию основных узлов и блоков устройства для сдвига и нормализации в предположении, что выполняются сдвиги

64 разрядных чисел.

Сдвигатель 1 предназначен для быстрого выполнения разных видов сдвига информации, поступающей на вход 10 данных устройства. Узел 20 групповых сдвигов осу0 ществляет межбайтные сдвиги поступающей на его входы информации по значению старших разрядов выхода коммутатора 5 в соответствии с направлением и типом сдвига, установленными по входам 13 и 14 зада5 ния направления и типа сдвига устройства, Узел 21 разрядных сдвигов осуществляет сдвиг в пределах байта информации, поступающей на его вход по значению младших разрядов выхода коммутатора 5 в соответ0 ствии с направлением и типом сдвига, установленными по входам 13 и 14 направления и типа сдвига устройства. Как и в устройстве-прототипе, сдвигатель 1 является одно- тактным.

5 Первый узел 2 инвертирования осуществляет илм транзитную передачу информации со входа 10 данных устройства, или же инвертирование. Информация инвертируется при выполнении в устройстве арифме0 тического сдвига влево (первый разряд 111 входа 11 задания режима установлен в единицу) отрицательного числа (старший разряд 15 входа 10 данных установлен в единицу), в противном случае она передает5 ся через узел 2 транзитом. Первый узел 2 - инвертирования может быть реализован на элементах ИСКЛЮЧАЮЩЕЕ ИЛИ, управляемых элементом И.

Блок 3 дешифраторов нуля служит для

0 побайтного анализа числа на нуль и может быть построен на восьмивходовых элементах ИЛИ.

Первый шифратор 4 является приоритетным и предназначен для формирования

5 двоичного кода числа подряд идущих со стороны старших разрядов нулей в его входной информации. Фактически он указывает двоичный код числа подряд идущих со стороны старших байтов нулевых байтов информа0 ции, поступающей на вход 10 устройства. При нулевой информации на входе 10 данных на сигнальном выходе шифратора 4 формируется сигнал, поступающей на выход 16 признака нуля устройства. Первый

5 шифратор 4 может быть реализован точно так же, как и в устройстве-прототипе.

Коммутатор 5 осуществляет передачу на вход задания величины сдвига сдвигателя 1 или информации с входа 12 задания кода сдвига устройства, или информации с выхода 18 кода нормализации устройства. Сигнал, поступающий по входу 11j, разряда входа задания режима работы устройства и равный Г, обеспечивает передачу на выход коммутатора 5 информации со входа 12 устройства. Сигнал, равный О, обеспечивает передачу на выход коммутатора 5 информации с выхода 18 кода нормализации устройства, причем, если на входе 9 задания типа нормализации устройства присутствует сигнал 1, то на выход коммутатора 5 передается код двоичной нормализации, в противном случае на выход коммутатора 5 передается код шестнадцатиричной нормализации, умноженный на четыре. Коммутатор 5 может быть реализован точно так же, как и в устройстве-прототипе.

Второй узел б инвертирования подобно первому узлу 2 инвертирования осуществляет или транзитную передачу информации, сформированной на втором выходе сдвига- теля 1, или ее инвертирование. Второй узел 6 инвертирования может быть реализован аналогично первому узлу 2 инвертирования.

Второй шифратор 7 предназначен для формирования двоичного кода числа подряд идущих со стороны старших разрядов нулей в поступившем на его вход байте информации. Он может быть реализован аналогично первому шифратору 4.

Узел 8 сравнения предназначен для выработки признака переполнения при левом арифметическом сдвиге. В нем происходит сравнение кодов нормализации и сдвига. Если код нормализации меньше кода сдвига или равен ему, то вырабатывается признак переполнения. Узел 8 (фиг. 3) состоит из двух схем сравнения, выходы которых объединены элементом ИЛИ. Первая схема 22 сравнения осуществляет сравнение старших разрядов кода сдвига и кода нормализации. На выходе первой схемы 22 сравнения появится сигнал 1 только тогда, когда старшие разряды кода нормализации меньше старших разрядов кода сдвига. Вторая схема 23 сравнения осуществляет сравнение младших разрядов кода сдвига и кода нормализации, причем сигнал Г формируется только тогда, когда младшие разряды кода нормализации меньше или равны младшим разрядам кода сдвига.

Работа устройства для сдвига и нормализации. Для определенности примем разрядность входной информации равную 64.

Режим нормализации.

В данном режиме устройство работает следующим образом. На вход 11 задания режима работы устройства поступают нулевые сигналы входов разрядов 111 и 112. первый из которых запрещает инвертирование

информации в узлах 2 и 6, а второй передает код нормализации с выходов шифраторов 4 и 7 на вход задания величины сдвига сдви- гателя 1 через коммутатор 5, На вход 9 уст- 5 ройства поступает сигнал, определяющий тип нормализации (двоичная или шестнадцатиричная), на входы 13 и 14 устройства подаются сигналы, настраивающие сдвига- тель 1 на выполнение логического сдвига

0 информации влево. С помощью первого узла 2 инвертирования, блока 3 дешифраторов нуля, первого шифратора 4, коммутатора 5, узла 20 групповых сдвигов. второго узла б инвертирования, второго

5 шифратора 7 на выходе 18 устройства образуется код нормализации, который сообщает сдвигателю 1 через коммутатор 5 на сколько двоичных разрядов необходимо осуществить сдвиг влево нормализуемого

0 числа. При этом в случае двоичной нормализации на вход задания величины сдвига сдвигателя 1 подается полноразрядный код нормализации, в случае шестнадцатиричной нормализации коммутатор 5 запрещает

5 передачу двух младших разрядов кода нормализации. Таким образом, в режиме нормализации на выходе 19 результата устройства формируется нормализованное число, а на выходе 18 устройства образуется

0 код нормализации.

Режим арифметического сдвига влево.

В этом режиме на вход 10 данных устройства поступает информация, подлежа5 щая сдвигу, а на входы 12-14 - информация соответственно о коде сдвига, направлении сдвига и типе сдвига. При этом на вход 11 задания режима работы поступают два единичных сигнала входов 11i и 112 разрядов.

0 Первый сигнал разрешает инвертирование в узле 2 информации, присутствующей на входе 10 данных, и инвертирование в узле старшего байта информации, поступившей на выход узла 20 групповых сдвигов, если

5 только значение старшего входа 15 разряда входа 10 данных устройства равно единице. Второй сигнал разрешает передачу на выход коммутатора 5 значения кода сдвига со входа 12 устройства. На вход задания вели0 чины сдвига узла 20 сдвигателя 1 поступает значение трех старших разрядов кода сдвига с выхода коммутатора 5, на вход задания величины сдвига узла 21 сдвигателя 1 поступает значение трех младших разрядов с вы5 хода коммутатора 5. Результат формируется на выходе узла 21 сдвигателя 1 и поступает на выход 19 результата устройства. Кроме того, если код нормализации меньше или равен коду сдвига, то на выходе узла 8 сравнения формируется сигнал переполнения

при левом арифметическом сдвиге информации.

При выполнении других видов сдвига устройство работает аналогично режиму арифметического сдвига влево, но сигнал переполнения на выходе 17 устройства не учитывается.

Режим анализа.

Этот режим работы устройства может быть эффективно применен при предварительном анализе обрабатываемых чмсел на равенство нулю.

Устройство в этом режиме работает следующим образом. Анализируемое на куль число подается на вход 10 данных устройства, а на вход 11 задания режима работы поступает нулевой сигнал из вход 11i разряда, который настраивает первый узел 2 инвертирования на транзитную передачу информации с его входа на выход. В случае нулевого числа на сигнальном выходе первого шифратора 4 образуется единичный сигнал, который поступает на выход 16 признака нуля устройства,,

Формула изобретений

Устройство для сдвига и нормализации, содержащее сдвигатель, блок дешифраторов нуля, первый м второй шифраторы, пер- | вый узел инвертирования, коммутатор и узел сравнения, причем первый выход сдаи- гателя является выходом результата устройства, входы задания направлений сдвига м типа сдвига которого соединены соответственно с входами задания на- п равления сдвига и типа сдвига сдвигателя, информационный вход которого соединен с входом данных устройства и с информационным входом первого узла инвертирования, выход которого соединен с входом блока дешифраторов нуля, выход которого соединен с входом первого шифратора, выходы разрядов информационного выхода которого являются выходами старших разрядов выхода кода нормализации устройства и соединены с входами старших разрядов

первого входа узла сравнения и первого информационного входа коммутатора, второй информационный вход которого соединен с входом задания кода сдвига устройства и с вторым входом узла сравнения, выход которого является выходом признака переполнения устройства, вход первого разряда входа задания режима которого соединен с первым управляющим входом первого узла инвертирования, второй управляющий вход

которого соединен с входом старшего разряда входа данных устройства, вход второго разряда входа задания режима которого соединен с первым управляющим входом коммутатора, входы младших разрядов первого

информационного входа которого соединены с выходами разрядов выхода второго шифратора, с входами младших разрядов первого входа узла сравнения и с выходами младших разрядов выхода кода нормализации устройства, вход задания типа нормали- зации которого соединен с вторым управляющим входом коммутатора, выход которого соединен с входом задания величины сдвига сдвигателя, сигнальный выход

первого шифратора является выходом признака нуля устройства, отличающееся тем, что, с целью сокращения аппаратурных затрат, оно содержит второй узел инвертирования, причем информационный вход

второго узла инвертирования соединен с вторым выходом сдвигателя, вход второго шифратора - с выходом второго узла инвертирования, первый и второй управляющие входы которого соединены соответственно

с первым и вторым управляющими входами первого узла инвертирования.

Фиг. 2 is

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сдвига данных | 1983 |

|

SU1140113A1 |

| Устройство для определения кода нормализации | 1987 |

|

SU1465878A1 |

| Устройство для предсказания четности результата сдвигателя | 1988 |

|

SU1649545A1 |

| Устройство для сложения-вычитания чисел с плавающей запятой | 1986 |

|

SU1376080A1 |

| Устройство для формирования сигналов четности | 1988 |

|

SU1571591A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство для сложения-вычитания чисел с плавающей запятой | 1991 |

|

SU1784971A1 |

| Устройство для предсказания четности результата сдвигателя | 1989 |

|

SU1658155A1 |

| Арифметическое устройство с плавающей точкой | 1985 |

|

SU1259248A1 |

| Устройство для предсказания четности результата сдвигателя | 1989 |

|

SU1730628A1 |

Изобретение относится к вычислительной технике и может быть применено в высокопроизводительных системах обработки информации. Целью изобретения является сокращение аппаратурных затрат. Устройство содержит сдвигатель 1, блок 3 дешифраторов нуля, два шифратора 4 и 7, первый узел 2 инвертирования, коммутатор 5, узел 8 сравнения и второй узел 6 инвертирования. Введение второго узла 6 инвертирования с соответствующими связями обеспечивает положительный эффект, заключающийся в сокращении аппаратурных затрат. 3 ил.

-Л

8

Фиг. 5

| Авторское свидетельство СССР № 1331315, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сдвига данных | 1983 |

|

SU1140113A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-07-30—Публикация

1989-07-10—Подача