Известны устройства умножения, реализующие сокращенный способ умножения, состоящий в прибавлении множимого для множителей «О до «5 и вычитании для множителей от «6 до «9, содержащие регистры, триггеры, логические собирательные схемы и схемы совпадения.

Предлагаемое устройство умножения отличается тем, что для упрощения в нем применены два одноразрядных десятичных счетчика, соединенные через вентили с устройством управления и соответственно с прямым и инверсным выходами триггера. Вход последнего подключен к соответствующему разряду регистра множителя, а выходы счетчиков через собирательную схему соединены со входом сброса триггера, служащего для разрешения передачи множимого в накапливающий регистр.

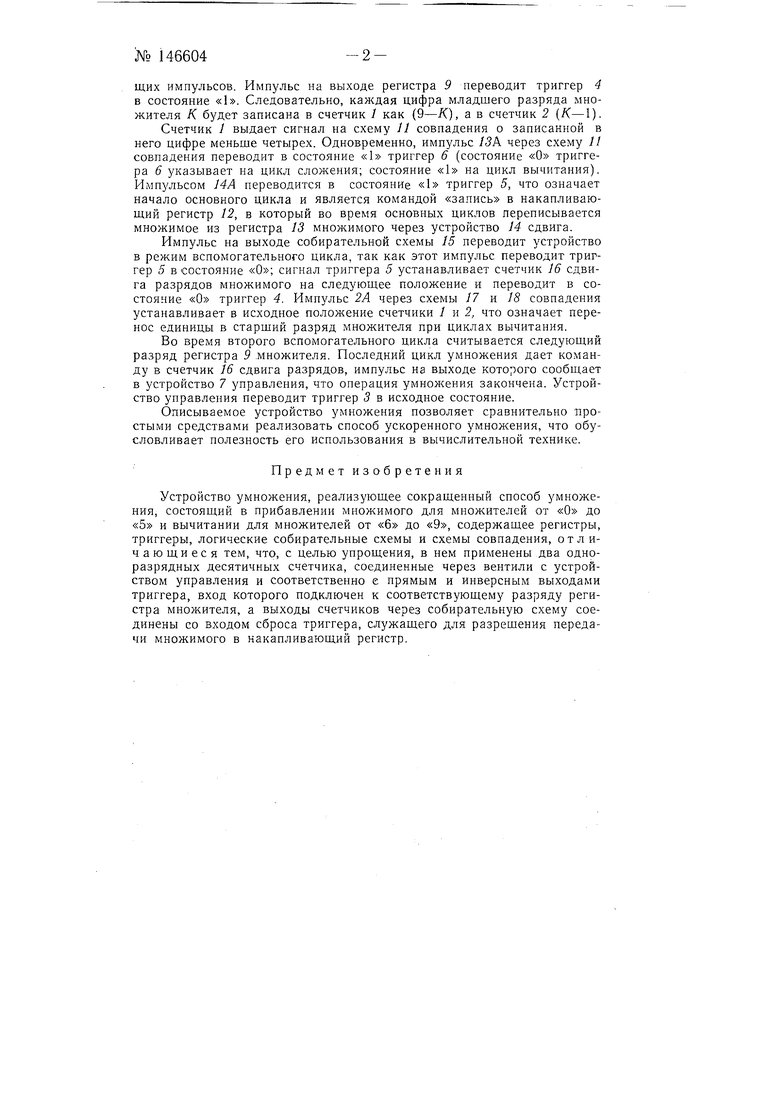

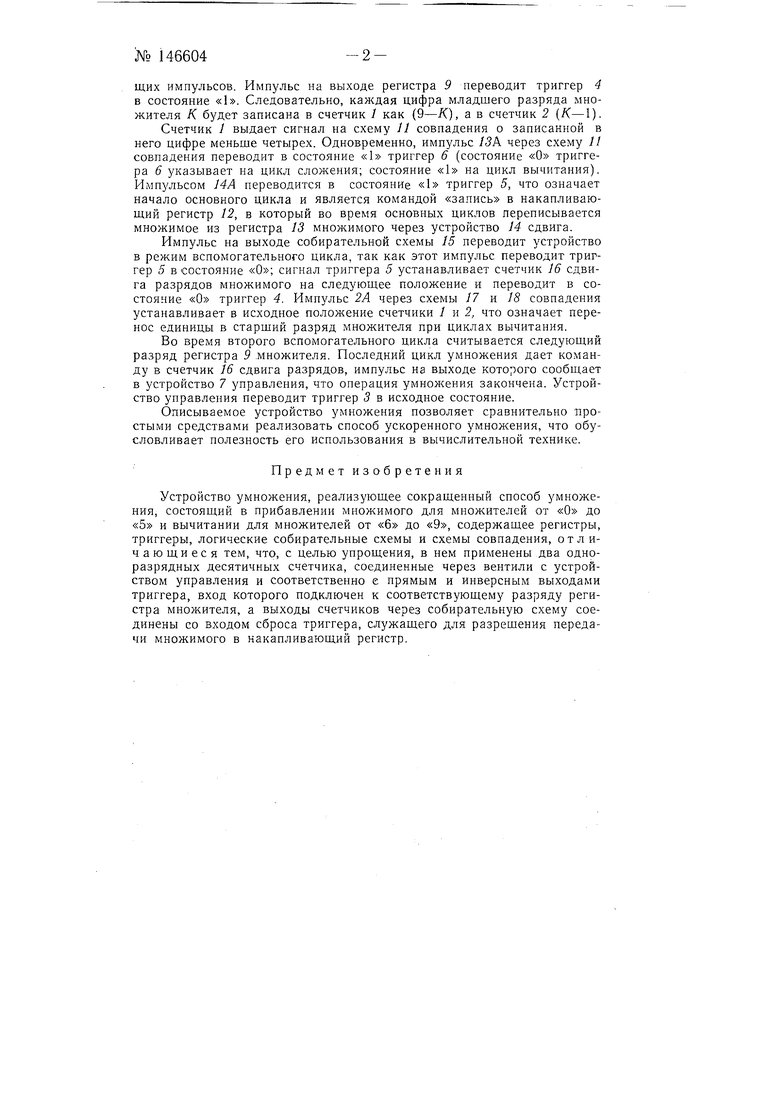

На чертеже изображена функциональная схема описываемого устройства умножения.

В исходном состоянии устройства одноразрядные десятичные счетчики 1 и 2 установлены в «О и «9 положения соответственно. Триггеры 3, 4, 5 и 6 находятся в «О состоянии. Необходимые для работы устройства управляющие импульсы М, 2А, 13А, 14А, 15А и серии импульсов и ЗВ-гЛВ в каждом цикле вырабатываются устройством 7 управления. Номера этих импульсов указывают последовательность их во времени; частота следования импульсов А и В одинакова, но импульсы В отстают по фазе на половину периода от импульсов А.

Импульс начала операции умножения поступает из устройства 7 управления на схему 8 совладения и переводит триггер 5 в состояние «1. Этим начинается первый цикл умножения, являющийся вспомогательным, во время которого первый разряд множителя из регистра 9 множителя переписывается в счетчики / и 2. Для этого через схему 10 совпадения на регистр 9 множителя поступают десять считываю№ 146604-2щих импульсов. Импульс на выходе регистра 9 переводит триггер 4 в состояние «1. Следовательно, каждая цифра младшего разряда множителя К будет записана в счетчик / как (9-К), а в счетчик 2 (К.-1).

Счетчик 1 выдает сигнал на схему 11 совпадения о записанной в него цифре меньше четырех. Одновременно, имнульс через схему // совпадения переводит в состояние «1 триггер 6 (состояние «О триггера 6 указывает на цикл сложения; состояние «1 на цикл вычитания). Импульсом 14А переводится в состояние «1 триггер 5, что означает начало основного цикла и является командой «запись в накапливающий регистр 12, Б который во время основных циклов переписывается множимое из регистра 13 множимого через устройство 14 сдвига.

Импульс на выходе собирательной схемы 15 переводит устройство в режим вспомогательного цикла, так как этот импульс переводит триггер 5 в состояние сигнал триггера 5 устанавливает счетчик 16 сдвига разрядов множимого на следующее положение и переводит в состояние «О триггер 4. Импульс 2А через схемы 17 и 18 совпадения устанавливает в исходное положение счетчики 1 и 2, что означает перенос единицы в старший разряд множителя при циклах вычитания.

Во время второго вспомогательного цикла считывается следующий разряд регистра 9 .множителя. Последний цикл умножения дает команду в счетчик 16 сдвига разрядов, импульс на выходе которого сообщает в устройство 7 управления, что операция умножения закончена. Устройство управления переводит триггер 5 в исходное состояние.

Описываемое устройство умножения позволяет сравнительно простыми средствами реализовать способ ускоренного умножения, что обусловливает полезность его использования в вычислительной технике.

Предметизобретения

Устройство умножения, реализующее сокращенный способ умножения, состоящий в прибавлении множимого для множителей от «О до «5 и вычитании для множителей от «6 до «9, содержащее регистры, триггеры, логические собирательные схемы и схемы совпадения, отличающиеся тем, что, с целью упрощения, в нем применены два одноразрядных десятичных счетчика, соединенные через вентили с устройством управления и соответственно е прямым и инверсным выходами триггера, вход которого подключен к соответствующему разряду регистра множителя, а выходы счетчиков через собирательную схему соединены со входом сброса триггера, служащего для разрешения передачи множимого в накапливающий регистр.

| название | год | авторы | номер документа |

|---|---|---|---|

| Десятичный сумматор | 1961 |

|

SU151117A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Устройство для умножения данных переменной длины | 1985 |

|

SU1291972A1 |

| МНОЖИТЕЛЬНОЕ УСТРОЙСТВО ПОСЛЕДОВАТЕЛЬНОГОДЕЙСТВИЯ | 1970 |

|

SU434411A1 |

| Арифметическое устройство | 1971 |

|

SU522497A1 |

| Множительное устройство | 1979 |

|

SU832554A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ | 1973 |

|

SU409222A1 |

| УСТРОЙСТВО УМНОЖ1ЕНИЯ | 1968 |

|

SU220632A1 |

| ЭЛЕКТРОННАЯ КЛАВИШНАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА | 1973 |

|

SU395837A1 |

| Устройство для умножения | 1980 |

|

SU960805A1 |

Авторы

Даты

1962-01-01—Публикация

1961-04-20—Подача