1

Изобретение.относится к области автоматики и вычислительной техники и может быть использовано при реализации технических средств автоматики и вычислительной техники.

Известны устройства для умножения, содержащие коммутатор, связанный выходами с шинами опроса регистра множимого и регистра множителя, причем выходы регистра множимого через первую группу схемы «И соединены с входом одноразрядного двоичнодесятичного накопительного сумматора, выходы которого подключены к входам счетчика переносов, и через вторую группу схем «И, на другие входы которых подсоединены выходы генератора сигналов управления, связаны с выходными шинами устройства, и преобразователь кодов.

Однако известные устройства сложны, так как в них необходимо применение регистров для хра нения операндов. Кроме того, они не обеспечивают дннамической индикации результатов без иснользОвания регистра результата и не позволяют отслеживать произведение при изменении значений сомножителей в процессе вычислений.

Предложенное устройство отличается тем, что выходы регистра множителя соединены С входами преобразователя кодов, а выход преобразователя-с вторыми входами схем «И первой группы.

Это позволяет упростить устройство и расширить его функциональные возможности.

Сокращение электронного оборудования достигается за счет того, что при вычислении произведений десятичных цифр управление накапливающим сумматором осуществляется с помощью преобразователя кодов цифр множителя в число-импульсный код.

Умножение проводится многократно и непрерывно с определенной частотой, а произведение поступает непосредственно на визуальный индикатор динамического типа либо на какое-нибудь регистрирующее устройство.

Использование перекрестного метода в сочетании с многократным вычислением позволяет реализовать преимущество данного метода умножения, заключающееся в том, что разрядность промежуточных результатов, которые необходимо хранить в процессе вычислений, значительно меньше, чем при других методах умножения.

При умножении /i-разрядных десятичных чисел перекрестным методом разрядность промежуточных результатов не более Ig п + 3, в то время как при умножении общепринятым методом накопления кратных мнол имого разрядность промежуточных результатов равна п+1

Поскольку в предлагаемом устройстве умножение выполняется непрерывно и многократно, один или оба сомножителя могут изменяться в процессе вычислений. В этоы случае умножающее устройство отрабатывает изменяющееся произведение, что дает возможность в зависимости от значения результата динамически воздействовать на объекты, являющиеся источниками сомножителей. Такие вычислительные устройства находят применение в весовых дозирующих автоматах, в различных измерительных и технологических установках, в системах программного управле}1ИЯ и т. д.

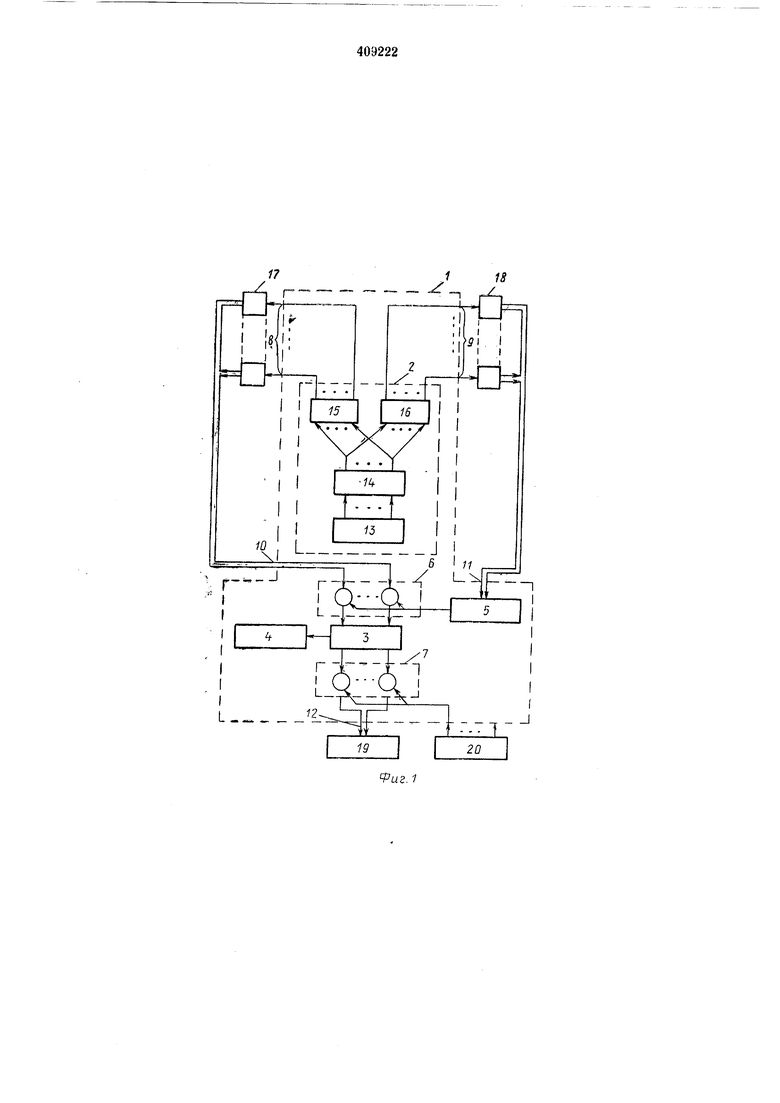

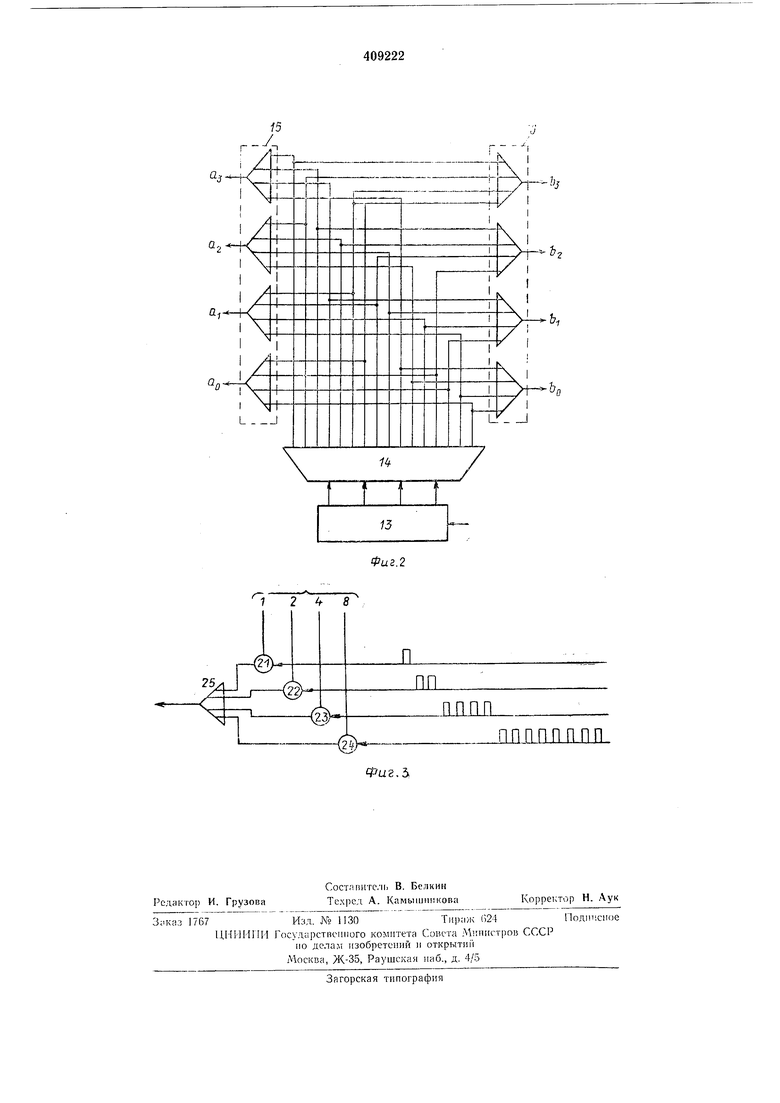

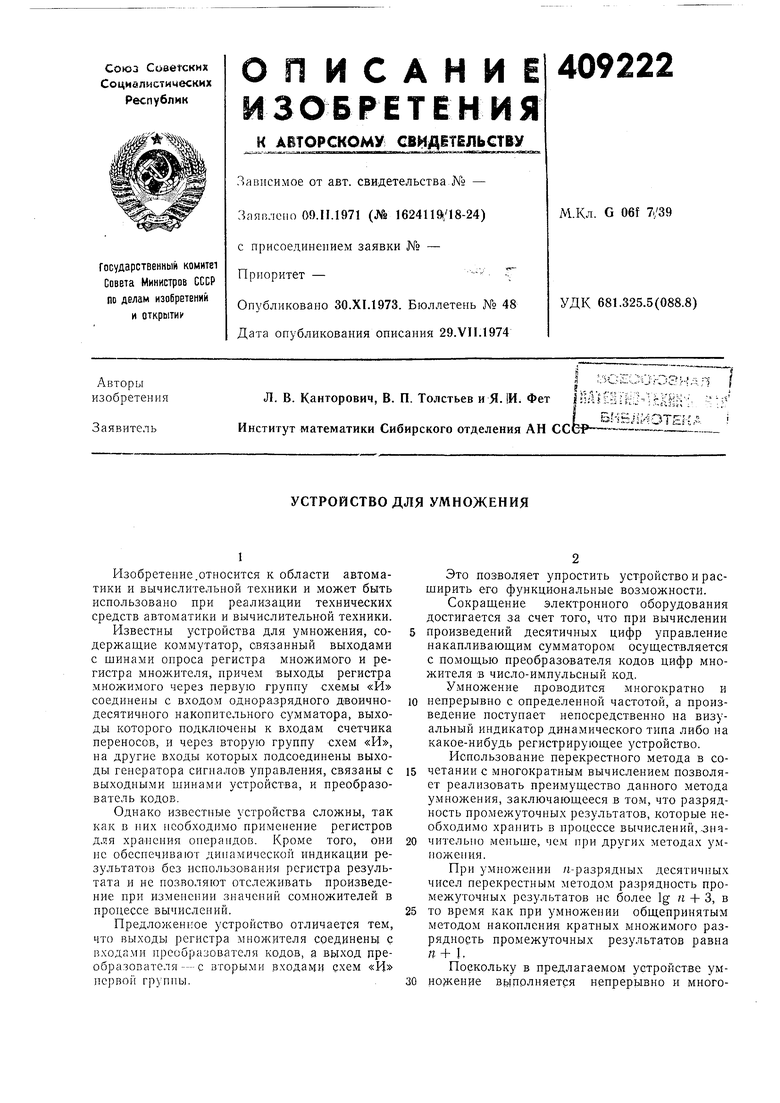

На фиг. 1 представлена блок-схема умножающего устройства; на фиг. 2 -пример реализации схемы опроса разрядов операндов для случая и 4; на фиг. 3 - пример реализации схемы преобразователя кодов.

Для облегчения объяснения работы умножающего устройства на чертежах и в дальнейшем описании оно рассматривается во взаимодействии с двумя tt-разрядными регистрами сомножителей, динамическим визуальным индикатором результата и генератором сигналов управления. Реализация этих узлов для работы предложенного устройства несуществеННа и зависит от конкретных условий, в которых оно используется.

Умножающее устройство 1 (фиг. 1) содержит схему опроса операндов - коммутатор 2, одноразрядный двоично-десятичный накопительный сумматор 3, счетчик 4 переносов, преобразователь 5 позиционного кода цифр множителя в число-импульсный код, группу схем «И 6, группу схем «И 7, шины сигналов опроса разрядов множимого 8, множителя 9, входов кодов цифр множнмого 10, входов кодов цифр множителя 11 и выходов кодов цифр произведения 12.

Ком:мутатор 2 состоит из счетчика 13, дешифратора 14 и групп схем «ИЛР 15 и 16. Выходы счетчика 13 подключены к соответствующим входам дешифратора 14, а выходы дешифратора - к соответствующим входам схем «ИЛИ 15 и 16. Выходы группы схем «ИЛИ 15 коммутатора 2 связаны с соответствующими шинами 8 сигналов опроса разрядов множимого, а выходы группы схем «ИЛР1 16-с соответствующими шинами 9 сигналов опроса разрядов множителя. Каждая из шин 8 соединена с соответствующим управляющим входом регистра 17 множимого, а каждая из щин 9 - с соответствующим управляющим входом регистра 18 множителя. Информационные выходы регистра 17 подсоединены к соответствующим шинам 10 входов кодов цифр множимого, а информационные выходы регистра 18 -к соответствующим шинам // входов кодов цифр множителя.

Шины 10 соединены с информационными входами соответствующих схем «И 6, а шины // - с соответствующими входами преобразователя 5. Выход преобразователя связан с управляющими входами всех схем «И 6, выходы которых подключены к соответствующим входам сумматора 5. Выход переносов сумматора соединен с входом счетчика 4 переносов, выходы суммы сумматора -с входами соответствующих схем «И 7, выходы которых подключены к щинам 12 выходов кодов цифр

произведения.

Шины 12 связаиы также с входами индикатора 19. Выходы генератора 20 сигналов управления соединены с соответствующими входами сумматора в, счетчика 4 переносов,

преобразователя 5 кодов, группы схем «И 7 и счетчика 13.

Предложенное устройство работает следующим образом.

Пусть в регистрах 17 и 18 имеются л-разрядные сомножители: множимое , ..., uiflo и множитель В Ь„- , ..., bibo.

Необходимо получить на индикаторе 19

произведение С Czn-iCiCo.

В 0-ом цикле (т. е. при вычислении разряда Со произведения) опрашиваются разряды GO, о; в 1-м цикле: «о, &i и «ь 6о и т.д.; в (2п-1)-м цикле: , . Всего при вычислении произведения опрашивается п различных пар разрядов сомножителей, причем

каждый разряд каждого сомножителя опрашивается п раз. В соответствии с этим разрядность счетчика 13 коммутатора 2 выбирается таким образом, чтобы он имел не менее, чем п состояний. У дешифратора 14 ti выходов,

каждый из которых соответствует одному из состояний счетчика. Каждая из групп схем «РШИ 15, 16 содержит п /г-входовых схем «ИЛИ, причем каждая схема из группы схем «ИЛИ 15 соответствует одному из разрядов

множимого, а группы схем «ИЛИ /5 -множителя. Входы каждой схемы «ИЛИ соединены с п выходами дешифратора 14, соответствующими тем состояниям счетчика, в которых должен опрашиваться данный разряд данi;oro операнда согласно приведенной последовательности опроса (с точностью до перестаj:OBKH нар внутри каждого цикла).

В предложенном устройстве проводится многократное повторное вычислите произведения. Следовательно, необходимо осуществлять многократный повторный опрос операндов в соответствии с приведенным порядком. При использовании указанного коммутатора такой опрос обеспечивается подачей на вход

счетчика 13 от генератора 20 простейшей непрерывной последовательности счетных импульсов. Это приводит к дополнительной эко1 омии оборудования в схемах управления. Итак, в каждом состоянии счетчика на шины входов кодов цифр множимого и множителя поступает пара цифр, соответствующих данному состоянию разрядов сомножителей. Умножение этих цифр проводится следующим образом.

Код цифры множимого ноступает с шин 10 входов на информационные входы группы схем «И в и сумматор 3. Код цифры множителя подается с шин 11 на преобразователь 5, который преобразует этот код в число-импульсный. 11ред.11и.аа1 ;juiC5i, чти 1и1фр1л множителя постуиаил 1;а вход умюжшииичч) ycipoiiCTiu iкоде, 8---4---2-1. Иреобразов;пель состоит из схем «К 21-24 и схемы «ИЛИ 25. К первым входам схем «PI 21-24 подключены шины цифр кода множителя свесами, соответственно 1,2,4,8. На вторые входы схем «И 21-24 проходят соответственно 1,2,4,8 импульсов от rciiepaTopa 20, причем временное расположение импульсов может быть, например, таKUM, как показано на фиг. 3. Выходы схем «И 21-24 подключены к входам схемы «ИЛИ 25, выход которой является выходом преобразователя кодов. Таким образом, после падачи серии импульсов, показанной на фиг. 3, на выход преобразователя кодов подается число импульсов, соответствующее пифре множителя, опрашиваемой в данный момент. В результате через группу схем «И 6 цифра множимого, опрашиваемая в данный момент, поступает па вход накопительного сумматора столько раз, сколько единиц содержится в цифре мяожителя. Возникающие при сложении переносы попадают из сумматора в счетчик 4 переносов, емкость которого зависит от разрядности сомножителей. В соответствии с алгоритмом перекрестного умножения в конце г-го цикла на сум.маторе содержится /-я цифра произведения. Из генератора 20 в конце каждого цикла подается сигнал на управляющие входы всех схем «И 7, в результате чего код данной цифры произведения поступает через шипы 12 на входы индикатора 19. Затем проводится сдвиг содержимого счетчика 4 и сумматора 3 на один десятичный разряд biip;iiu), liOc.ie чего устройство переходит к вьпю.шсиию с.чсдующего цикла. Концу каждого цикла соответствует определенное состояние счетчика 13, и, следовательно, сигнал на определенном выходе дешифратора 14. Эти сигналы могут быть использованы для управления разрядными входами индикатора, что является дополнительным преимуществом предлагаемой схемы коммутатора. Необходимые для качественной индикации частота вычислений произведения и длительность высветки каждой цифры зависят от характеристик применяемого индикаторного устройства. Предмет изобретения Устройство для умножеии.ч, содержащее коммутатор, связанный выходами с шинами опроса регистра множимого и регистра множителя, а причем выходы регистра множимого через первую группу схем «И связаны с входами одноразрядного двоично-десятичного накопительного сумматора, выходы которого подключены к входам счетчика переносов, и через вторую группу схем «И, другими входами связанных с выходом генератора сигналов управления, соединены с выходными шинами устройстве., и преобразователь кодов, отличающееся тем, что, с целью упропдепия устройства, выходы регистра множителя соединены с входами преобразователя кодов, выход которого связаи с другими входами первой группы схем «И.

17

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1982 |

|

SU1136151A1 |

| Устройство для умножения двоичных чисел | 1980 |

|

SU981996A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Устройство для умножения десятичных чисел | 1981 |

|

SU1016780A1 |

| Устройство для умножения чисел с плавающей запятой | 1985 |

|

SU1280624A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство для умножения двух @ -разрядных чисел | 1988 |

|

SU1575174A1 |

| Множительное устройство | 1982 |

|

SU1116427A1 |

| Множительное устройство | 1982 |

|

SU1053104A1 |

| Матричное устройство для умножения | 1979 |

|

SU842800A1 |

r-i---r--i

L..

-t

QO

1 2 Ч- 8 V

-Ъ,

1ПППППП

Авторы

Даты

1973-01-01—Публикация