в вычислительной технике известны устройства умножения, содержащие регистры, сумматор, блок анализа множителей и логические схемы.

Предлагаемое устройство отличается от известных тем, что с целью экономии оборудования вход регистра множителя соединен с выходами элемента запрета и первого элемента совпадения, выход регистра связан с первым входом второго элемента совпадения и входом записи элемента запрета. Второй вход второго элемента совпадения, вход запрета элемента запрета и первый вход первого элемента совпадения подключены к выходу схемы счетчика разрядов множителя. Второй вход первого элемента совпадения соединен с выходом сумматора. Вход схемы округления подключен к выходу схемы счетчика разрядов множителя, а выход - ко входу сумматора.

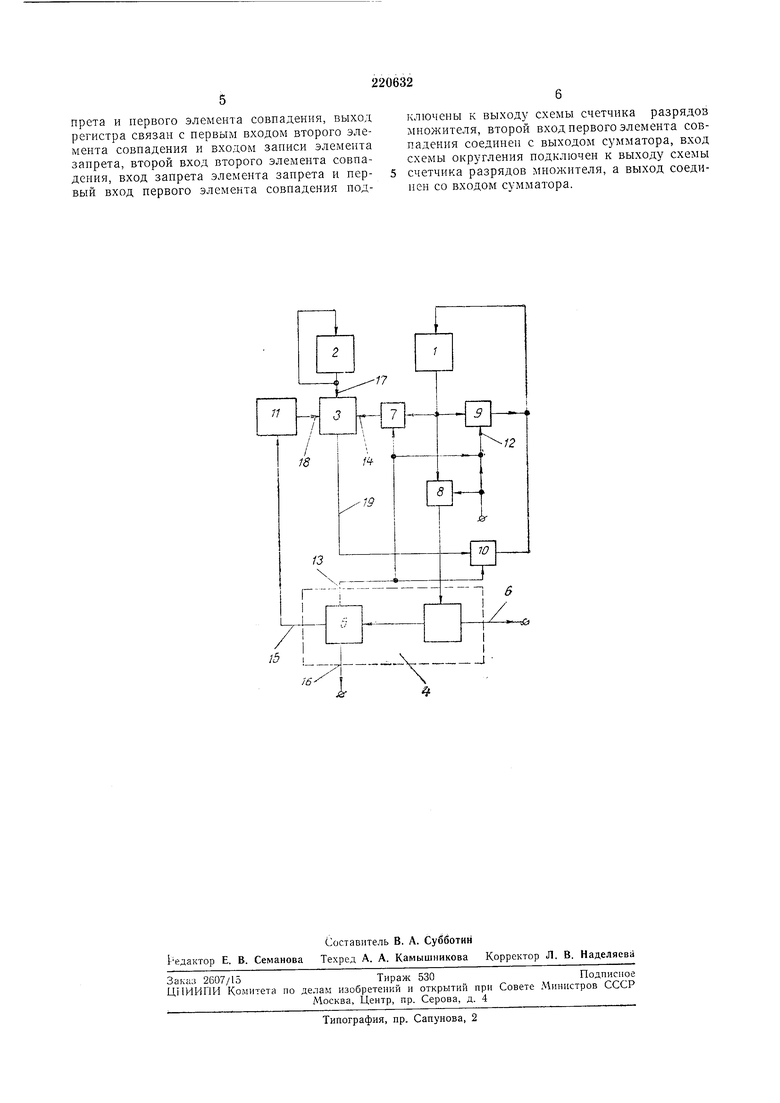

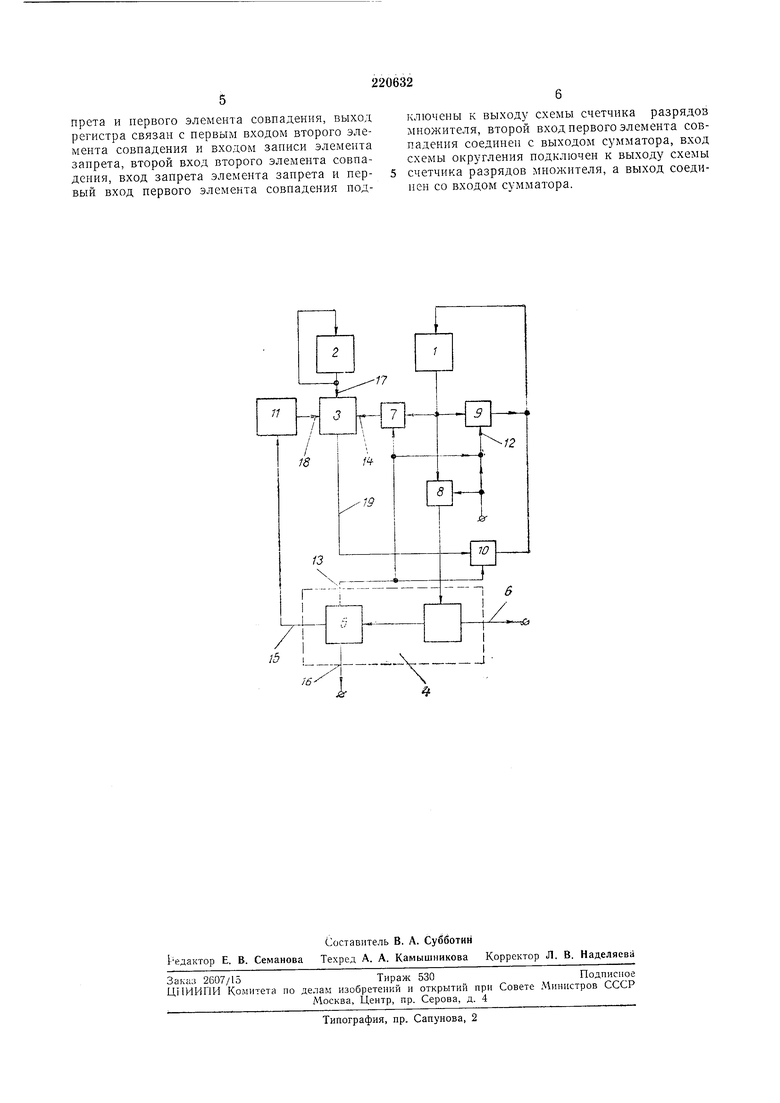

На чертеже представлена блок-схема устройства для умножения «-разрядных чисел для случая арифметического устройства последовательного счета.

Устройство содержит регистр / множителя и результата, регистр 2 множимого, сумматор 3, блок 4 анализа множителя, счетчик 5 разрядов множителя, выход 6 анализатора цифр множителя, элементы 7 и 8 совпадения, разрешающие прохождение кода числа, хранящегося в регистре /, элемент 9 запрета, управляющий перезаписью числа в регистре /, элемент 10 совпадения, управляющий выдачей результата суммирования в регистр / и схему // округления.

Выход регистра 1 соединен с одним из входов каждого из элементов 7 и 8 совпадения и входом записи элемента 9; второй вход элемента 8 соединен с устройством управления вычислительного устройства и входом запрета 12 элемента 9; второй вход элемента 7 - с выходом 13 схемы счетчика разряда множителя и входом запрета 12 элемента 9. Выход элемента 7 соединен со входом 14 сумматора, выход элемента 8 - со входом блока анализа множителя, выход элемента 9 - со входом регистра 1. Выход 15 схемы счетчика соединен со входом округления, а выход 16 - с устройством управления концом операций вычислительного устройства. Выход 6 соединен с устройством управления вычислительного устройства, выход регистра 2 - со входом этого же регистра и входом 17 сумматора, выход схемы округления - со входом 18 сумматора. Выход 19 сумматора соединен с одним входом элемента 10, другой вход этого элемента соединен с выходом 13, а выход - с выходом регистра /. Регистры 1 и 2 допускают сдвиг только вправо.

Устройство работает следующим образом (множитель записан в регистре /, множимое- - 15 регистре 2).

В начале операции происходит сдвиг множителя на один разряд внраво. Одновременно из устройства управления вычислительным устройством поступает импульс па вход элемента 6 II вход запрета элемента 9. При этом младшая ппфра множителя поступает в анализатор цифр множителя, а в счетчик разрядов множителя записывается единица.

Пусть цифра младшего разряда множителя ut - пе нуль, тогда начинаются сдвиги в регистрах / и 2. Сигналов на вход запрета элемента 9 не поступает. В результате в регистрах 1 1 2 начинается перезапись чисел, т. е. младшне разряды чисел переписываются в старшие, и кроме того, разряды множимого, начиная с младшего, поступают в сумматор 3 (выдача с сумматора на вход регистра 1 запреш,епа).

При выдаче (п-1)-го разряда множимого происходит выдача сигнала со счетчика 5 разрядов множителя на схему //. По этому сигналу с выхода схемы 11 на сумматор 3 подается число - - , где а - основание системы

счисления (например, для десятичной подается число 5). Если цифра (п-1)-го разряда больше нли равна - , в сумматоре образуется

ница переноса в старший разряд, т. е. происходит округление /г-го разряда множимого. При выдаче п-го разряда из регистров прекращается перезапись в регистре 1, так как из схемы счетчика разрядов поступает сигнал на вход элемента 7 и вход запрета элементов 9. При этом разрешается выдача на сумматор п-го разряда множителя (в первом цикле это будет нуль). Таким образом, происходит сложение п-го разряда множимого и, если есть единицы переноса, с записью результата в старший разряд регистра /, так как открыт элемент 10.

После окончания этого цикла происходит вычитание единицы из цифры множителя, поступавшей в начале операции в блок 4. Происходит повторный анализ оставшегося значения цифры множителя. Если она не равна нулю, процесс, описанный выше, повторяется. Только теперь происходит сложение п-го разряда множимого с промежуточным результатом, записанным в регистре 7, и, если есть, единицей переноса от округления. Количество описанных циклов сложения будет равно цифре исследуемого разряда множителя. При этом в регистре I получают промежуточный результат, равный ai (6„-|-Агг), где «1 - младший разряд множителя, 6 „ - старщий п-ный разряд множимого.

в том случае, если анализируемое значение разряда множителя равно нулю, производится сдвиг регистра У вправо. При этом сигналом из устройства управления открывается элемент 8 и закрывается э.темент 9. Следующая цифра множителя поступает в блок 4, н в счетчик 5 разрядов заносится еще одна единица. При умножении на цифру следующего разряда множителя все происходит аналогично описанному за исключением того, что в связи с заполпением счетчнка 5 разрядов на единицу происходит округление (п-1)-го разряда, т. е.

- поступает в сумматор одновременно с

{п-2)-ным разрядом множимого. При этом через элемент 9 будет переписываться (п-2) младших разряда регистра /, а в сумматор через элемент 7 будут переписываться 2 старших разряда. С промежуточным результатом умножения складывается теперь не старщий «-Й разряд множимого, а два старщих, п-й и (л -1)-й разряды множимого.

В результате этого цикла происходит умножение «2 (6 „+/ /г-i+A -1), а промежуточный результат равняется

1 (п + А «) + «2 (п + «-1 + А /г - 1). При умиожении на /с-й разряд множителя в связи с заполнением счетчика к единицами округление происходит (п - «4-1)-го разряда

множимого, т. е. в сумматоре -будет складыZi

ваться с (п - /с)-ным разрядом множимого, а к нромежуточному результату будут прибавляться к старщих разрядов мпожимого.

При умножении на последнюю цифру множителя происходит умножение

Qj&;,+.-l+... + 6l + Al),

И В регистре / записан результат, равный

1 (Ьп + А Л) + «2 ( + Ьп-1 + A/Z - 1) + ... + + ««(«+ + -+6i + Al).

Множимое сохранено в регистре 2.

Счетчик 5 разрядов заполнен, и с его выхода 16 поступает сигнал конца операции в устройство унравления концом операции и вычислительного устройства. Если количество значащих разрядов множимого и множителя в

сумме пе превосходит л, то результат произведения, полученный данным способом, будет абсолютно точным. В противном случае результат будет приближенным, но в наихудшем случае относительная погрешность произведения

ДЯ п -1

не превышает

2x1

Предмет изобретения

прета и первого элемента совпадения, выход регистра связан с первым входом второго элемента совпадения и входом записи элемента запрета, второй вход второго элемента совпадения, вход запрета элемента запрета и первый вход первого элемента совпадения подключены к выходу схемы счетчика разрядов множителя, второй вход первого элемента совпадения соединен с выходом сумматора, вход схемы округления подключен к выходу схемы счетчика разрядов множителя, а выход соединен со входом сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1988 |

|

SU1654814A2 |

| Устройство для умножения | 1976 |

|

SU651341A1 |

| Устройство для умножения | 1984 |

|

SU1249507A1 |

| Устройство управления умножением двоично-десятичных чисел | 1972 |

|

SU469969A1 |

| Устройство для умножения | 1985 |

|

SU1278838A1 |

| Последовательное множительное устройство | 1981 |

|

SU987620A1 |

| Устройство для умножения | 1990 |

|

SU1753471A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО | 1971 |

|

SU318941A1 |

| Устройство для умножения | 1982 |

|

SU1136151A1 |

| Арифметическое устройство | 1985 |

|

SU1287144A1 |

16

Авторы

Даты

1968-01-01—Публикация