Изобретение относится к вычислительной технике и может быть использовано в специализированных системах обработки сигналов высокой производительности.

Цель изобретения - сокращение аппаратурных затрат.

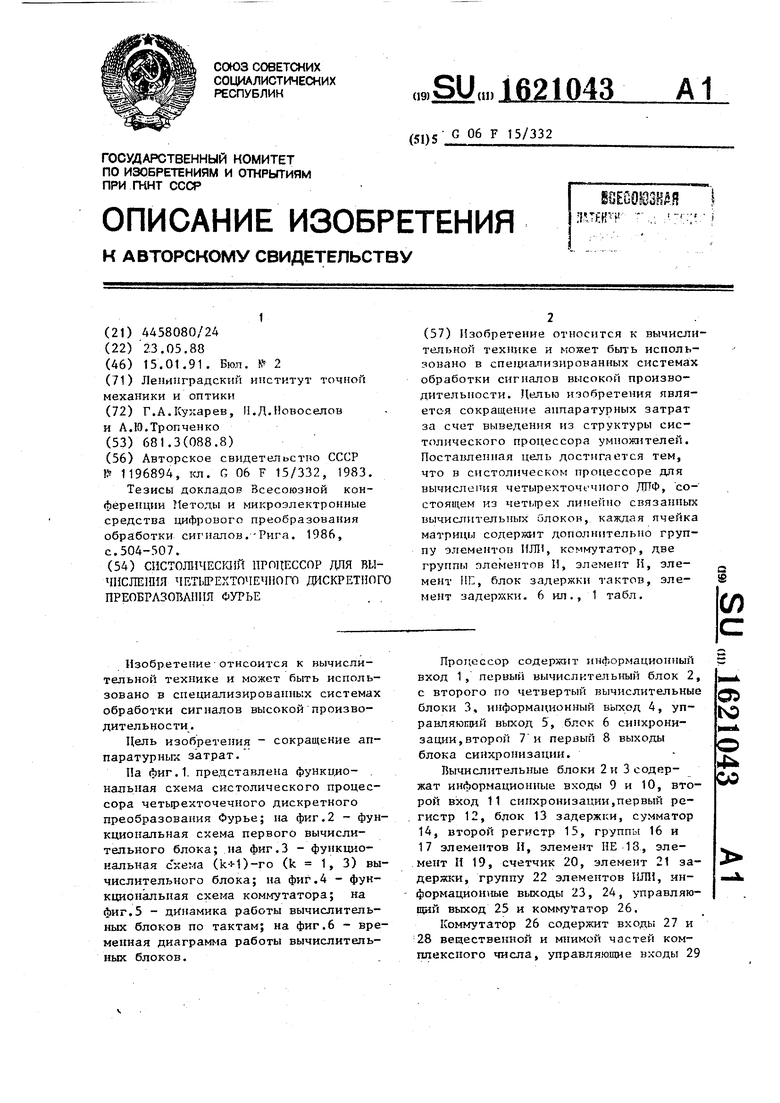

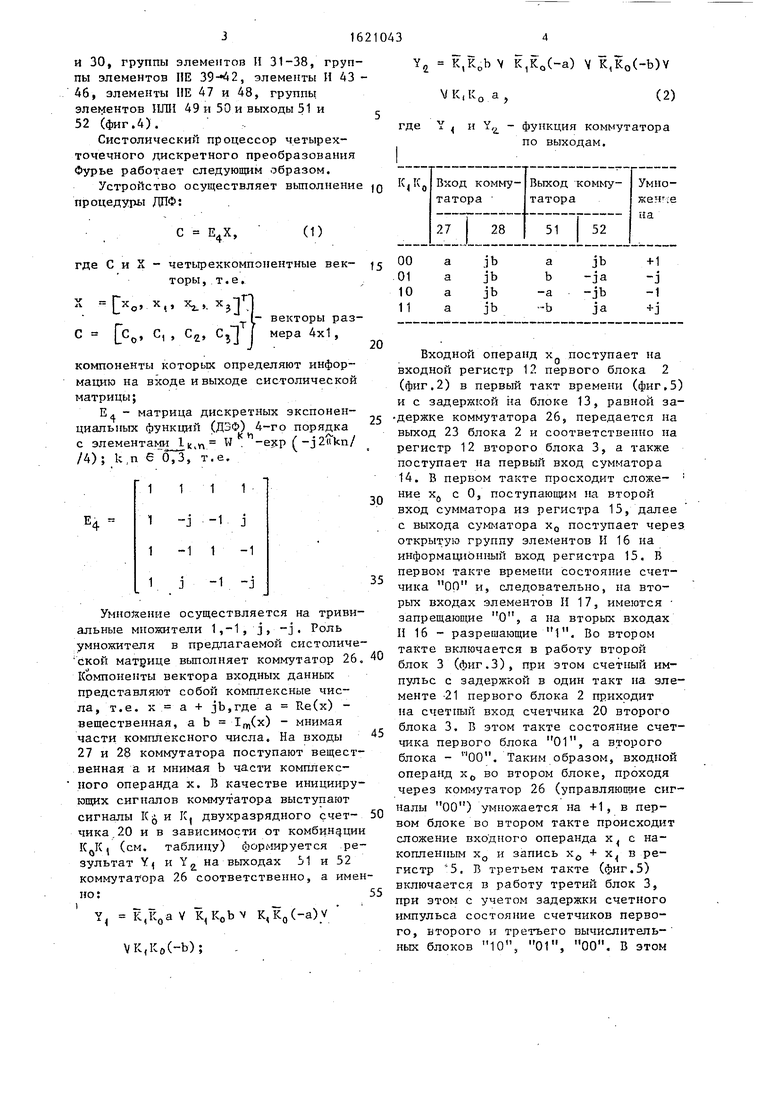

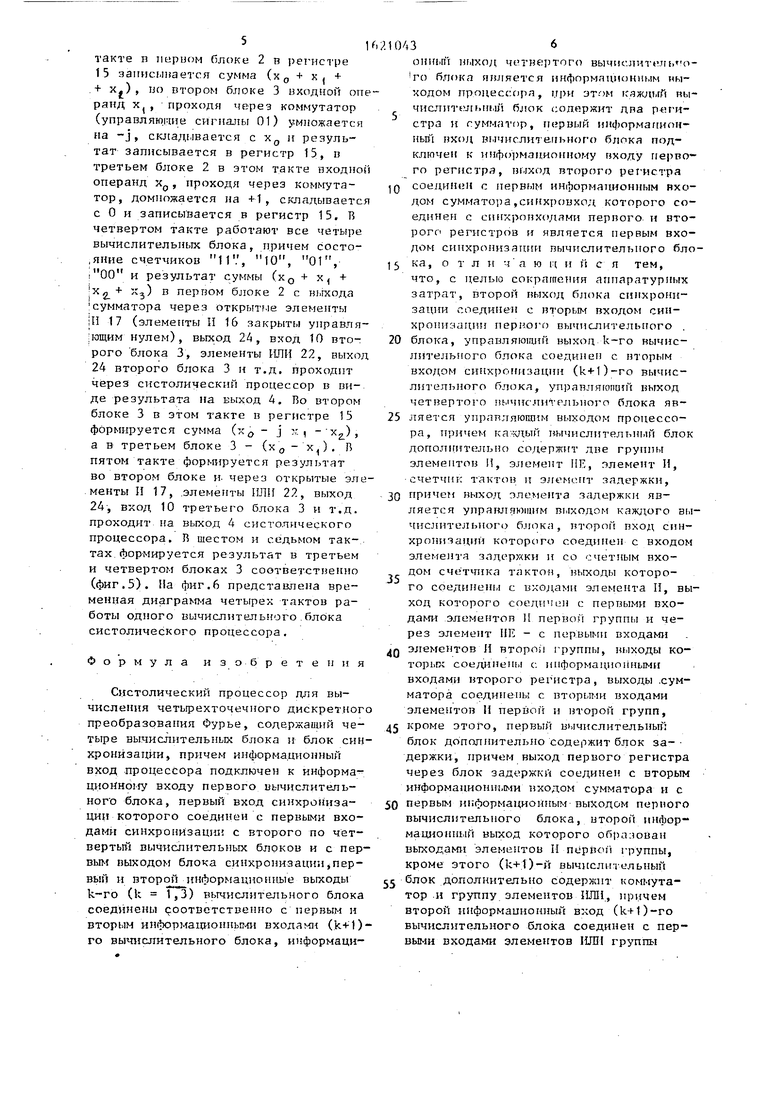

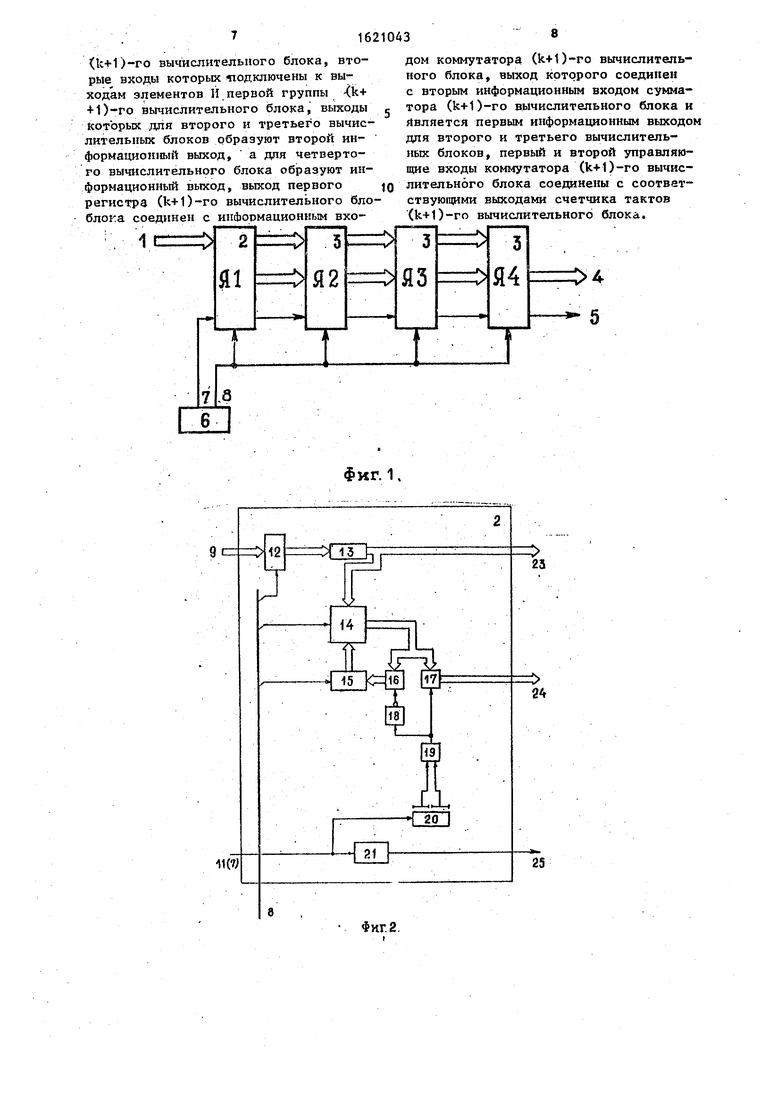

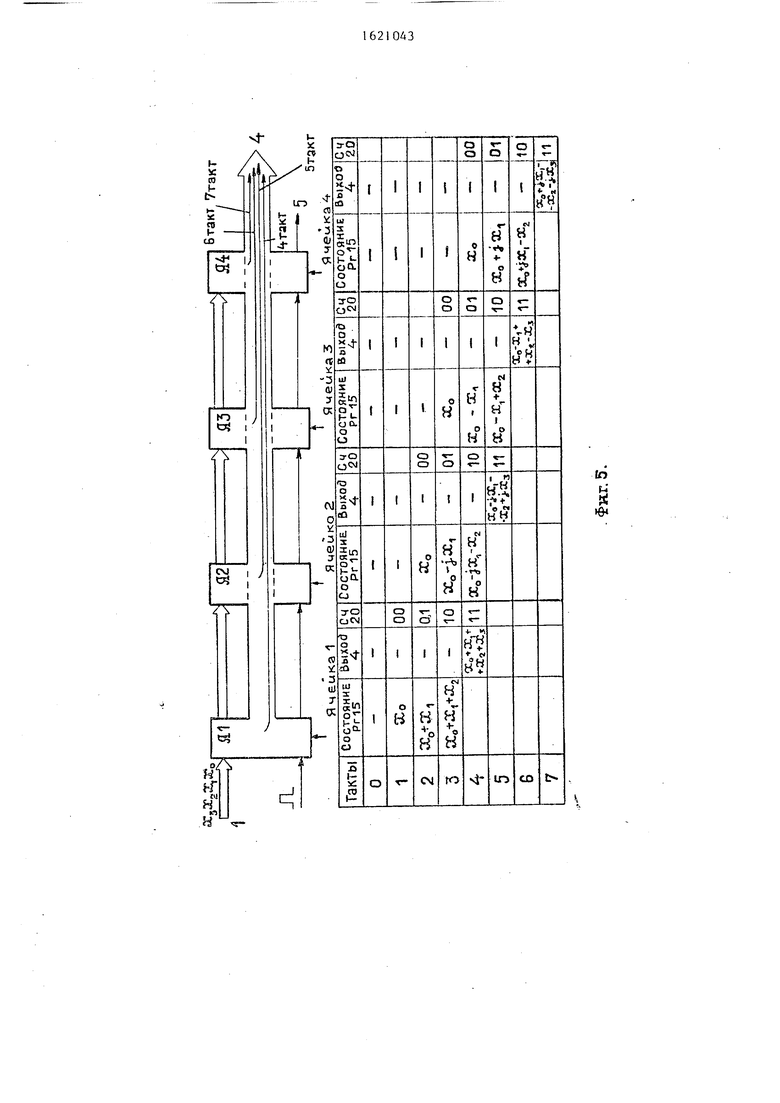

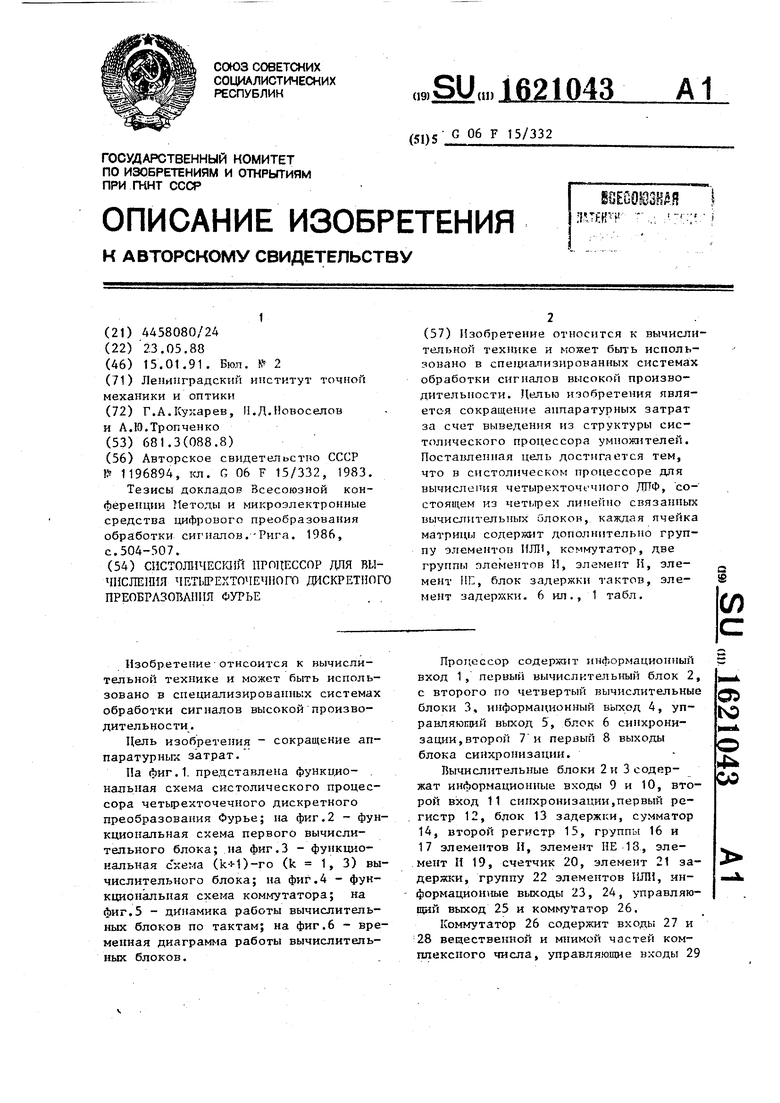

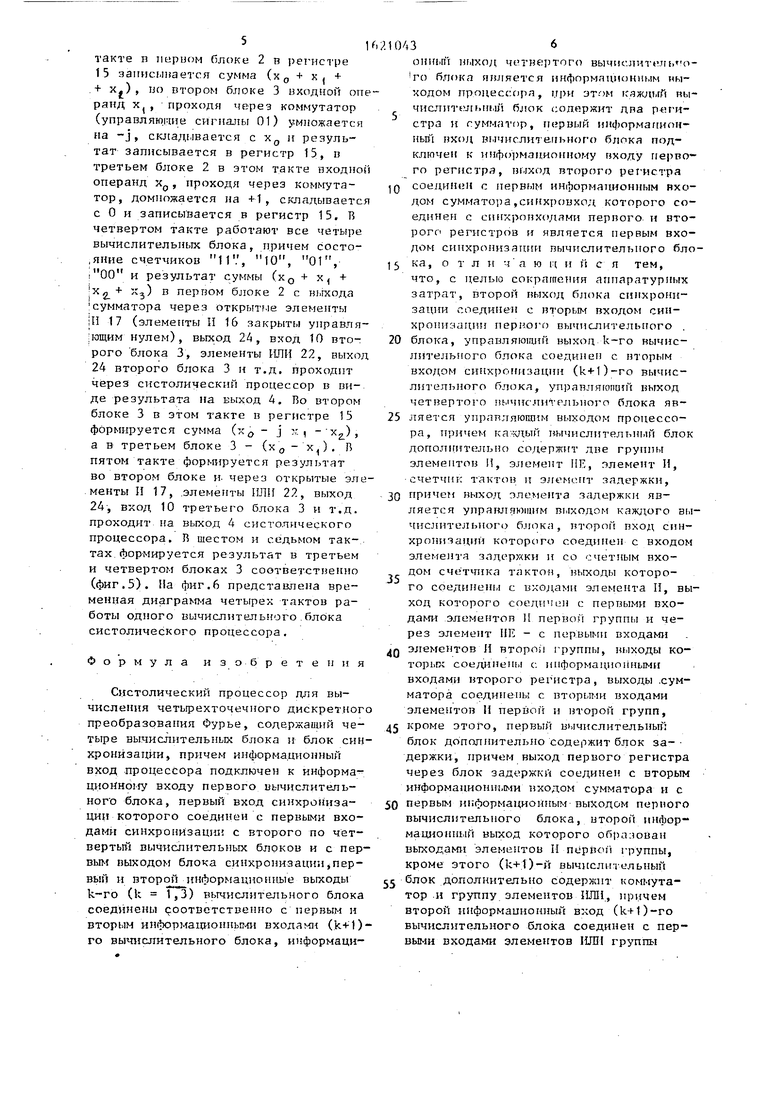

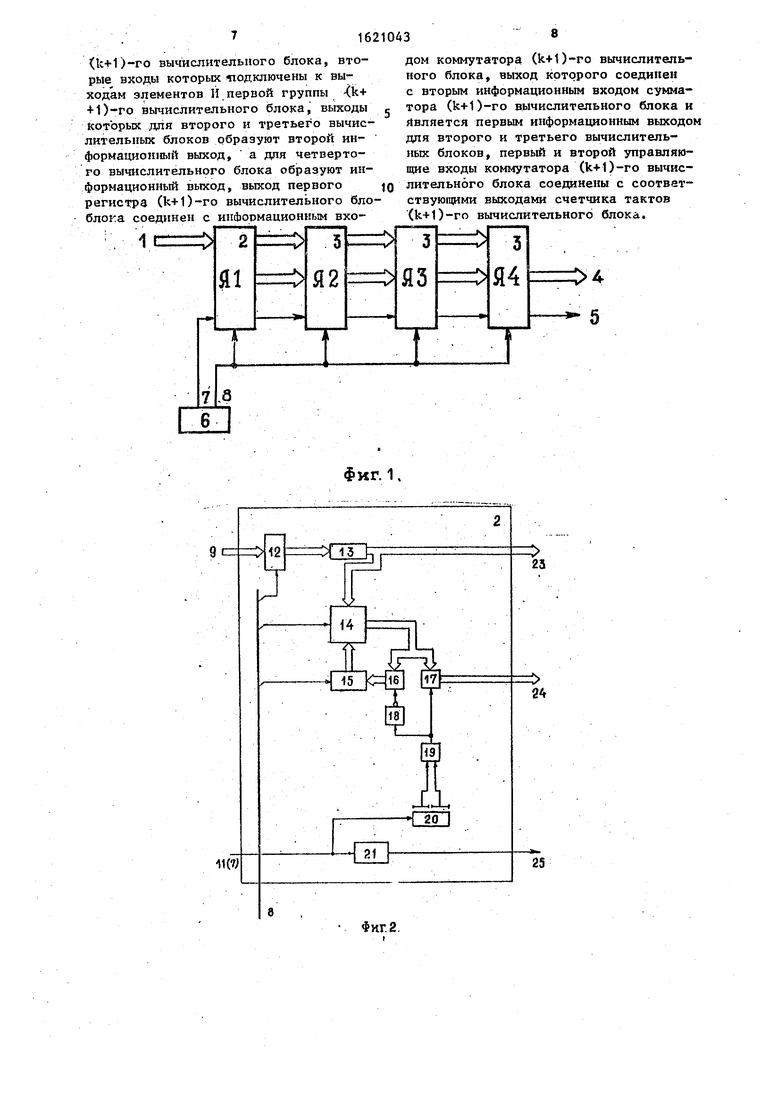

На фиг.1 представлена функциональная схема систолического процессора четырехточечного дискретного преобразования Фурье; на фкг.2 - функциональная схема первого вычислительного блока; на фиг.З - функциональная схема (k-M)-ro (k 1, 3) вычислительного блока; на фиг.4 - функциональная схема коммутатора; на фиг.5 - динамика работы вычислительных блоков по тактам; на фиг.6 - временная диаграмма работы вычислительных блоков.

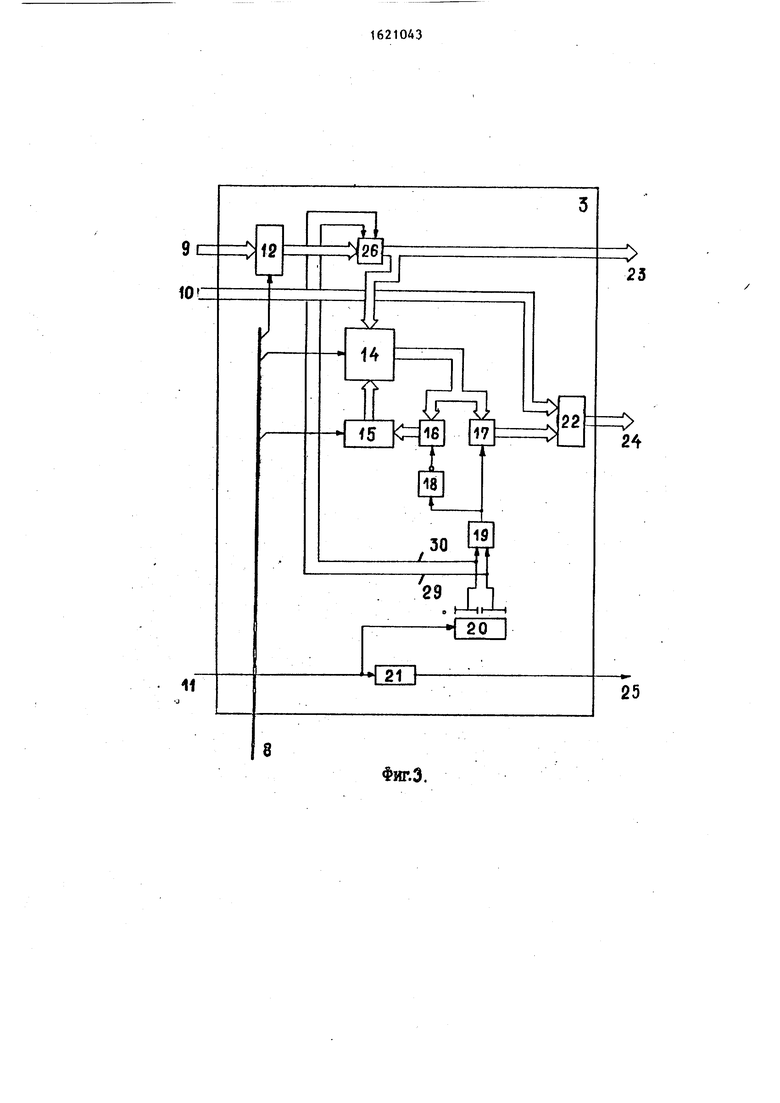

Процессор содержит информационный вход 1, первый вычислительный блок 2, с второго по четвертый вычислительные блоки 3, информационный выход 4, управляющий выход 5, блок 6 синхронизации, второй 7 и первый 8 выходы блока синхронизации.

Вычислительные блоки 2 и 3содяр- жат информационные входы 9 и 10, второй вход 11 сшгхронизации,первый регистр 12, блок 13 задержки, сумматор 14, второй регистр 15, группы 16 и 17 элементов И, элемент НЕ 18, элемент И 19, счетчик 20, элемент 21 задержки, группу 22 элементов ИЛИ, информационные выходы 23, 24, управляющий выход 25 и коммутатор 26.

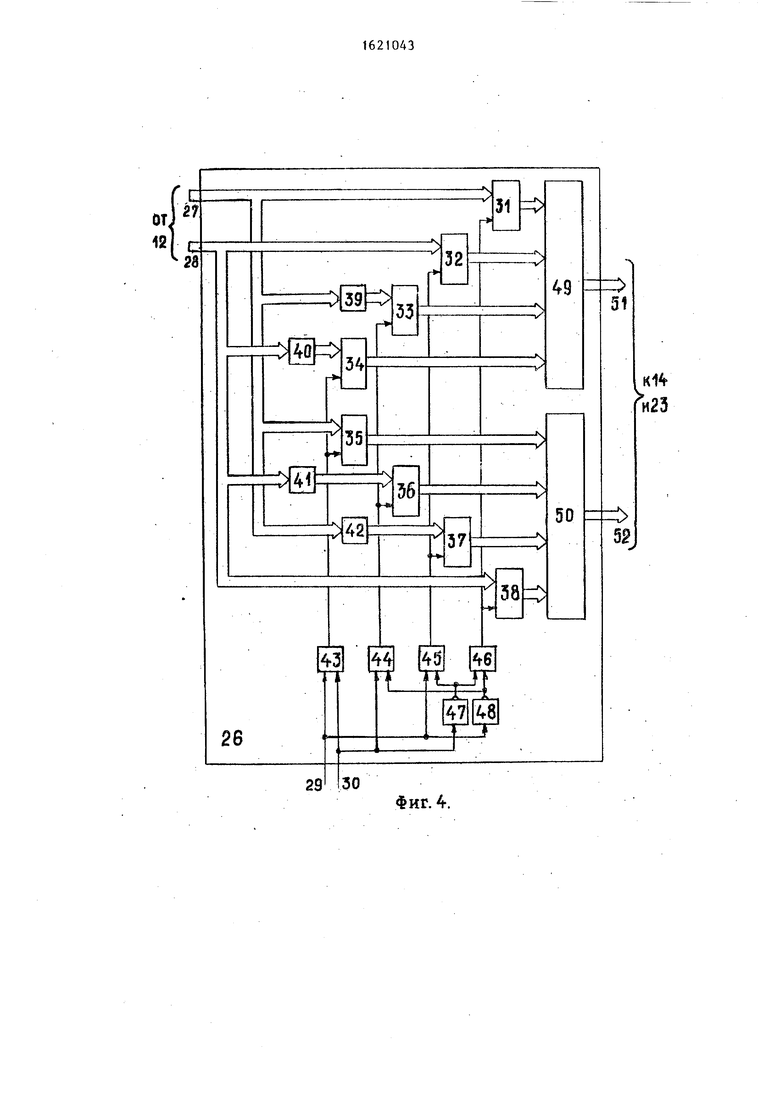

Коммутатор 26 содержит входь; 27 и 28 вещественной и мнимой частей комплексного числа, управляющие входы 29

о

N3

Јь

00

3162

И 30, группы элементов И 31-38, группы элементов НЕ 39-«4 2, элементы И 43 - 46, элементы НЕ 47 и 48, группы элементов ИЛИ 49 и 50 и выходы 51 и 52 (фиг.4).

Систолический процессор четырехточечного дискретного преобразования Фурье работает следующим образом.

Устройство осуществляет выполнение процедуры ДПФ:

Y2 K,K0bV K,K0(-a) V K,Ko(-b)V VK,K0 a,(2)

где Y и Y - функция коммутатора по выходам.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный систолический процессор для вычисления полиномиальных функций | 2020 |

|

RU2737236C1 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

| Процессор для цифровой обработки сигналов | 1985 |

|

SU1257662A1 |

| Устройство параллельной обработки видеоинформации | 1989 |

|

SU1651299A1 |

| Процессор для умножения вектора на матрицу размером S @ N | 1990 |

|

SU1751780A1 |

| Систолический процессор для двумерного дискретного преобразования Фурье | 1988 |

|

SU1608688A1 |

| Систолический процессор дискретного преобразования Фурье | 1989 |

|

SU1615741A1 |

| Поточно-параллельный процессор Хаара | 1989 |

|

SU1756901A1 |

| Многоканальный цифровой фильтр | 1990 |

|

SU1751781A1 |

| Процессор быстрого преобразования Фурье | 1988 |

|

SU1667101A1 |

Изобретение относится к вычислительной технике и может быть использовано в специапизированных системах обработки сигналов высокой производительности. Целью изобретения является сокращение аппаратурных затрат за счет выведения из структуры систолического процессора умножителей. Поставленная цель достигается тем, что в систолическом процессоре для вычисления четырехточечного ДПФ, состоящем из четырех линейно связанных вычислительных блоков, каждая ячейка матрицы содержит дополнительно группу элементов ИЛИ, коммутатор, две группы элементов И, элемент И, элемент НЕ, блок задержки тактов, элемент задержки. 6 ил., 1 табл. i (Л

EdX,

(1)

где С и X - четырехкомпонентные век- торы, т.е.

Х хо х .

I- векторы разС со, С, , С2, С J мера 4x1,

компоненты которых определяют информацию на входе и выходе систолической матрицы;

Е, - матрица дискретных экспоненциальных функций (ДЗФ) 4-го порядка с элементами 1 W -exp (-j2«kn/ /4); k,n 6 0,3, т.е.

Умножение осуществляется на тривиальные множители 1,-1, j, -J. Роль умножителя в предлагаемой систолической матрице выполняет коммутатор 26. 40 Компоненты вектора входных данных представляют собой комплексные числа, т.е. х а + Ъ,где а Re(x) - вещественная, a b Im(x) - мнимая части комплексного числа. На входы 4$ 27 и 28 коммутатора поступают вещественная а и мнимая b части комплексного операнда х. В качестве инициирующих сигналов коммутатора выступают сигналы KQ и К, двухразрядного счет- 50 чика 20 и в зависимости от комбинации К0К( (см. таблицу) формируется результат Y и Ye на выходах Ы и 52 коммутатора 26 соответственно, а именно :55

Y K,K0aV K,K0bv K,K0(-a)V VK,K0(-b);

0

5

0 $ 0 5

Входной операнд х поступает на входной регистр 12 первого блока 2 (фиг.2) в первый такт времени (фиг,5) и с задержкой на блоке 13, равной за- держке коммутатора 26, передается на выход 23 блока 2 и соответственно на регистр 12 второго блока 3, а также поступает на первый вход сумматора 14. В первом такте просходит сложе- ние хй с 0, поступающим на второй вход сумматора из регистра 15, далее с выхода сумматора х0 поступает через открытую группу элементов И 16 на информационный вход регистра 15. В первом такте времени состояние счетчика 00 и, следовательно, на вторых входах элементов И 17, имеются запрещающие О, а на вторых входах И 16 - разрешающие 1. Во втором такте включается в работу второй блок 3 (фиг.З), при этом счетный импульс с задержкой в один такт на элементе 21 первого блока 2 приходит на счетный вход счетчика 20 второго блока 3. В этом такте состояние счетчика первого блока 01, а второго блока - 00. Таким образом, входной операнд х„ во втором блоке, проходя через коммутатор 26 (управляющие сигналы 00) умножается на +1, в первом блоке во втором такте происходит сложение входного операнда х с накопленным х0 и запись хо + х в регистр 5. В третьем такте (фиг.5) включается в работу третий блок 3, при этом с учетом задержки счетного импульса состояние счетчиков первого, второго и третьего вычислительных блоков 10, 01, 00. В этом

5К

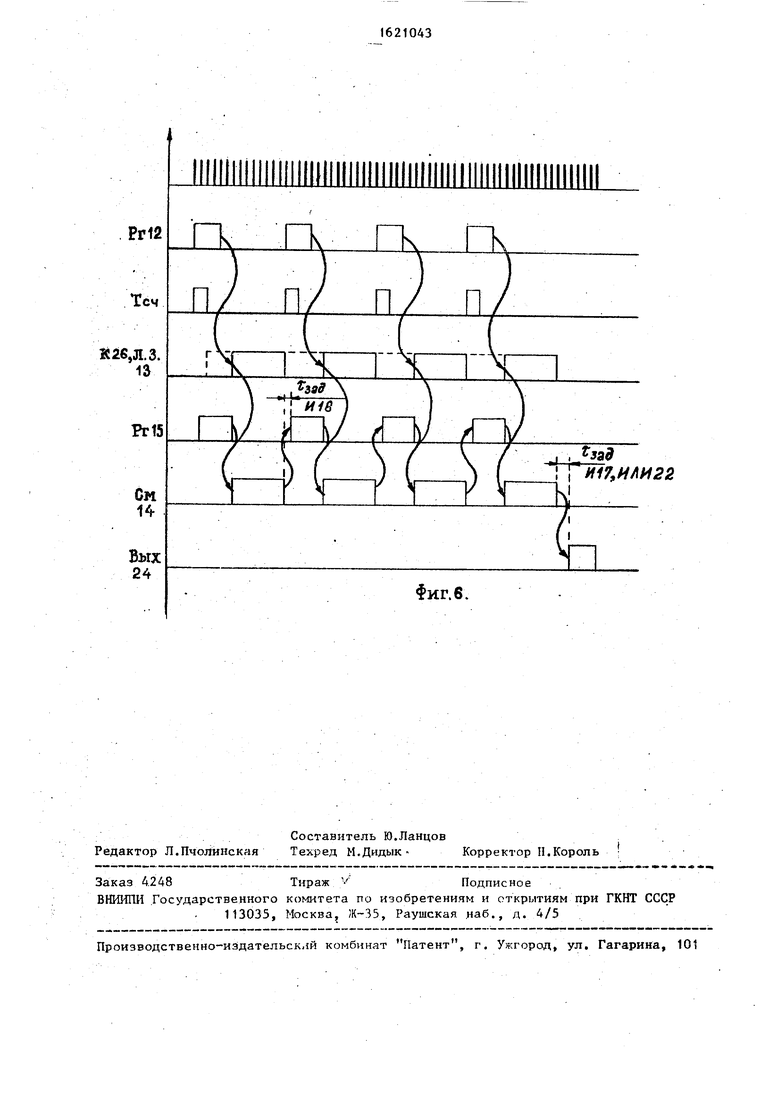

такте и парном блоке 2 в регистре 15 записывается сумма (х0 + х( + + х), но втором бпоке 3 входной операнд х( , проходя через коммутатор (управляющие сигналы 01) умножается на -j, складывается с х0 и результат записывается в регистр 15, п третьем блоке 2 в этом такте входной операнд х0 , проходя через коммутатор, домножается на + 1 , складывается с 0 и записывается в регистр 15. R четвертом такте работают все четыре вычислительных блока, причем согто- ,яиие счетчиков 11, 10, 01, и результат суммы (хо + х + х3) в первом блоке 2 с выхода сумматора через открытие элементы И 17 (элементы И 16 закрыты управляющим нулем), выход 24, вход 10 второго блока 3, элементы ИЛИ 22, выход 24 второго блока 3 и т.д. проходит через систолический процессор в виде результата на пыход 4. Во втором блоке 3 в этом такте в регистре 1Ь формируется сумма (х0 - j -,-, - х), а в третьем блоке 3 - (х0 - х). В пятом такте формируется результат во втором блоке и через открытые элементы И 17, элементы ИЛИ 22, выход 24, вход 10 третьего блока 3 и т.д. проходит на выход 4 систопического процессора. В шестом и седьмом тактах формируется результат в третьем и четвертом блоках 3 соответственно (фиг.5). На фиг.6 представлена временная диаграмма четырех тактов работы одного вычислительного блока систолического процессора.

Формула изобретения

Систолический процессор для вычисления четырехточечного дискретног преобразования Фурье, содержащий четыре вычислительных блока и блок синхронизации, причем информационный вход процессора подключен к информационному входу первого вычислительного блока, первый вход синхронизации которого соединен с первыми входами синхронизации с второго по четвертый вычислительных блоков и с первым выходом блока синхронизации,первый и второй информационные выходы k-го (k 1,3) вычислительного блока соединены соответственно с первым и вторым информационными входами (k+1) го вычислительного блока, информаци0436

сними выход четвертого вычис-литетми о- го блока является информационным иы- ходом процессора, при этом каждый вы- числительный блок содержит два регистра и сумматор, первый информационный вход вычислительного блока подключен к информационному «ходу первого регистра, выход второго регистра

JQ соединен с первым информационным входом сумматора,синхровход которого соединен с синхрон ход ft ми первого и второго регистров и является первым входом синхронизации вычислительного бло15 ка, о т л и ч а ю ц и и с л тем, что, с целью сокращения аппаратурных затрат, второй выход блока синхронизации соединен с вторым входом синхронизации первого вычислительного

20 блока, управляющий выход k-ro вычислительного блока соединен с вторым входом синхронизации (k-H)-ro вычислительного блока, управляющий выход четвертого вычислительного блока яв25 ляется управляющим выходом процессора, причем ка чдьтн вычислительный блок дополнительно содержит две группы элементов И, элемент НЕ, элемент И, счетчик тактов и элемент -задержки,

30 причем выход элемента -задержки является управляющим выходом каждого вычислительного бнока, второй вход синхронизации которого соединен с входом элемента задержки и со счетным входом счетчика тактом, выходы которого соединены с входами элемента И, выход которого соединен с первыми входами элементов II первой группы и через элемент НЕ - с первыми входами

4Q элементов И второй iруппы, выходы которых соединены с информационными входами второго регистра, выходы сумматора соединены с вторыми входами элементов И первой и второй групп,

дд кроме этого, первый вычислительный блок дополнительно содержит блок задержки, причем выход первого регистра через блок задержки соединен с вторым информационными входом сумматора и с

50 первым информационным выходом парного вычислительного блока, второй информационный выход которого образован выходами элементов И первом группы, кроме этого (k+0-й вычислит ольный

cj блок дополнительно содержит коммутатор и группу элементов ИЛИ, причем второй информационный вход (k-H)-ro вычислительного блока соединен с первыми входами элементов ИЛИ группы

35

1C

Я1

Я2

ш

Фиг. 1.

3

яз

Я4

РД

25

Фиг.З.

OTJ 12

к14 гЪ

Фиг. 4.

vT

y. n

Й

LO

fe

.Ц

4

H

Ю

;;

e«

РП2

Тсч

К2в,Л.З.

ia

) за9

ГИ17,ИЛИ22

Фиг. 6.

| Устройство для цифровой фильтрации | 1984 |

|

SU1196894A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Тезисы докладов Всесоюзной конференции Методы и микроэлектронные средства цифрового преобразования обработки сигналов.-Рига | |||

| Пневматический водоподъемный аппарат-двигатель | 1917 |

|

SU1986A1 |

Авторы

Даты

1991-01-15—Публикация

1988-05-23—Подача