фиг 1

Изобретение относится к вычислительной технике и может быть использовано при построении высокопроизводительных систем обработки цифровой информации.

Цель изобретения - увеличение быстродействия.

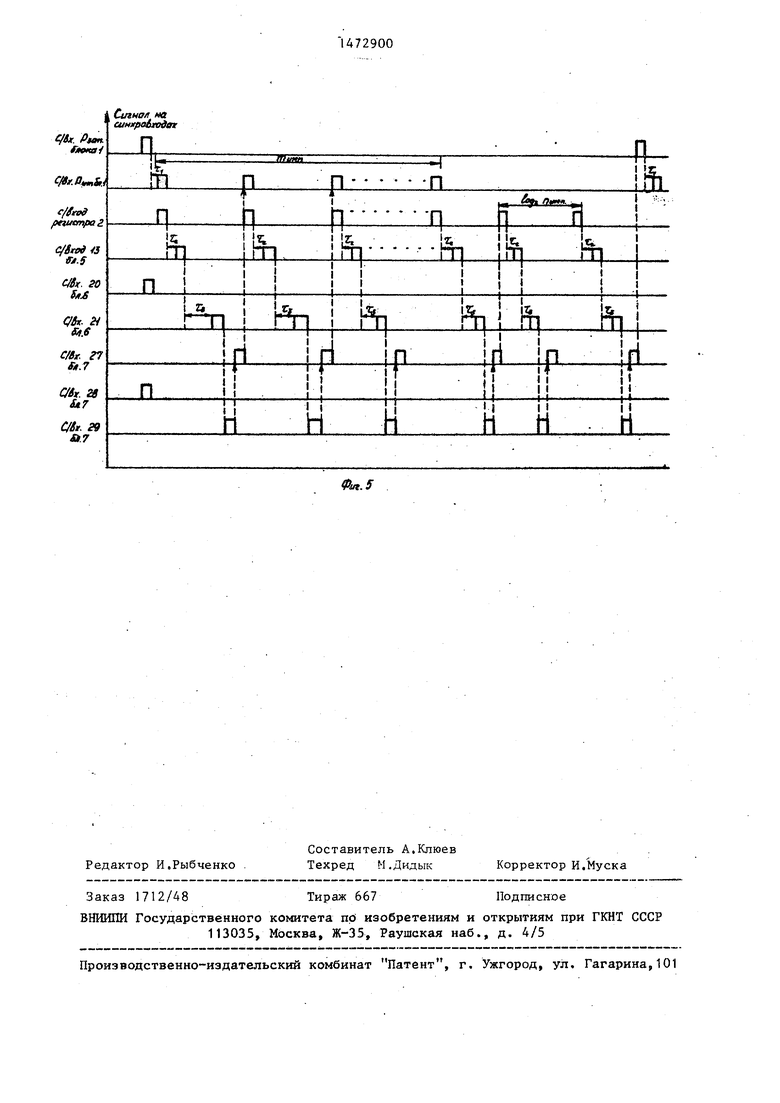

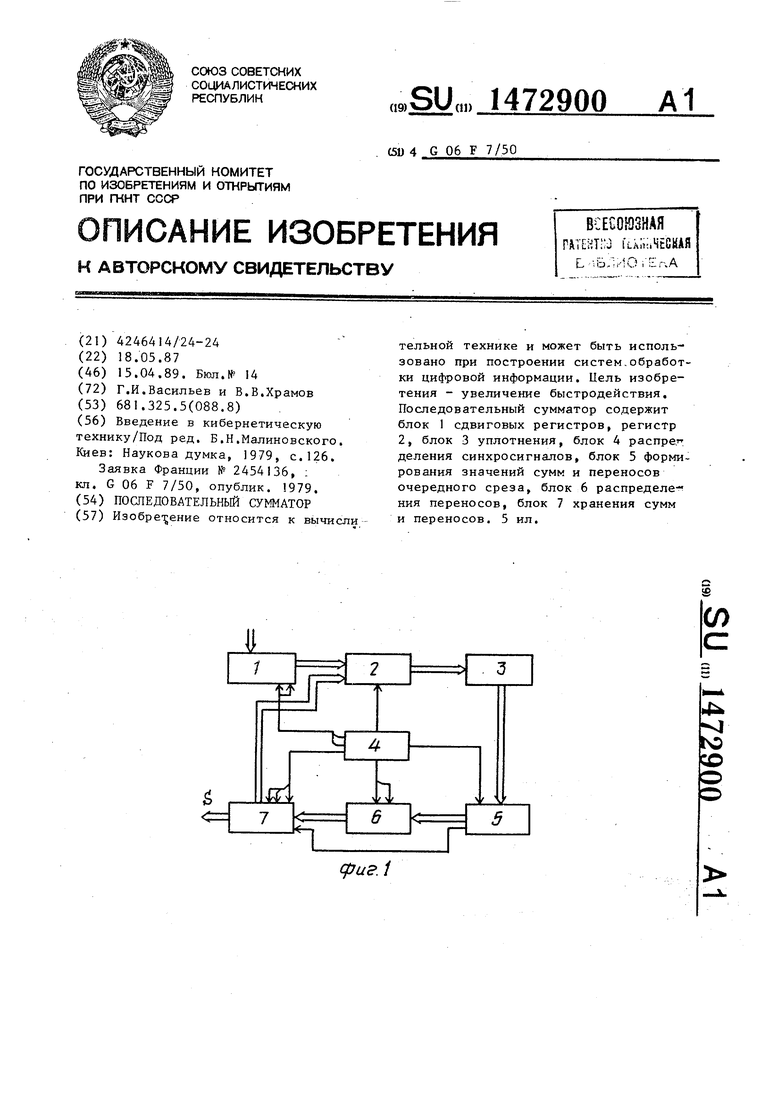

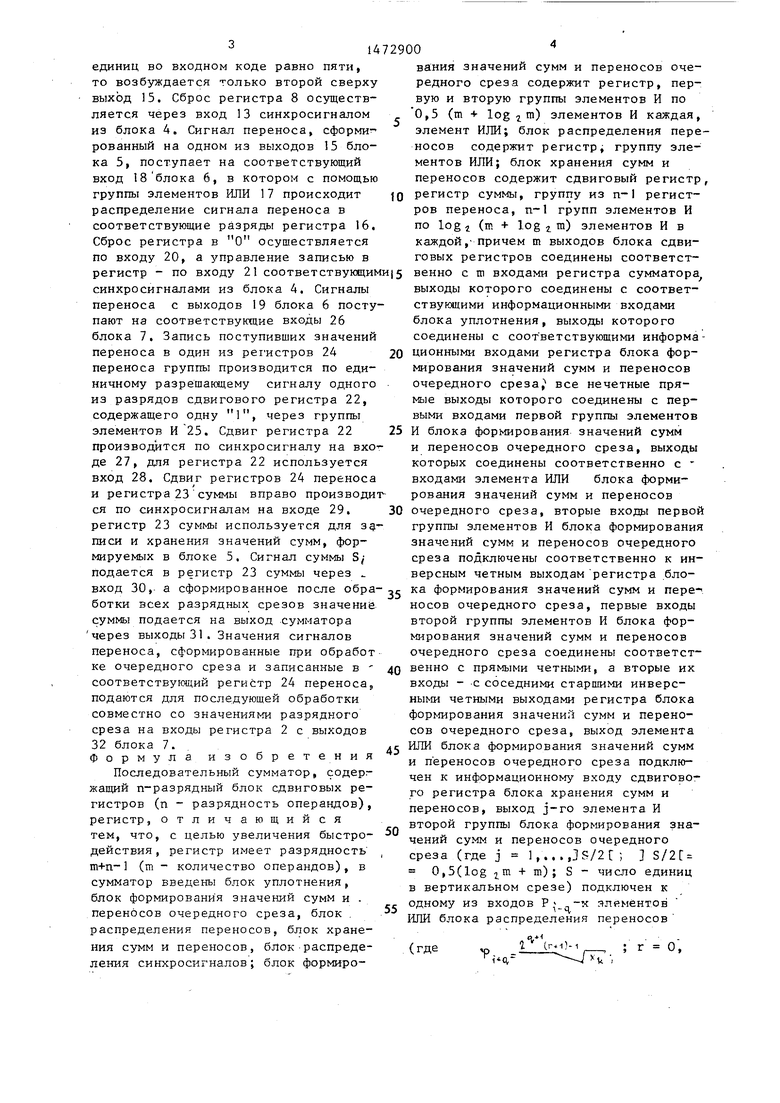

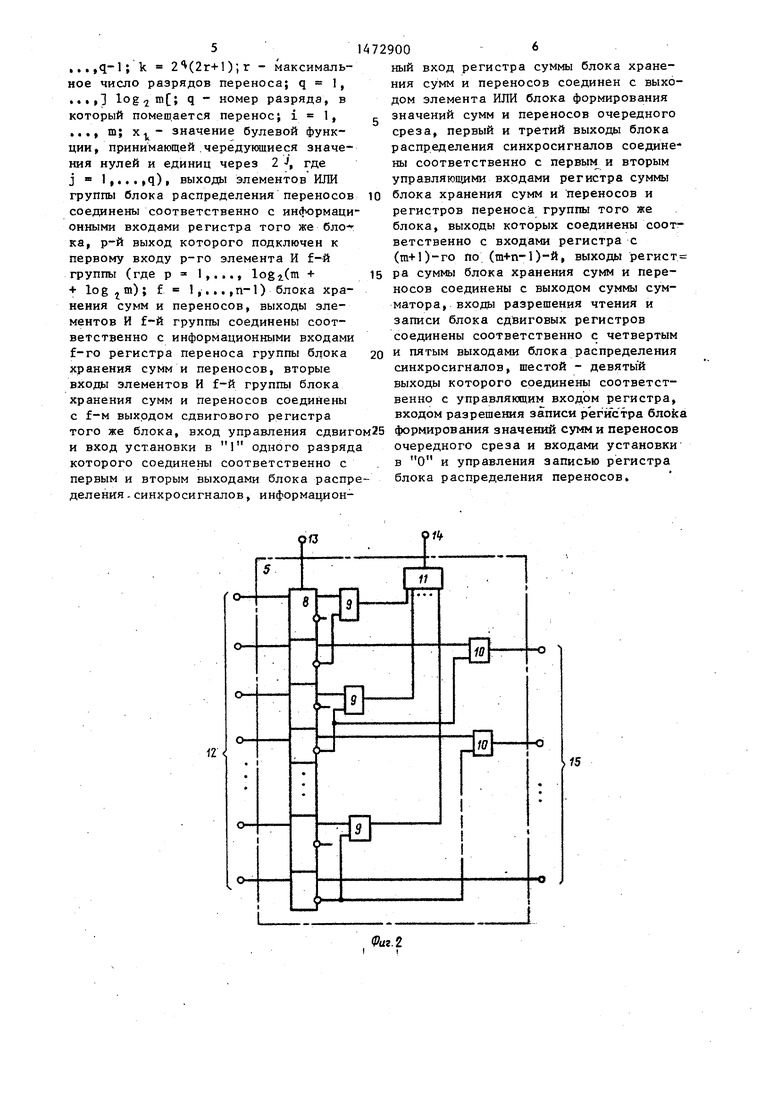

На фиг.1 представлена структурная схема последовательного сумматора; на фиг.2 - Функциональная схема блока формирования значений сумм и переносов очередного среза; на фиг.З- функциональная схема блока распределения переносов; на фиг.4 - функцио- напьная схема блока хранения сумм и переносов; -на фиг.5 - временная диаграмма работы блока распределения синхросигналов.

Последовательный сумматор (фиг.1) содержит блок 1 сдвиговых регистров, регистр 2, блок 3 уплотнения, блок 4 распределения синхросигналов, блок 5 формирования значений сумм и переносов очередного среза, блок 6 рас-. пределения переносов, блок 7 хранени сумм и переносов.

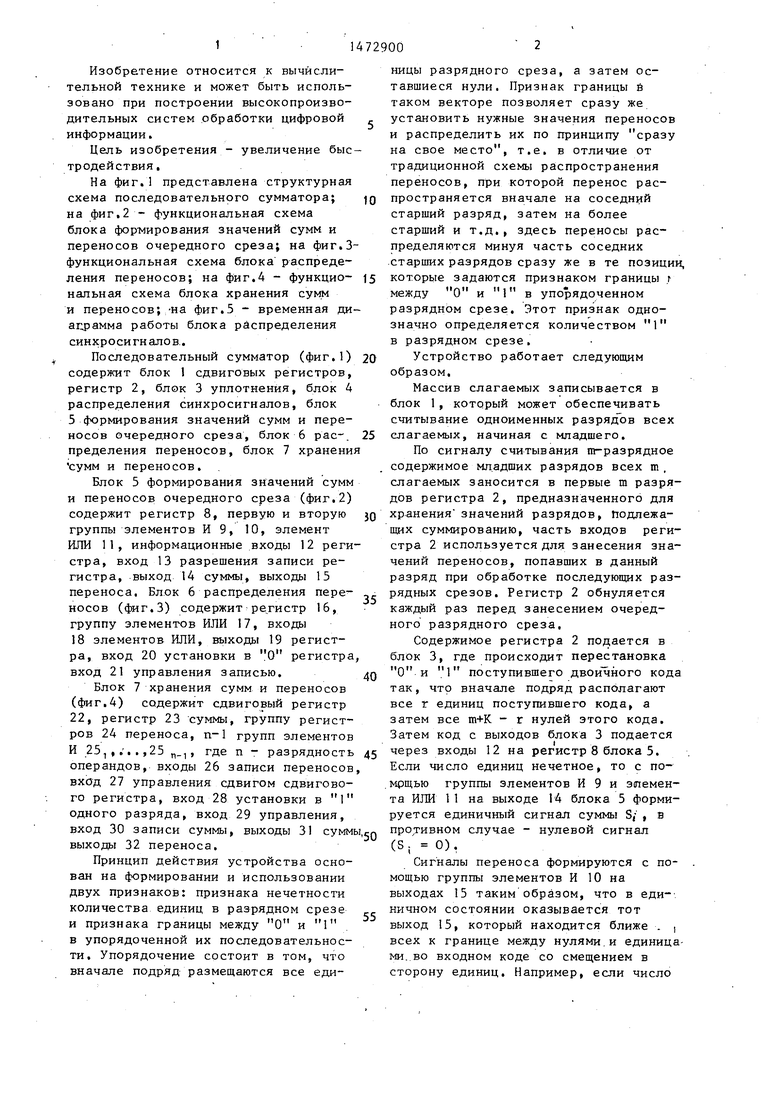

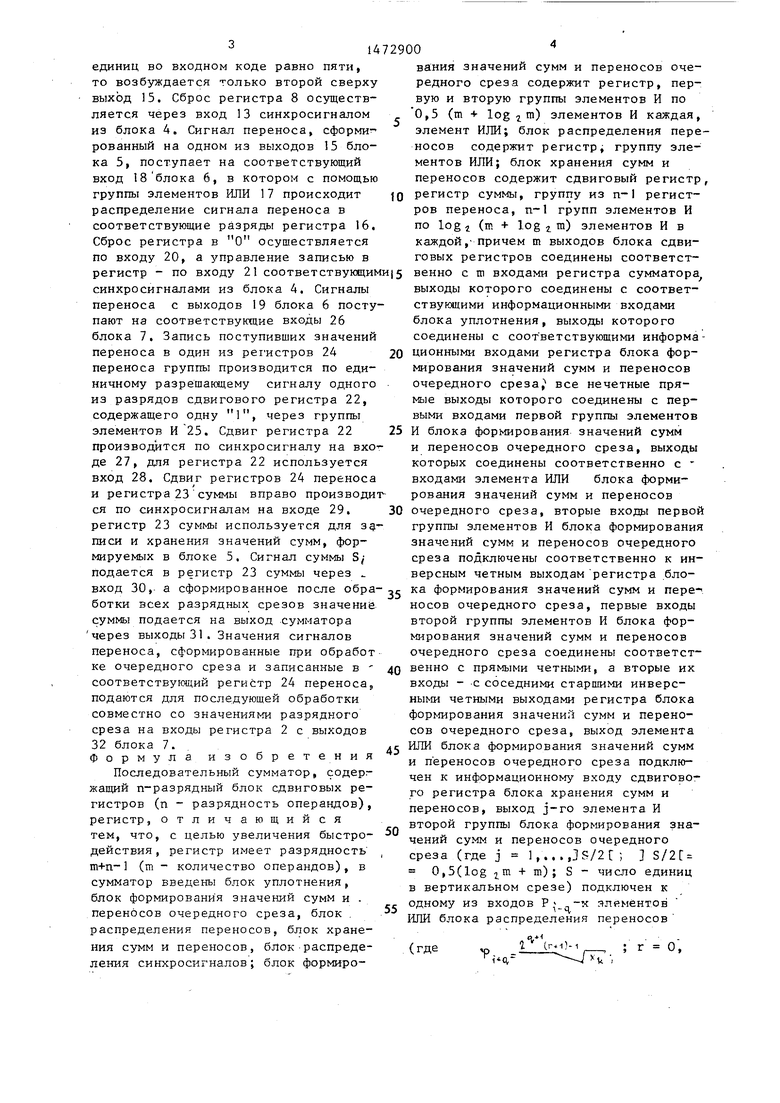

Блок 5 формирования значений сумм и переносов очередного среза (фиг,2) содержит регистр 8, первую и вторую группы элементов И 9, 10, элемент ИЛИ 11, информационные входы 12 регистра, вход 13 разрешения записи регистра, выход 14 суммы, выходы 15 переноса. Блок 6 распределения переносов (фиг.З) содержит регистр 16, группу элементов ИЛИ 17, входы 18 элементов ИЛИ, выходы 19 регистра, вход 20 установки в О регистра вход 21 управления записью.

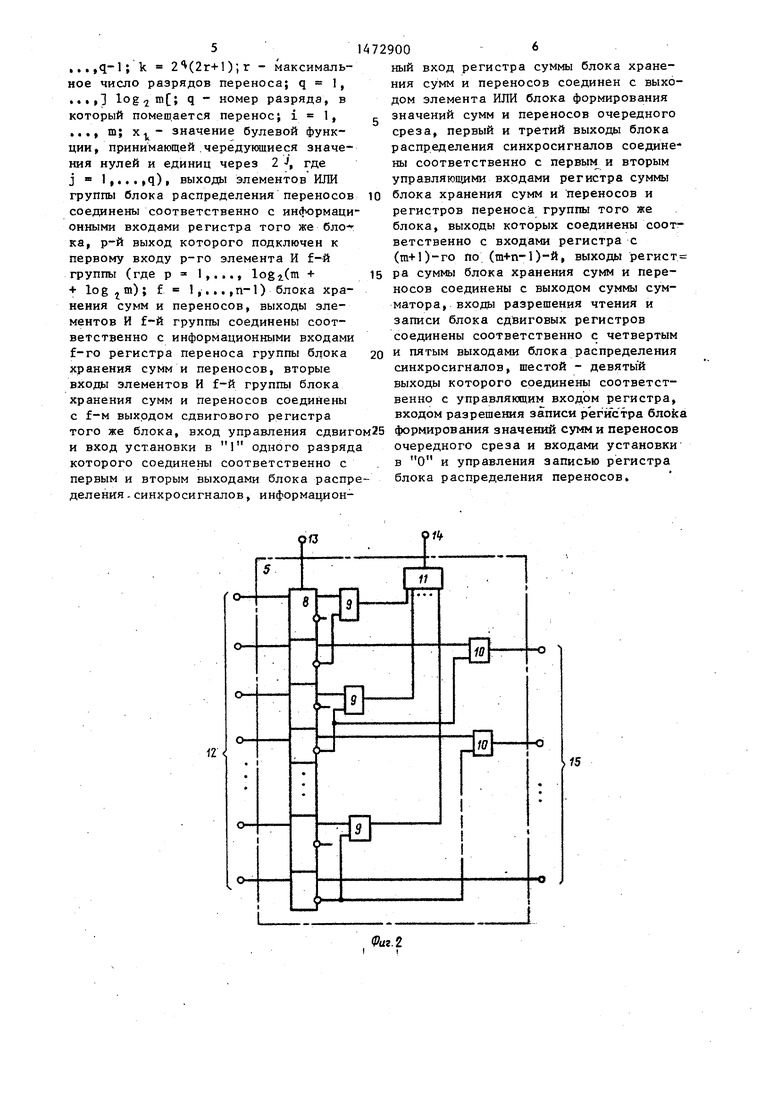

Блок 7 хранения сумм и переносов (фиг.4) содержит сдвиговый регистр 22, регистр 23 суммы, группу регистров 24 переноса, п-1 групп элементов И 25, ,.. . ,25 п,, где п - разрядность операндов, входы 26 записи переносов вход 27 управления сдвигом сдвигового регистра, вход 28 установки в 1 одного разряда, вход 29 управления, вход 30 записи суммы, выходы 31 сумм выходы 32 переноса.

Принцип действия устройства основан на формировании и использовании двух признаков: признака нечетности количества единиц в разрядном срезе и признака границы между О и 1 в упорядоченной их последовательности. Упорядочение состоит в том, что вначале подряд размещаются все еди

g 5

0 5

Q о

5

5

ницы разрядного среза, а затем оставшиеся нули. Признак границы и таком векторе позволяет сразу же установить нужные значения переносов и распределить их по принципу сразу на свое место, т.е. в отличие от традиционной схемы распространения переносов, при которой перенос распространяется вначале на соседний старший разряд, затем на более старший и т.д., здесь переносы распределяются минуя часть соседних старших разрядов сразу же в те позиции, которые задаются признаком границы t между О и 1м в упорядоченном разрядном срезе. Этот признак однозначно определяется количеством 1 в разрядном срезе.

Устройство работает следующим образом.

Массив слагаемых записывается в блок 1, который может обеспечивать считывание одноименных разрядов всех слагаемых, начиная с младшего.

По сигналу считывания т-разрядное содержимое младших разрядов всех т , слагаемых заносится в первые m разрядов регистра 2, предназначенного для хранения значений разрядов, подлежащих суммированию, часть входов регистра 2 используется для занесения значений переносов, попавших в данный разряд при обработке последующих разрядных срезов. Регистр 2 обнуляется каждый раз перед занесением очередного разрядного среза.

Содержимое регистра 2 подается в блок 3, где происходит перестановка О и 1 поступившего двоичного кода так, что вначале подряд располагают все г единиц поступившего кода, а затем все m+К - г нулей этого кода. Затем код с выходов блока 3 подается через входы 12 на регистр 8 блока 5. Если число единиц нечетное, то с помощью группы элементов И 9 и элемента ИЛИ 11 на выходе 14 блока 5 формируется единичный сигнал суммы S/ , в пробивном случае - нулевой сигнал

(Sj 0).

Сигналы переноса формируются с помощью группы элементов И 10 на выходах 15 таким образом, что в единичном состоянии оказывается тот выход 15, который находится ближе . , всех к границе между нулями и единицами во входном коде со смещением в сторону единиц. Например, если число

единиц во входном коде равно пяти, то возбуждается олько второй сверху выход 15. Сброс регистра 8 осуществляется через вход 13 синхросигналом из блока 4. Сигнал переноса, сформи- рованный на одном из выходов 15 блока 5, поступает на соответствующий вход 18 блока б, в котором с помощью группы элементов ИЛИ 17 происходит распределение сигнала переноса в соответствующие разряды регистра 16. Сброс регистра в О осушествляется по входу 20, а управление записью в

вания значений сумм и переносов очередного среза содержит регистр, первую и вторую группы элементов И по 0,5 (m + log гт) элементов И каждая, элемент ИЛИ; блок распределения переносов содержит регистр, группу элементов ИЛИ; блок хранения сумм и переносов содержит сдвиговый регистр, регистр суммы, группу из п-1 регистров переноса, п-1 групп элементов И по log 4 (т + log г т) элементов И в каждой, причем m выходов блока сдвиговых регистров соединены соответст

| название | год | авторы | номер документа |

|---|---|---|---|

| Ассоциативное устройство для суммирования массива чисел | 1988 |

|

SU1564615A1 |

| Преобразователь @ -ичного позиционного кода в двоичный код | 1983 |

|

SU1115045A1 |

| Устройство для умножения двоичных чисел | 1989 |

|

SU1784973A1 |

| Суммирующее устройство | 1987 |

|

SU1451681A1 |

| Устройство для умножения @ -разрядных двоичных чисел | 1990 |

|

SU1783519A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Арифметическое устройство | 1984 |

|

SU1236473A1 |

| Устройство для вычисления произведения векторов (его варианты) | 1984 |

|

SU1280389A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Делительное устройство | 1983 |

|

SU1198512A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении систем обработки цифровой информации. Цель изобретения - увеличение быстродействия. Последовательный сумматор содержит блок 1 сдвиговых регистров, регистр 2, блок 3 уплотнения, блок 4 распределения синхросигналов, блок 5 формирования значений сумм и переносов очередного среза, блок 6 распределения переносов, блок 7 хранения сумм и переносов. 5 ил.

регистр - по входу 21 соответствующими венно с m входами регистра сумматора,

синхросигналами из блока 4. Сигналывыходы которого соединены с соответпереноса с выходов 19 блока 6 посту-ствующими информационными входами

пают на соответствующие входы 26блока уплотнения, выходы которого

блока 7. Запись поступивших значений переноса в один из регистров 24 переноса группы производится по единичному разрешающему сигналу одного из разрядов сдвигового регистра 22, содержащего одну 1, через группы элементов И 25. Сдвиг регистра 22 производится по синхросигналу на вхо- де 27, для регистра 22 используется вход 28. Сдвиг регистров 24 переноса и регистра 23 суммы вправо производится по синхросигналам на входе 29. регистр 23 суммы используется для записи и хранения значений сумм, формируемых в блоке 5. Сигнал суммы S; подается в регистр 23 суммы через

вход 30, а сформированное после обра-,,- ка формирования значений сумм и пере

ботки всех разрядных срезов значение суммы подается на выход сумматора через выходы 31. Значения сигналов переноса, сформированные при обработ ке очередного среза и записанные в - соответствующий регистр 24 переноса, подаются для последующей обработки совместно со значениями разрядного среза на входы регистра 2 с выходов

32 блока 7.

Формула изобретения

Последовательный сумматор, содержащий n-разрядный блок сдвиговых регистров (п - разрядность операндов), регистр, отличающийся тем, что, с целью увеличения быстродействия, регистр имеет разрядность m+n-I (m - количество операндов), в сумматор введены блок уплотнения t блок формирования значений сумм и . переносов очередного среза, блок распределения переносов, блок хранения сумм и переносов, блок распределения синхросигналов; блок формироносов очередного среза, первые входы второй группы элементов И блока формирования значений сумм и переносов очередного среза соединены соответст40 венно с прямыми четными, а вторые их входы - с соседними старшими инверсными четными выходами регистра блока формирования значений сумм и переносов очередного среза, выход элемента

д5 ИЛИ блока формирования значений сумм и переносов очередного среза подключен к информационному входу сдвигового регистра блока хранения сумм и переносов, выход j-го элемента И второй группы блока формирования значений сумм и переносов очередного среза (где j 1,...,JS/2 Г 5 S/2O 0,5(log ггс + m); S - число единиц в вертикальном срезе) подключен к

50

55

одному из входов Р -х члрментов ИЛИ блока распределения переносов

(где

V (

г О,

соединены с соответствующими информа- ционными входами регистра блока формирования значений сумм и переносов очередного среза все нечетные прямые выходы которого соединены с первыми входами первой группы элементов И блока формирования значений сумм и переносов очередного среза, выходы которых соединены соответственно с входами элемента ИЛИ блока формирования значений сумм и переносов очередного среза, вторые входы первой группы элементов И блока формирования значений сумм и переносов очередного среза подключены соответственно к инверсным четным выходам регистра блоносов очередного среза, первые входы второй группы элементов И блока формирования значений сумм и переносов очередного среза соединены соответст0 венно с прямыми четными, а вторые их входы - с соседними старшими инверсными четными выходами регистра блока формирования значений сумм и переносов очередного среза, выход элемента

5 ИЛИ блока формирования значений сумм и переносов очередного среза подключен к информационному входу сдвигового регистра блока хранения сумм и переносов, выход j-го элемента И второй группы блока формирования значений сумм и переносов очередного среза (где j 1,...,JS/2 Г 5 S/2O 0,5(log ггс + m); S - число единиц в вертикальном срезе) подключен к

0

55

одному из входов Р -х члрментов ИЛИ блока распределения переносов

(где

V (

г О,

..,q-l; k (2r+l); г - максимальное число разрядов переноса; q 1, ,.., Iog2m ; q - номер разряда, в который помешается перенос; , ..., т; х-ц- значение булевой функции, принимающей чередующиеся значения нулей и единиц через 2 J, где j .q)i выходы элементов ИЛИ группы блока распределения переносов соединены соответственно с информационными входами регистра того же бло- ка, р-й выход которого подключен к первому входу р-го элемента И f-й группы (где р 1,..., logiCm + + lo g г m) ; f « 1,..., п-1) блока хранения сумм и переносов, выходы элементов И f-й группы соединены соответственно с информационными входами f-ro регистра переноса группы блока хранения сумм и переносов, вторые входы элементов И f-й группы блока хранения сумм и переносов соединены с f-м выходом сдвигового регистра того же блока, вход управления сдвиг и вход установки в 1 одного разряд которого соединены соответственно с первым и вторым выходами блока распрделения ,синхросигналов, информационQf3

1Z

ный вход регистра суммы блока хранения сумм и переносов соединен с выходом элемента ИЛИ блока формирования значений сумм и переносов очередного среза, первый и третий выходы блока распределения синхросигналов соединены соответственно с первым и вторым управляющими входами регистра суммы блока хранения сумм и переносов и регистров переноса группы того же блока, выходы которых соединены соответственно с входами регистра с (т-И)-го по (т+п-1)-й, выходы регист ра суммы блока хранения сумм и переносов соединены с выходом суммы сумматора, входы разрешения чтения и записи блока сдвиговых регистров соединены соответственно с четвертым и пятым выходами блока распределения синхросигналов, шестой - девятый выходы которого соединены соответственно с управляющим входом регистра, входом разрешения записи регистра блока формирования значений сумм и переносов очередного среза и входами установки в О и управления записью регистра блока распределения переносов.

1

5

ycmtJH.f1

Jan

№

19

.J

Фо

| Введение в кибернетическую технику/Под ред | |||

| Б.Н.Малиновского | |||

| Киев: Наукова думка, 1979, с.126 | |||

| СПОСОБ ПРОИЗВОДСТВА КОМПОТА ИЗ ТКЕМАЛИ, АЛЫЧИ, МИРАБЕЛИ И КИЗИЛА | 2010 |

|

RU2454136C1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Дверной замок, автоматически запирающийся на ригель, удерживаемый в крайних своих положениях помощью серии парных, симметрично расположенных цугальт | 1914 |

|

SU1979A1 |

Авторы

Даты

1989-04-15—Публикация

1987-05-18—Подача