S

ервгн iffro

|

h

v°

nab

8/лоро

геуаай

вюйЗов

Пгрвая lyana тгЈа6

4.

ч

ЬЭ

СО

о со

+

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам (ЗУ), и может быть использовано, например, в процессорах с асинхронным управлением вычислениями для хранения операндов и результатов операций.

Цель изобретения - повышение пропускной способности устройства за счет обеспечения возможности одновременного осуществления операций записи и чтения информации.

На фиг.1 изображена структурная схема ЗУ с динамической адресацией; на фиг.2 - функциональная схема блока управления; на фиг.З - функциональная схема блока буферизации данных и формирования младших разрядов адреса; на фиг.4 - функциональная схема блока буферных регистров,- на фиг.З - взаимодействие ЗУ с динамической адресацией с внешней средой,

ЗУ с динамической адресацией (см. фиг.1) содержит блок 1 буферизации данных и формирования младших разрядов адреса, блок 2 управления, блок 3 памяти (основной информации), первый и второй блоки 4 и 5 памяти количества копий основной информации, блок 6 магазинной памяти для хранения адресов свободных ячеек блока 3, блок 7 буферных регистров. Блок 1 имеет две группы входов 8-11 и 12-15, а также вход 16 тактовых импульсов и выходы 17-28, Блок 2 управления имеет входы 29-35, выход 36, вход 37, выходы 38-40, вход 41, выходы 42 и 43, вход 44, выход 45 и вход 46. Блок 7 буферных регистров имеет входы 47-51 и выходы 52-55.

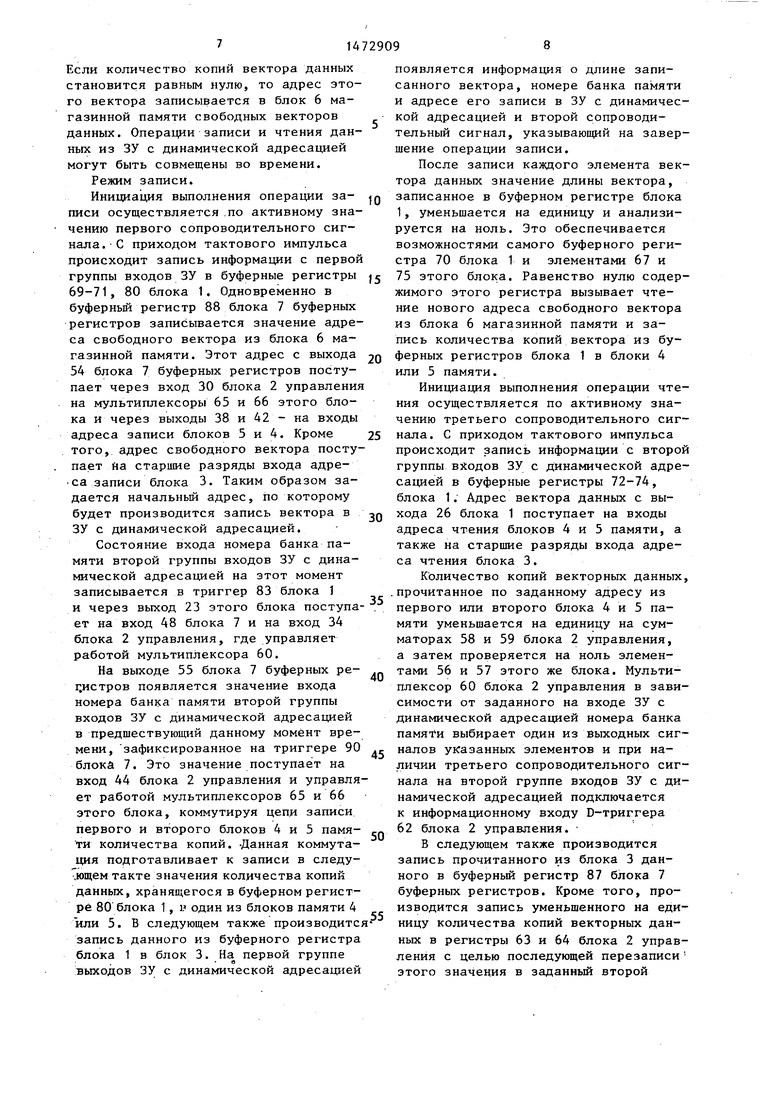

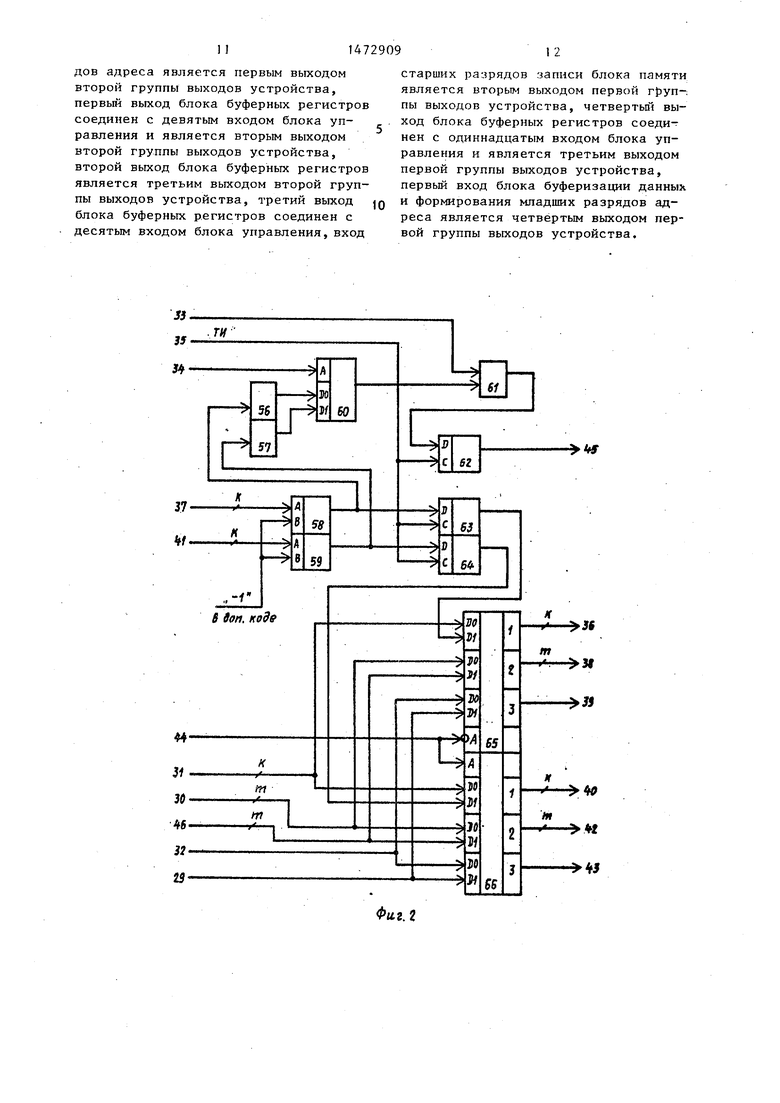

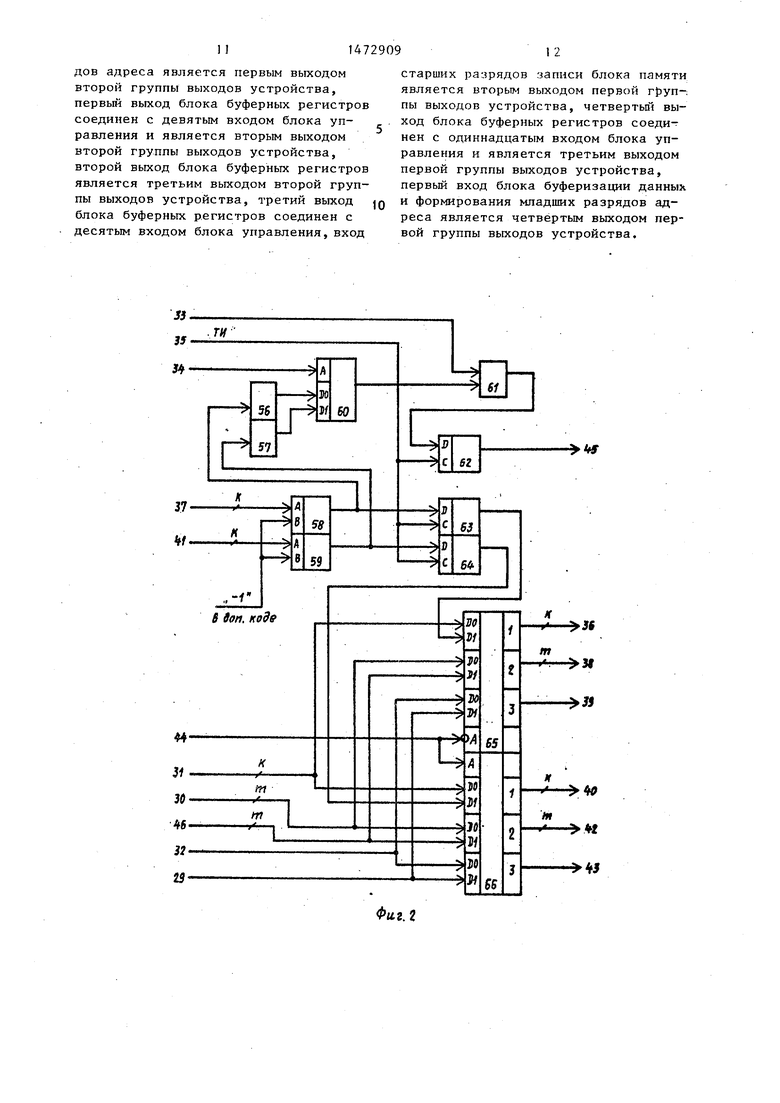

Блок 2 управления (см. фиг.2) содержит элементы 55-66, в том числе мультиплексоры 65 и 66, коммутирующие информационные и управляющие сигналы блоков 4 и 5, сумматоры 58 и 59 и регистры 63 и 64, обеспечивающие уменьшение содержимого вышеуказанных блоков 4 и 5 памяти количества копий на единицу и фиксацию полученных значений, элементы 56 и 57 проверки на ноль, мультиплексор 60, элемент И 61 и D-триггер 62, обеспечивающие выработку сигнала разрешения записи блок 6 магазинной памяти.

Блок 1 (см. фиг.З) содержит элементы 67-84, в том числе буферные регистры входных сигналов ЗУ с динамической адресацией,га также счетчи0

5

0

5

0

5

0

5

0

5

ки длины векторов записываемых и считываемых данных со схемами анализа их содержимого на ноль. Блок 6 магазинной памяти имеет организацию , где т - разрядность адреса вектора основной информации. Блок 7 буферных регистров (см. фиг.4) содержит элементы 85 и 86 задержки, необходимые между фиксаторами конвейерных устройств, а также D-триггеры 87-90 выходных сигналов ЗУ с динамической адресацией.

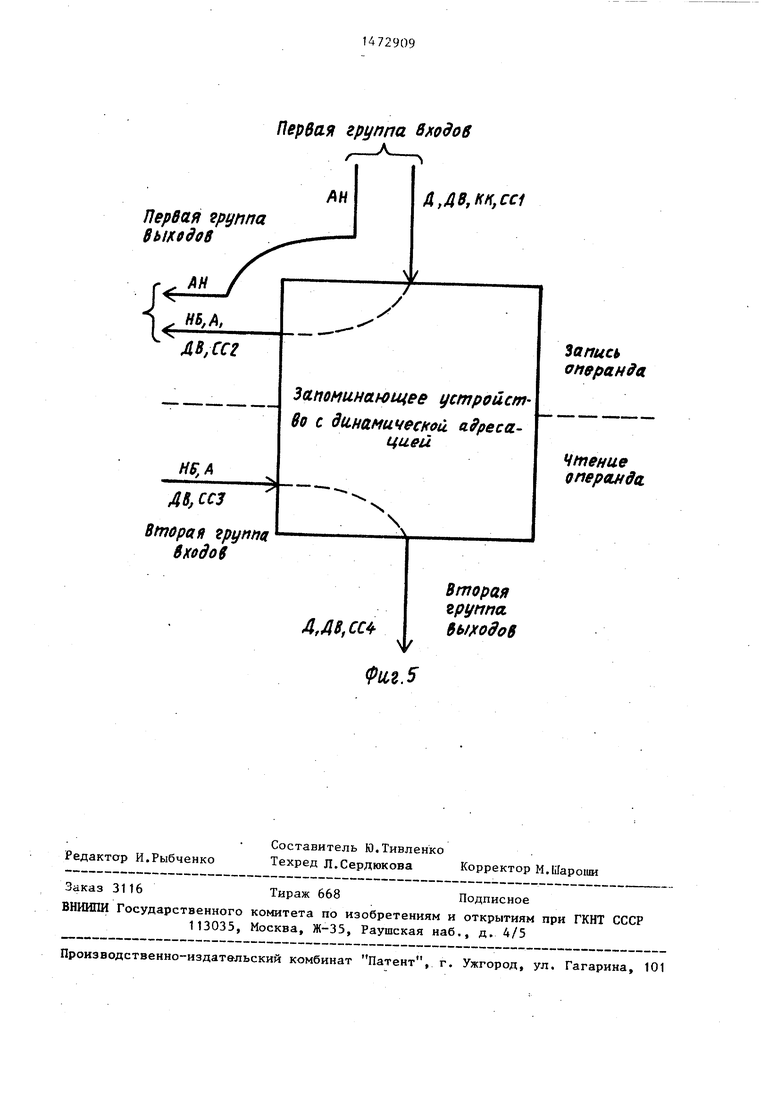

Структура входной информации, поступающей для записи по первой группе входов ЗУ с динамической адресацией, следующая (см. фиг.5): данные основной информации (Д), длина вектора данных (ДВ); количество копий данных (КК), первый сопроводительный сигнал, приход которого указывает на необходимость выполнения операции записи (СС1); адрес назначения, по которому необходимо отослать информацию, находящуюся на первой группе выходов ЗУ с динамической адресацией (АН).

Первая группа выходов ЗУ с динамической адресацией содержит следующую информацию о записанных данных: значение длины вектора записанных данных (ДВ), номер банка памяти, который хранит количество копий записанных данных (НБ); динамически сформированный адрес записанной информации (А), второй сопроводительный сигнал, свидетельствующий о наличии информации на первой группе выходов ЗУ с динамической адресацией (СС2).

Вторая группа входов ЗУ с динамической адресацией предназначена для выполнения операции чтения и содержит адрес требуемых данных (А) , номер банка памяти, хранящий количество копий требуемых данных (НБ); длину вектора данных (ДВ), третий сопроводительный сигнал, свидетельствующий о необходимости выполнения операции чте ния (ССЗ).

Вторая группа выходов ЗУ с динами ческой адресацией предназначена для считывания требуемой информации и содержит прочитанные данные (Д), длину вектора данных (ДВ), четвертый сопроводительный сигнал, свидетельствующий о наличии считываемой информации (СС4).

Количество копий записанных данных указывает на число операций чтения,

необходимых для освобождения ячеек памяти, занятых этими данными.

В устройстве принята следующая система обозначений: п - разрядность данных; t - разрядность регистра длины вектора$ 1 - максимальная длина вектора ( ); К - разрядность регистра количества копий данныхj S - максимальное количество копий данных (); m - разрядность адреса данных.

Запоминающее устройство с динамической адресацией работает следующим образом.

Установка начального состояния запоминающего устройства выполняется один раз перед началом его работы и осуществляется путем многократного выполнения операции чтения из ЗУ по последовательным адресам в интервале от 0 до 2 . В результате блок магазинной памяти полностью заполнен адресами свободных векторов основной информации блока 3.

Выполнение операции записи и считывания происходит в строго определенные моменты времени, задаваемые последовательностью тактовых импульсов, которая подается на вход тактовых импульсов ЗУ с динамической адресацией.

ЗУ с динамической адресацией предназначено для работы в системах конвейерной обработки и представляет собой двухступенчатый конвейер при чтении данных и одноступенчатый конвейер при записи данных. Чтение и запись данных осуществляется одновременно. Данные могут подаваться на вход устройства и сниматься с его выходов каждый машинный такт. С момента поступления информации на входы ЗУ с динамической адресацией до осуществления требуемой операции необходимо два тактовых периода при чтении и один период при записи данных. Вся входная информация, поступающая на вход ЗУ с -динамической адресацией, запоминается в регистрах блока 1 буферизации данных и формирования младших разрядов адреса.

Запись вектора данных производится в свободные ячейки блока 3. Вектор данных записывается в память последовательно по элементам. Регистр длины вектора в блоке 1 буферизации данных и формирования младших разрядов адреса задает смещение для каждого

0

5

0

5

0

5

0

5

0

5

элемента вектора относительно начального адреса вектора данных. Адреса свободных векторов данных блока 3 хранятся в блоке 6 магазинной памяти, и к моменту записи вектора адрес первого свободного вектора подается на старшие разряды адреса записи блока 3. Регистр длины вектора данных подключен к младшим разрядам адреса записи блока 3. После записи каждого элемента вектора данных содержимое регистра уменьшается на единицу. Когда значение регистра длины вектора становится равным нулю, запись вектора прекращается и из блока 6 магазинной памяти извлекается следующий адрес свободного вектора данных.

Каждому вектору данных ставится в соответствие такая характеристика, как количество копий вектора. Количество копий вектора указывает на число операций чтения этого вектора, после которого происходит освобождение ЗУ с динамической адресацией от этого вектора, т.е. адрес вектора записывается в блок 6 магазинной памяти адресов свободных векторов. Количество копий векторов данных записывается в один из двух блоков 4 и 5 памяти. Номер блока памяти, в который записывается количество копий вектора данных, выбирается противоположным задаваемому сигналом Номер банка памяти на группе входов чтения ЗУ с динамической адресацией. Адреса записи вектора данных и его количества копий в блоке 3 и первом и втором блоках 4 и 5 совпадают. Адрес записанного вектора данных, его , длина и номер банка памяти, в котором находится количество копий вектора, ,выдаются на первую группу выходов ЗУ с динамической адресацией.

Чтение вектора данных из ЗУ с динамической адресацией производится следующим образом.

Адрес вектора данных, его длина и количество копий подаются на вторую группу входов ЗУ с динамической адре,- сацией. Аналогично операции записи данных производится поэлементное считывание вектора из блока 3 путем уменьшения значения регистра длины вектора, подключенного к младшим разрядам адреса чтения блока 3. Кроме того производится чтение из указанного банка памяти количества копий вектора данных и сравнение его с нулем.

Если количество копий вектора данных становится равным нулю, то адрес этого вектора записывается в блок 6 магазинной памяти свободных векторов данных. Операции записи и чтения данных из ЗУ с динамической адресацией могут быть совмещены во времени. Режим записи.

Инициация выполнения операции за- писи осуществляется по активному значению первого сопроводительного сигнала. -С приходом тактового импульса происходит запись информации с первой группы входов ЗУ в буферные регистры 69-71, 80 блока 1. Одновременно в буферньй регистр 88 блока 7 буферных регистров записывается значение адреса свободного вектора из блока 6 магазинной памяти. Этот адрес с выхода 54 блока 7 буферных регистров поступает через вход 30 блока 2 управления на мультиплексоры 65 и 66 этого блока и через выходы 38 и 42 - на входы адреса записи блоков 5 и 4. Кроме того, адрес свободного вектора поступает на старшие разряды входа адре- са записи блока 3. Таким образом задается начальный адрес, по которому будет производится запись вектора в ЗУ с динамической адресацией.

Состояние входа номера банка памяти второй группы входов ЗУ с динамической адресацией на этот момент записывается в триггер 83 блока 1 и через выход 23 этого блока поступает на вход 48 блока 7 и на вход 34 блока 2 управления, где управляет работой мультиплексора 60.

На выходе 55 блока 7 буферных ре- г.истров появляется значение входа номера банка памяти второй группы входов ЗУ с динамической адресацией в предшествующий данному момент времени, зафиксированное на триггере 90 блока 7. Это значение поступает на вход 44 блока 2 управления и управляет работой мультиплексоров 65 и 66 этого блока, коммутируя цепи записи первого и второго блоков 4 и 5 памяти количества копий. -Данная коммутация подготавливает к записи в следу- ,ющем такте значения количества копий данных, хранящегося в буферном регистре 80 блока 1 , v один из блоков памяти 4 или 5. В следующем также производитс запись данного из буферного регистра блока 1 в блок 3. На первой группе выходов ЗУ с динамической адресацией

0 о

5

0

0

появляется информация о длине записанного вектора, номере банка памяти и адресе его записи в ЗУ с динамической адресацией и второй сопроводительный сигнал, указывающий на завершение операции записи.

После записи каждого элемента вектора данных значение длины вектора, записанное в буферном регистре блока 1, уменьшается на единицу и анализируется на ноль. Это обеспечивается возможностями самого буферного регистра 70 блока 1 и элементами 67 и 75 этого блока. Равенство нулю содержимого этого регистра вызывает чтение нового адреса свободного вектора из блока 6 магазинной памяти и запись количества копий вектора из буферных регистров блока 1 в блоки 4 или 5 памяти.

Инициация выполнения операции чтения осуществляется по активному значению третьего сопроводительного сигнала. С приходом тактового импульса происходит запись информации с второй группы входов ЗУ с динамической адресацией в буферные регистры 72-74, блока 1. Адрес вектора данных с выхода 26 блока 1 поступает на входы адреса чтения блоков 4 и 5 памяти, а также на старшие разряды входа адреса чтения блока 3.

Количество копий векторных данных, .прочитанное по заданному адресу из первого или второго блока 4 и 5 памяти уменьшается на единицу на сумматорах 58 и 59 блока 2 управления, а затем проверяется на ноль элементами 56 и 57 этого же блока. Мультиплексор 60 блока 2 управления в зависимости от заданного на входе ЗУ с динамической адресацией номера банка памяти выбирает один из выходных сигналов указанных элементов и при наличии третьего сопроводительного сигнала на второй группе входов ЗУ с динамической адресацией подключается к информационному входу D-триггера 62 блока 2 управления.

В следующем также производится запись прочитанного из блока 3 данного в буферный регистр 87 блока 7 буферных регистров. Кроме того, производится запись уменьшенного на единицу количества копий векторных данных в регистры 63 и 64 блока 2 управления с целью последующей перезаписи этого значения в заданный второй

группой входов ЗУ с динамической адресацией банк памяти, т.е. первый или второй блок 4 или 5 памяти. Как указывалось выше, управление работой блоков 4 и 5 памяти осуществляется мультиплексорами 65 и 66 блока 2 управления, которые коммутируют информационные и управляющие цепи этих блоков в зависимости от выбранного для данной операции банка памяти,

Необходимо отметить, что процессы считывания и записи информации происходят независимо друг от друга и поэтому могут быть совмещены во вре- мени. Кроме того, ЗУ с динамической адресацией может работать как с векторами, так и со скалярными данными (длина вектора равна единице). ЗУ с динамической адресацией может быть применено в векторно-потоковых процессорах, машинах с динамической архитектурой и т.п.

формула изобретения

Запоминающее устройство с динамической адресацией, содержащее блок буферизации данных и формирования младших разрядов адреса, блок буфер- ных регистров, блок памяти, первый блок памяти колич.ества копий информации и блок управления, причем первый вход блока управления соединен с выходом первого блока памяти количества копий, информационный вход, вход адреса записи и вход разрешения записи которого соединены соответственно с первым, вторым и третьим выходами блока управления, вход разрешения записи, информационный вход, вход младших разрядов адреса записи блока памяти соединены соответственно с первым, вторым и третьим выходами блока буферизации данных и формирования младших разрядов адреса, выход блока памяти соединен с первым информационным входом блока буферных регистров, четвертый даыход блока буферизации данных и формирования младших разрядов адреса - с вторым входом блока управления, отличающееся тем, что, с целью повышения пропускной способности запоминающего устройства с динамической адресацией за счет обеспечения одновременного осуществления операций записи и чтения информации, в него введены второй блок памяти количества копий ин

jg

Q

5

п 5

5

0

0

формации и блок магазинной памяти, причем информационный вход, вход адреса записи и вход разрешения записи второго блока памяти количества копий информации соединены соответственно с четвертым, пятым и шестым выходами блока управления, третий вход которого подключен к выходу второго блока памяти количества копий информации, а седьмой выход соединен с входом разрешения записи блока магазинной памяти, информационный выход которого соединен с вторым входом блока буферных регистров, а вход разрешения операции чтения блока магазинной памяти - с четвертым входом блока управления и подключен к пятому выходу блока буферизации данных и формирования младших разрядов адреса, соответствующие разряды шестого выхода которого соединены с входами адреса чтения первого и второго блоков памяти количества копий информации и с входом старших разрядов адреса чтения блока памяти, седьмой выход блока буферизации данных и формирования младших разрядов адреса соединен с информационным входом блока магазинной памяти и с пятым входом блока управления, восьмой и девятый выходы блока буферизации данных и формирования младших разрядов адреса - соответственно с шестым и седьмым входами блока управления и третьим и четвертым входами блока буферных регистров, соответствующие разряды шестого выхода блока буферизации данных и формирования младших разрядов адреса подключены к входам младших разрядов адреса чтения блока памяти, первый - четвертый входы блока буферизации данных и формирования младших разрядов адреса образуют вход записи устройства, пятый - восьмой входы блока буферизации данных и формирования младших разрядов адреса образуюгвход чтения устройства, девятый вход блока буферизации данных и формирования младших разрядов адреса, восьмой вход блока управления и стробирующий вход блока буферных регистров подключены к входу тактовых импульсов устройства, десятый выход блока буферизации данных и формирования младших разрядов адреса является первым выходом первой группы выходов устройства, а одиннадцатый выход блока буферизации данных и формирования младших раэрядов адреса является первым выходом второй группы выходов устройства, первый выход блока буферных регистров соединен с девятым входом блока управления и является вторым выходом второй группы выходов устройства, второй выход блока буферных регистров является третьим выходом второй группы выходов устройства, третий выход блока буферных регистров соединен с десятым входом блока управления, вход

старших разрядов записи блока памяти является вторым выходом первой группы выходов устройства, четвертый выход блока буферных регистров соединен с одиннадцатым входом блока управления и является третьим выходом первой группы выходов устройства, первый вход блока буферизации данных и формирования младших разрядов адреса является четвертым выходом первой группы выходов устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1984 |

|

SU1243033A1 |

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1509915A2 |

| Устройство для обмена данными между оперативной памятью и периферийными устройствами | 1985 |

|

SU1260970A2 |

| Устройство для контроля ввода-вывода | 1980 |

|

SU896626A1 |

| Запоминающее устройство | 1985 |

|

SU1339653A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ БУФЕРНОЙ ПАМЯТЬЮ | 1990 |

|

RU2010317C1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1987 |

|

SU1597895A1 |

| Программируемый сопроцессор | 1988 |

|

SU1675880A1 |

| Устройство для сопряжения двух магистралей | 1986 |

|

SU1348874A1 |

| Устройство для контроля блоков памяти | 1988 |

|

SU1569903A1 |

Изобретение относится к области вычислительной технике ,в частности, к запоминающим устройствам, и может быть использовано, например, в процессорах с асинхронным управлением вычислениями для хранения операндов и результатов операций. Изобретение повышает производительность запоминающего устройства с динамической адресацией, содержащего блок 1 буферизации данных и формирования младших разрядов адреса накопителя,блок 2 управления, блок 3 памяти, первый блок 4 памяти количества копий информации, блок 7 буферных регистров, за счет введения второго блока памяти 5 количества копий информации и блока 6 магазинной памяти, что позволяет обеспечить одновременность выполнения операций записи и считывания информации из запоминающего устройства с динамической адресацией. 5 ил.

6062ZVI

Первая группа входов

АН

Первая группа Выходов

ЛВ.СС2

Запоминающее устройство с динамической адресацией

не, А

48, ссз

$

Вторая групп В ход о t

ДМси

Ри,г.5

/

Д,ДВ,КК,СС1

Запись операнда

Чтение операнда

х

Вторая группа.

Выходов

/

| Коуги П.М | |||

| Архитектура конвейерных ЭВМ: Пер | |||

| с англ | |||

| М.: Радио и связь, 1985, с.274 | |||

| Патент США № 4047160, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Дверной замок, автоматически запирающийся на ригель, удерживаемый в крайних своих положениях помощью серии парных, симметрично расположенных цугальт | 1914 |

|

SU1979A1 |

Авторы

Даты

1989-04-15—Публикация

1987-05-21—Подача