5

10

15

Изобретение относится к вычислительной технике и может быть использовано в системах обработки изображений для решения задач распределения элементов изображения по диапазонам яркости-, а также в различных информационно-логических системах.

Цель изобретения - повьшение быстродействия устройства.

На чертеже изображена структурная схема запоминающего устройства.

Устройство содержит первый счетчик 1, коммутатор 2 адреса, первый блок 3 памятир регистр 4 числа, второй счетчик 5, третий счетчик 6-, второй блок 7 памяти и регистр 8 сдвига.

Работа устройства в режиме подсчета чисел основана на простой аналитической зависимости ной числа и номером ячейки, соответствующей данному диапазону значений числа. В блоке 7 хранится обрабаты- ваемьй массив чисел, максимальное из которых может иметь значение , 25 где к l,2j..,f п (разрядность блока 7). При этом обработка (подсчет значений) может вестись по 2 диапазонам, где , 1,2,.,.5 к. При

ячейке блока 7 с данным адресом. Считанное число, в свою очередь, поступает на вход регистра 8, на выходе которого вырабатывается код, представляющий собой значение числа, сдвинутое на к -т разрядов (сдвиг производится в сторону младших разрядов). Этот код является адресом ячейки соответствующего диапазона в блоке 3 и через коммутатор 2 поступает на его вход. Производится считывание в регистр 4 кода, представляющего собой текущее значение количества анализируемых чисел, попадающих в данный диапазон. Код с регистра 4 поступает на счетчик 5. где производится увеличение его на единицу, и Увеличенный код записывается обратмежду величи- 70 но в блок 3 по тому же адресу, Содержимое счетчика 6 увеличивается на единицу, и производится обработка следующего чисша из исходного массива, хранящегося в блоке 7. Эта последовательность действий повторяется для каждого исходного числа, и таким образом производится подсчет количества чисел исходного массива по диапазонам их значений, 30 Устройство может работать и в режиме обычного запоминающего устройства (ЗУ). Для этого комментатор 2 переключается в режим передачи на первый вход блока 3 информации с выхода счетчика 1. При этом устройство

m к производится подсчет количества чисел, равных каждому из 2 -1

значений, т,е„ диапазон сводится к какому-то одному конкретному з наченню числа, а количество диапазонов - к количеству всех возможных значений обрабатьшаемого массива чисел.

Перед работой устройства должен быть задан параметр т,. определяющий количество и длину диапазонов, обрабатываемый массив должен находиться в блоке 7, а блок 3 должен быть

подготовлен для подсчета . Для этого счетчики 1 и 5 устанавливаются в нуль. Производится запись содержимого счетчика 5 в ячейку блока 3, адрес которой определяется содержимым счетчика 1, Затем содержимое счетчика 1 увеличивается на единицу и производится следующий циют записи в блок 3. Эта последовательность действий повторяется для всех адресов блока 3. Таким образом, во все ячейки блока 3 заносятся нулевые значения после чего устройство готово к обработке массива чисел, хранядгегО- ся в блоке 7,

На вход блока 7 поступает значение адреса с счетчика 6 и производится считывание числа, хранящегося в

ва, хранящегося в блоке 7. Эта последовательность действий повторяется для каждого исходного числа, и таким образом производится подсчет количества чисел исходного массива по диапазонам их значений, Устройство может работать и в режиме обычного запоминающего устройства (ЗУ). Для этого комментатор 2 переключается в режим передачи на первый вход блока 3 информации с выхода счетчика 1. При этом устройство

1

представляет собой два отдельных ЗУ, информация из которых считывается в регистры 8 и 4 соответственно. Кроме того, устройство может работать и в режиме ЗУ с таблицей косвенной адресации на выходе„ При этом блок 7 представляет собой основную память хранения информации, которая при считывании через регистр

8 и коммутатор 2 поступает на вход блока 3, якпяющегося вспомогательной памятью, выполняющей функции хра- не1ШЯ таблицы косвенной адресации, и адресом, по которому из блока 3 в

регистр 4 считывается результат. Таким образом,.устройство осуществляет хранение и табличное преобразование информации.

Управление данным устройством в

описанном порядке может осуществлять как, автомат с жесткой логикой), так И универсальная ЭВМ по заданной программе, Сигнсшы управления поступают от внешнего блока управления ко

в-сем блокам запоминающего устройства. Результат или выходные данные могут считаны согласно алгоритму обработки из блока 3 с помощью того же внешнего блока управления.

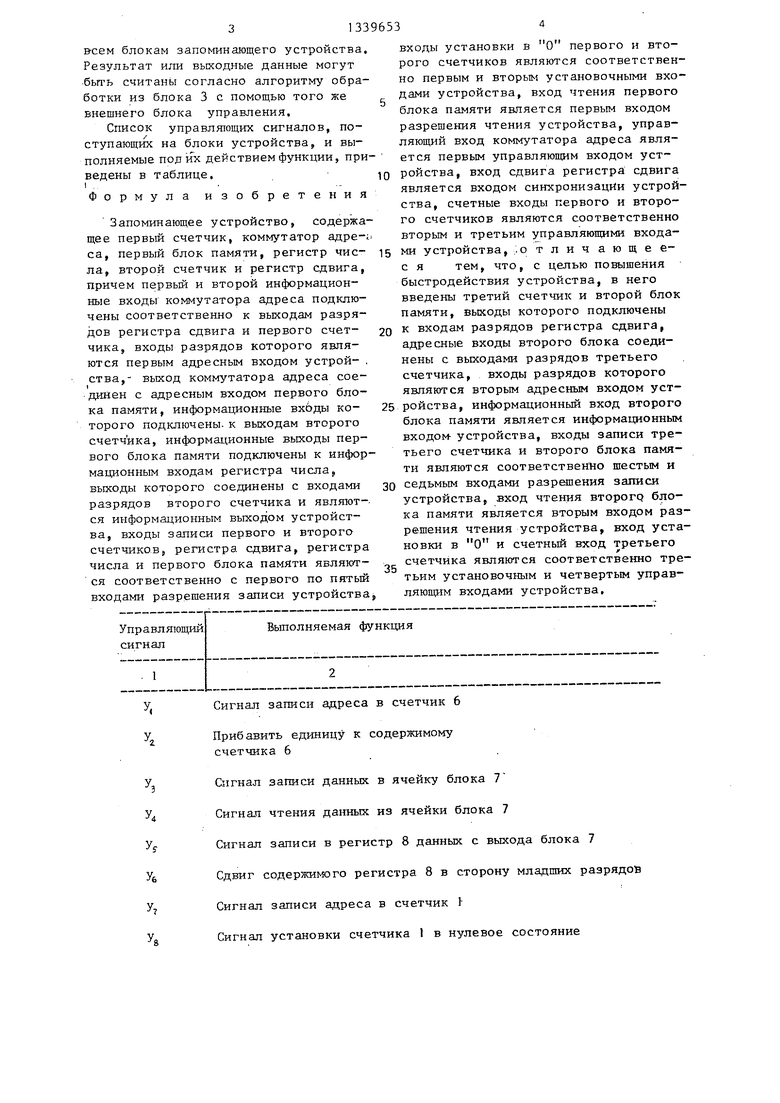

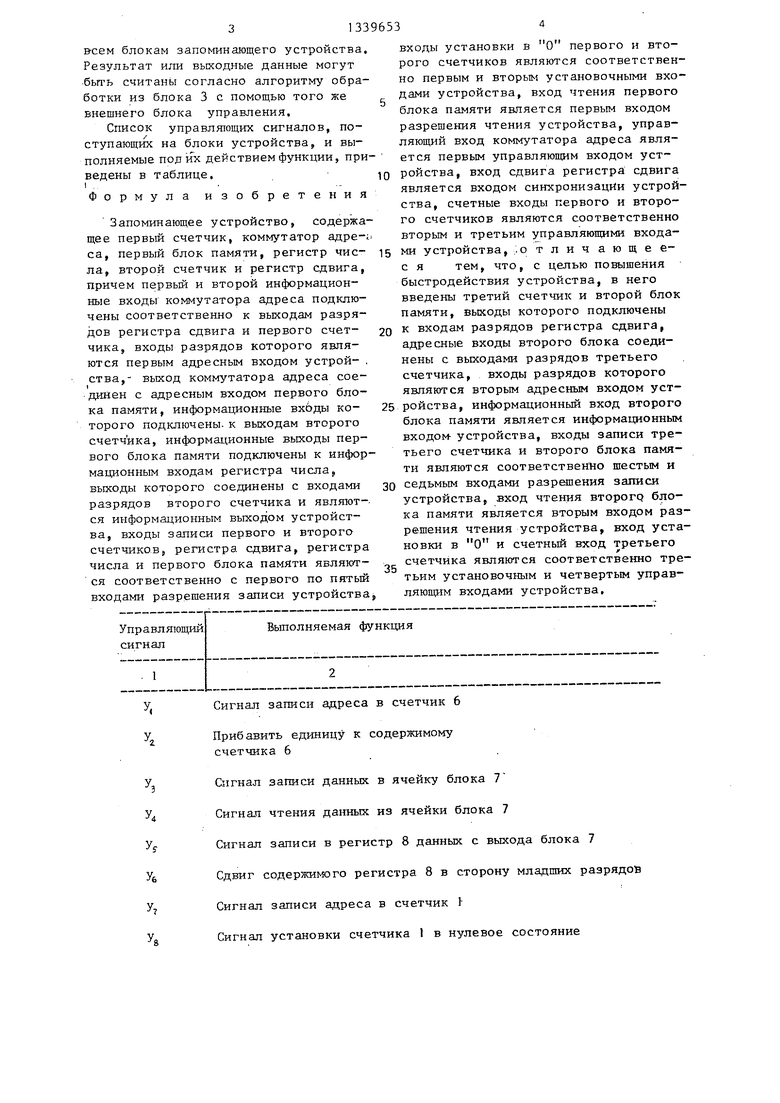

Список управляющих сигналов, поступающих на блоки устройства, и выполняемые под их действием функции, при- ведены в таблице,

Формула изобретения

Запоминающее устройство, содержащее первый счетчик, коммутатор ядре-;.

20

са, первый блок памяти, регистр чис- 15 ми устройства, ,,о т л и ч а ю щ е ес я тем, что, с целью повышения быстродействия устройства, в него введены третий счетчик и второй блок памяти, выходы которого подключены к входам разрядов регистра сдвига, адресные входы второго блока соединены с выходами разрядов третьего счетчика, входы разрядов которого являются вторым адресным входом уст- 25 ройства, информационный вход второго блока памяти является информационным входом- устройства, входы записи третьего счетчика и второго блока памяти являются соответственно шестым и седьмым входами разрешения записи устройства, вход чтения второгр блока памяти является вторым входом разрешения чтения устройства, вход установки в О и счетный вход третьего счетчика являются соответственно третьим установочным и четвертым управ- входами устройства.

ла, второй счетчик и регистр сдвига, причем первьш и второй информационные входы коммутатора адреса подключены соответственно к выходам разрядов регистра сдвига и первого счетчика, входы разрядов которого являются первым адресным входом устрой- . ства,- выход коммутатора адреса соединен с адресным входом первого блока памяти, информационные вхбды которого подключены- к выходам второго счетчика, информационные выходы первого блока памяти подключены к информационным входам регистра числа, выходы которого соединены с входами разрядов второго счетчика и являют-- ся информационным выходом устройства, входы записи первого и второго счетчиков регистра сдвига, регистра числа и первого блока памяти являются соответственно с первого по пятый входами разрешения записи устройстваj

30

35

У

Сигнал записи адреса в счетчик 6

Прибавить единицу к содержимому счетчика 6

Сигнал записи данных в ячейку блока 7

Сигнал чтения данных из ячейки блока 7

Сигнал записи в регистр 8 данных с выхода блока 7

Сдвиг содержимого регистра 8 в сторону младших разрядов

Сигнал записи адреса в счетчик h

Сигнал установки счетчика 1 в нулевое состояние

653

10

4 О

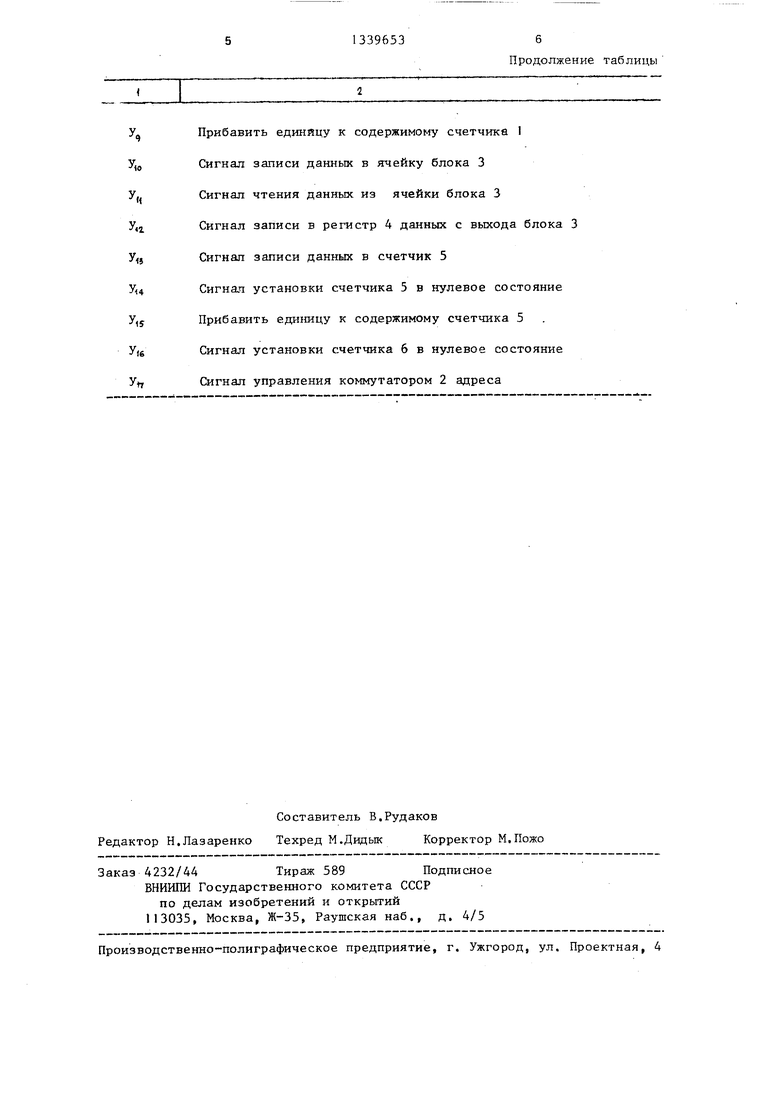

входы установки в и первого и второго счетчиков являются соответственно первым и вторым установочными входами устройства, вход чтения первого блока памяти является первым входом разрешения чтения устройства, управляющий вход коммутатора адреса является первым управляющим входом устройства, вход сдвига регистра сдвига является входом синхронизации устройства, счетные входы первого и второго счетчиков являются соответственно вторым и третьим управляющими входаПрибавить единицу к содержимому счетчика 1

Сигнал записи данных в ячейку блока 3

Сигнал чтения данных из ячейки блока 3

Сигнал записи в регистр 4 данных с выхода блока 3

Сигнал записи данных в счетчик 5

Сигнал установки счетчика 5 в нулевое состояние

Прибавить к содержимому счетчика 5

Сигнал установки счетчика 6 в нулевое состояние

Сигнал управления коммутатором 2 адреса

Продолжение таблицы

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1987 |

|

SU1531160A1 |

| Запоминающее устройство | 1981 |

|

SU970463A1 |

| Запоминающее устройство | 1980 |

|

SU942141A2 |

| Устройство для контроля программ | 1983 |

|

SU1136172A1 |

| Устройство для умножения с накоплением комплексных чисел | 1988 |

|

SU1587230A1 |

| Устройство для сортировки информации | 1986 |

|

SU1365075A1 |

| Устройство для сопряжения ЦВМ с внешним устройством | 1989 |

|

SU1661779A1 |

| Устройство для контроля логических блоков | 1986 |

|

SU1386998A1 |

| Запоминающее устройство | 1987 |

|

SU1520592A1 |

| Устройство для сортировки чисел | 1990 |

|

SU1835543A1 |

Изобретение относится к вычислительной технике и может быть использовано в системах обработки изображений для решения задач распределения элементов изображения по диапазонам яркости, а также в различных информационно-логических системах. Цель изобретения - повьшение быстродействия устройства. Запоминающее устройство содерясит первый счетчик 1, коммутатор 2.адреса, первый блок 3 памяти, регистр 4 числа, второй счетчик 5, третий счетчик 6, второй блок 7 памяти, регистр 8 сдвига. Повышение быстродействия устройства достигается за счет того, что в блоке 3 памяти хранятся результаты обработки данных, а в блоке 7 памяти - исходные дачные. 1 ил., 1 табл. с € (Л 00 00 со ot СП со

| Запоминающее устройство | 1977 |

|

SU691925A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Запоминающее устройство | 1981 |

|

SU970463A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-09-23—Публикация

1985-12-17—Подача