1

Изобретение относится к вычислительной технике и может быть использовано в устройствах со встроенными средствами тестирования.

Целью изобретения является расширение функциональных возможностей регистра за счет выполнения функций генератора псевдослучайных чисел.

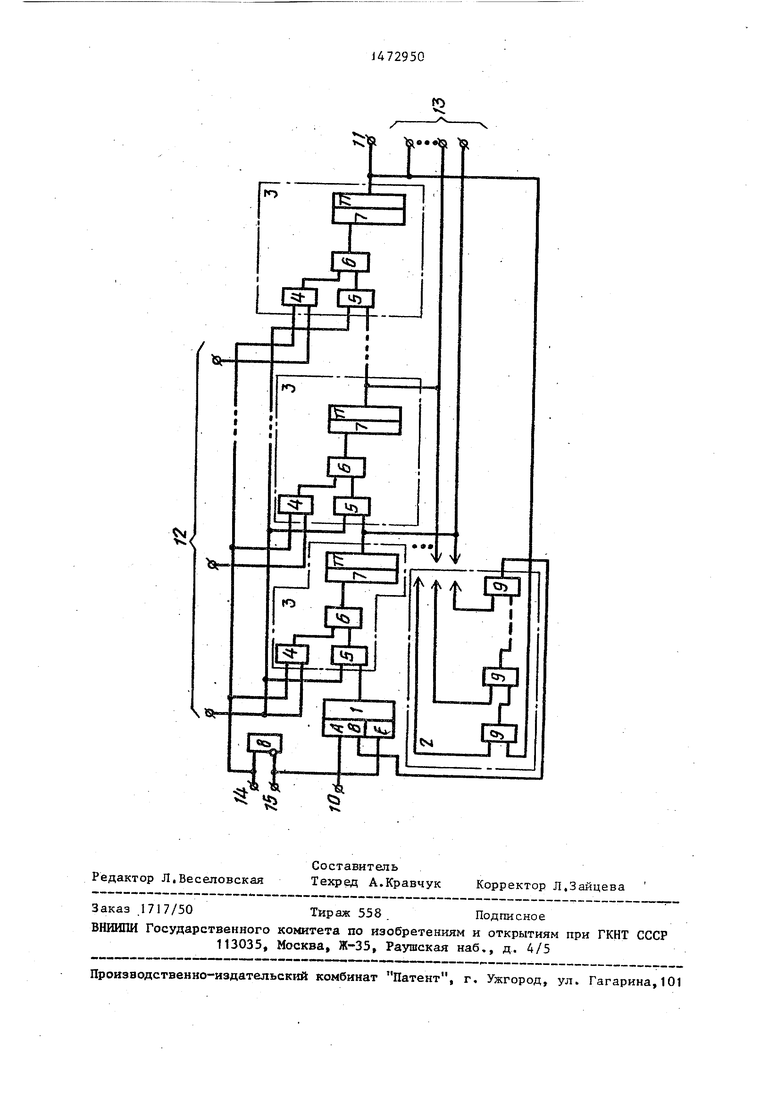

На чертеже приведена схема регистра.

Регистр содержит мультиплексор 1, блок 2 обратной связи, разряды 3 регистра, каждый из которых содержит первый блок 4 и второй 5 элементы И, элемент ИСКЛЮЧАЮЩИЕ ИЛИ 6, двухступенчатый D-триггер 7, элемент 8 ИМПЛИКАЦИЯ, Блок обратной связи содержит по крайней мере один элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 9. На чертеже показаны также последовательные информационные вход 10 и выход 11 регитра, параллельные информационные выходы

(/

12 и выходы 13, первый 14 и второй 15 управляющие входы регистра (тактовый вход регистра на чертеже не показан),

. Регистр работает следующим образом,

При подаче на первый 14 и второй 15 управляющие входы сигналов логического нуля на выходе элемента ИМПЛИКАЦИЯ 8 вырабатывается сигнал логической единицы. При этом информация через мультиплексор 1 с входа 10 регистра подается через элементы 5 и ИСКЛЮЧАЮЩЕЕ ИЛИ 6 каждого разряда 3 регистра на входы триггеров 7 регистра. Таким образом, многофункциональный регистр работает как регистр сдвига, причем информация с выхода триггера 7 последнего разряда 3 регистра поступает на выход 11, В этом же режиме можно устанавливать триггеры 7, подавая вектор состояний в

4

s|

1C

CD

сл

последовательном коде на вход 10 ре-/ гистра и выводить информацию в поседовательном коде через выход П.

При подаче на первый управляющий вход 14 сигнала логической единицы, а на второй 15 сигнала логического нуля на выходе элемента ИМПЛИКАЦИЯ устанавливается сигнал логического нуля и на входы триггеров 7 всех раз-JQ рядов 3 через элементы 4 и 6 подаются только сигналы с соответствующих информационных входов 12 регистра, Та-1 ким образом, многофункциональный регистр распадается на отдельные15 три г-геры,

При -подаче на первый управляющий г вход 14 сигнала логического нуля, а на второй управляющий вход 15 сигна- ла логической единицы на выходе эле- 20 мента 8 вырабатывается сигнал логи--1 ческой единицы и на входы триггеров 7 всех разрядов 3 регистра, кроме первого, через элементы 5 и б подается информация с предыдущих разрядов 25 регистра, а на вход триггера 7 первого разряда через мультиплексор 1 и элементы 5 и 6 - информация с выхода блока обратной связи 2. Таким образом, многофункциональный регистр30 преобразуется в генератор псевдослучайных последовательностей, которые могут использоваться в качестве тестовых векторов для цифровых схем,

При подаче на управляющие входы с 14 и 15 сигналов логической единицы на выходе элемента 8 формируется сигнал логической единицы и на входы триггеров 7 всех разрядов 3 регистра через элемент 6 подаются суммирован- 40 ные по модулю два сигналы с соответствующих информационных входов 10 устройства (через элемент 4, 6) и сигналы с выходов триггеров 7 предыдущих разрядов 3 (через элементы 5) , а для первого разряда сигналы из блока обратной связи 2 (через мультиплексор 1 и элемент 5),

Таким образом, тестирующий регистр -п преобразуется в параллельный сигнатурный анализатор, предназначенный для анализа и свертки информации с тестируемой схемы 4

Формула изобретения Многофункциональный регистр, со- держащий мультиплексор, блок обратной связи, состоящий из элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, и в каждом разряде - первый и второй элементы И, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и D-триггер, выход которого является соответствующим параллельным информационным выходом регистра, С-вход - тактовым входом регистра, а D-вход соединен с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, входы которого соединены с выходами первого и второго элемента И, первый вход первого элемента И является соответствующим параллельным информационным входом регистра, а второй вход - первым управляющим входом регистра, первый вход второго элемента И каждого разряда, кроме первого, соединен с выходом D-триггера предыдущего разряда, а первый вход второго элемента И первого разряда соединен с выходом мультиплексора, в блоке обратной связи первые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, кроме первого, соединены с выходами предыдущих элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, перцый вход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с выходом D-триггера последнего разряда регистра, а вторые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены с выходами D-триггеров других разрядов, выход последнего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с первым информационным входом мультиплексора, второй информационный вход которого является последовательным информационным входом регистра,.о т - л. и чающийся тем, что, с целью расширения функциональных возможностей регистра за счет выполнения функции генератора псевдослучайных чисел, в регистр введен элемент ИМПЛИКАЦИЯ, прямой вход которого соединен с вторым входом первого элемента И первого разряда регистра, выход с вторыми входами вторых элементов И каждого разряда регистра, а ин- .версный вход соединен с управляющим входом мультиплексора и является вторым управляющим входом регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор псевдослучайных чисел | 1990 |

|

SU1805465A1 |

| Генератор случайных чисел | 1990 |

|

SU1817094A1 |

| Устройство для контроля логических блоков | 1988 |

|

SU1553980A1 |

| Устройство для встроенного контроля цифровых блоков | 1986 |

|

SU1397920A1 |

| Устройство для встроенного тестового контроля | 1984 |

|

SU1196877A1 |

| КОРРЕЛЯЦИОННОЕ УСТРОЙСТВО | 2013 |

|

RU2536393C1 |

| Многофункциональный модуль для устройств встроенного контроля | 1989 |

|

SU1619275A1 |

| Регистр | 1987 |

|

SU1425785A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1260961A1 |

| Генератор псевдослучайных последовательностей | 1983 |

|

SU1127079A1 |

Изобретение относится к вычислительной технике и может быть использовано в устройствах со встречными средствами тестирования. Целью изобретения является расширение функциональных возможностей регистра за счет выполнения функций генератора псевдослучайных чисел. Для достижения этой цели управление регистром выполняется с помощью элемента импликация. 1 ил.

| Тице У,, Шенк К | |||

| Полупроводниковая схемотехника | |||

| Справочное руководство, М.: Мир, 1983, с.512 | |||

| Konemann В., Mucha I,, Zwiechoff G | |||

| Build - in Logic Block Observation Techniques, 1979, IEEE Test Conference, IEEE pub | |||

| Инерционно-аккумуляторное приспособление для автоматического открывания и закрывания поршневого затвора | 1912 |

|

SU509A1 |

| Пишущая машина | 1922 |

|

SU37A1 |

Авторы

Даты

1989-04-15—Публикация

1987-03-30—Подача