Изобретение относится к вычисли- .тельной технике и технике связи и мо- жет быть использовано в аппаратуре передачи дискретной информации.

Цель изобретения - повышение скорости передачи многопозиционных сигналов. (МПС) при заданной помехоустойчивости.

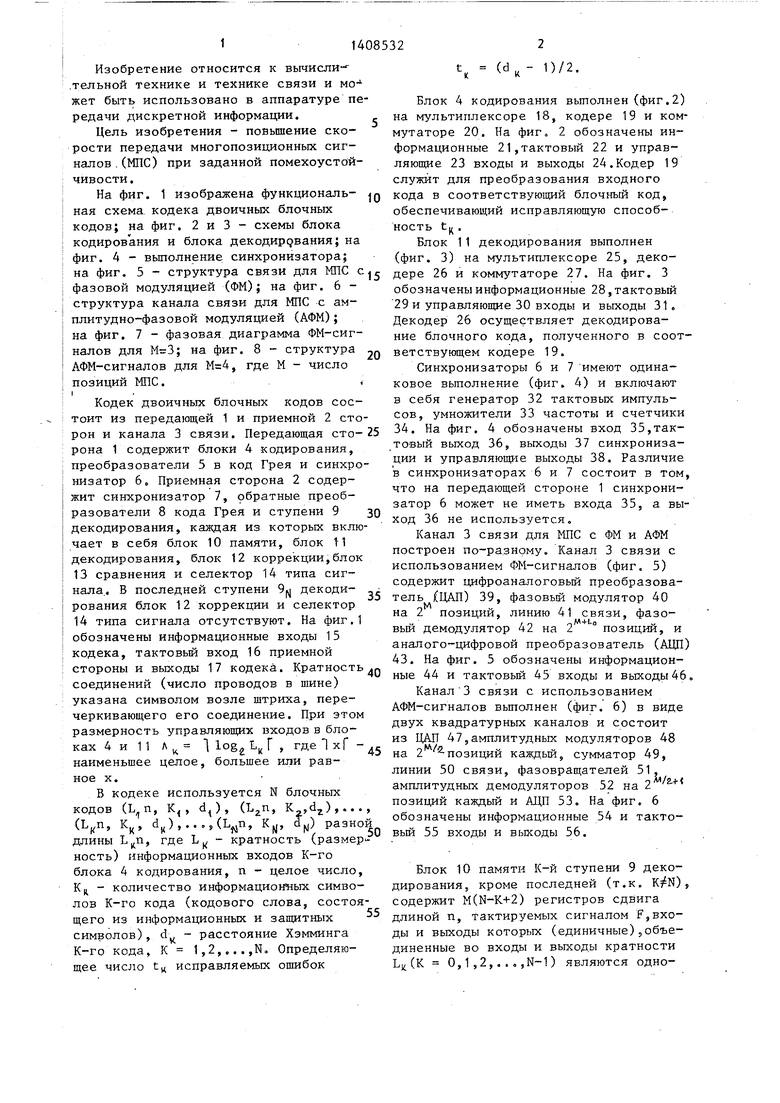

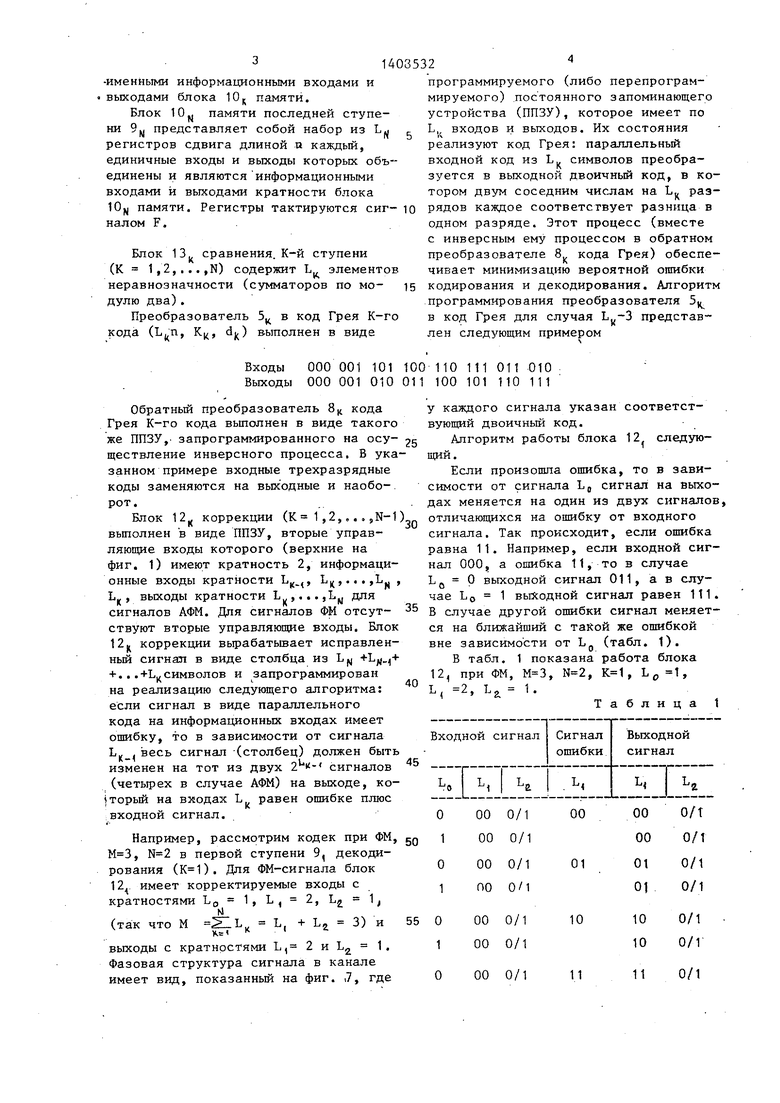

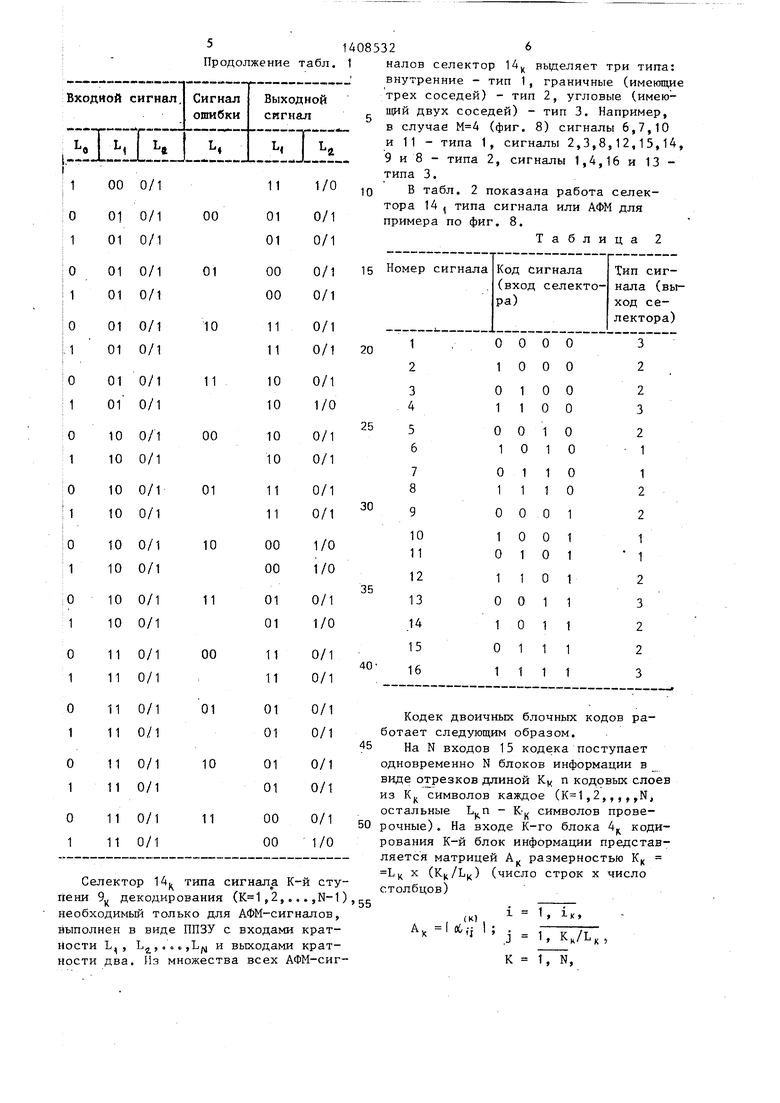

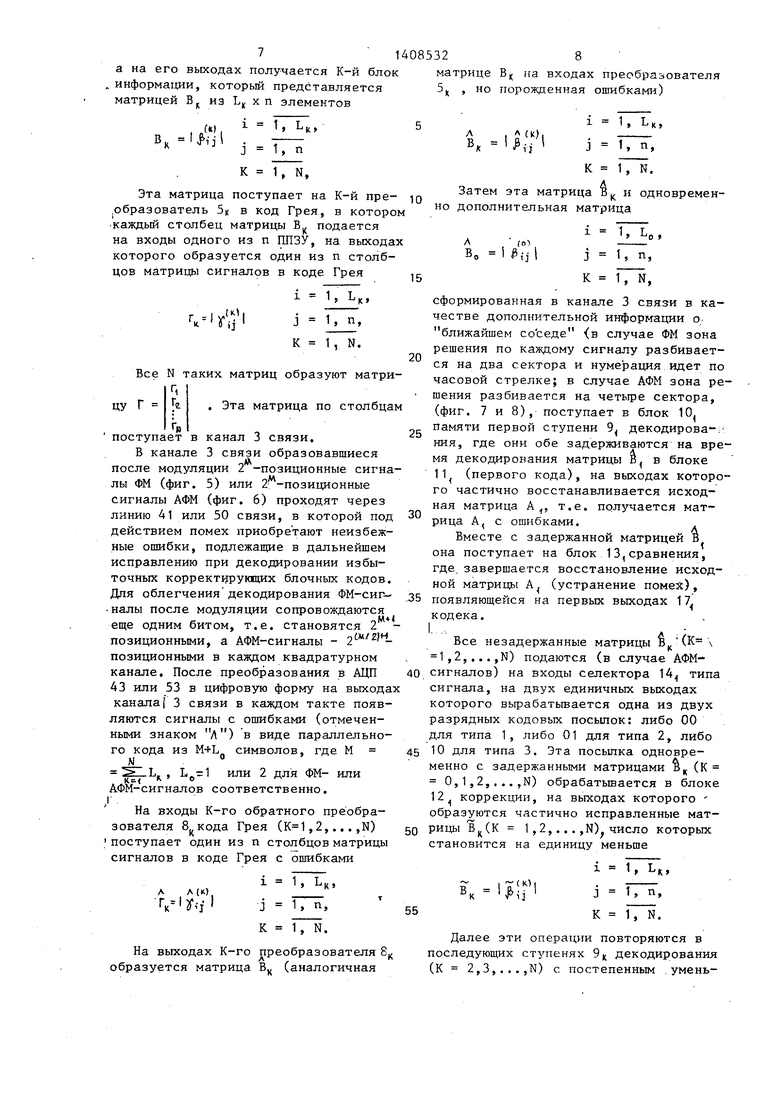

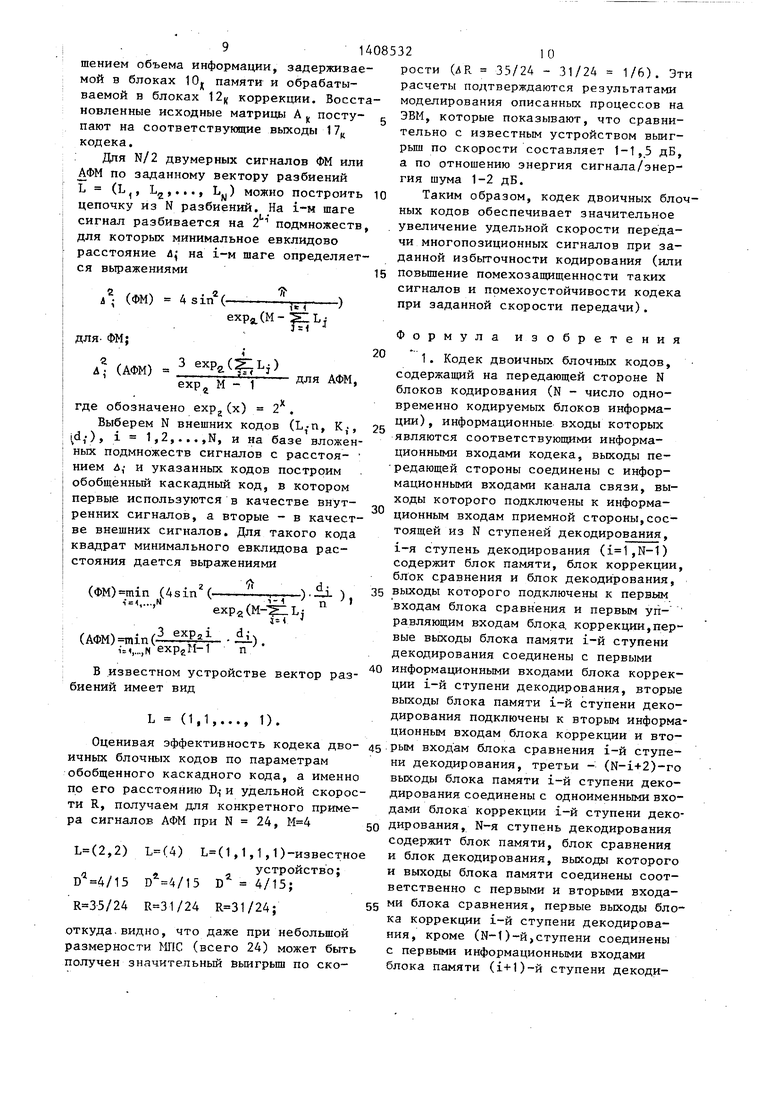

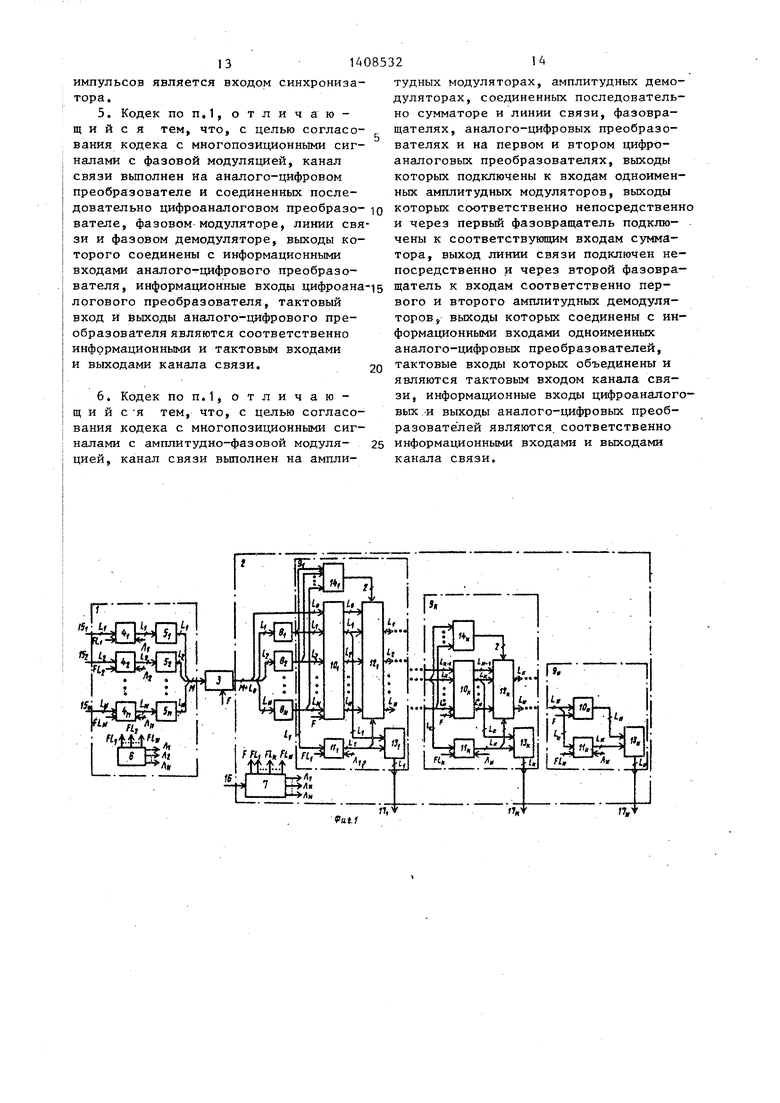

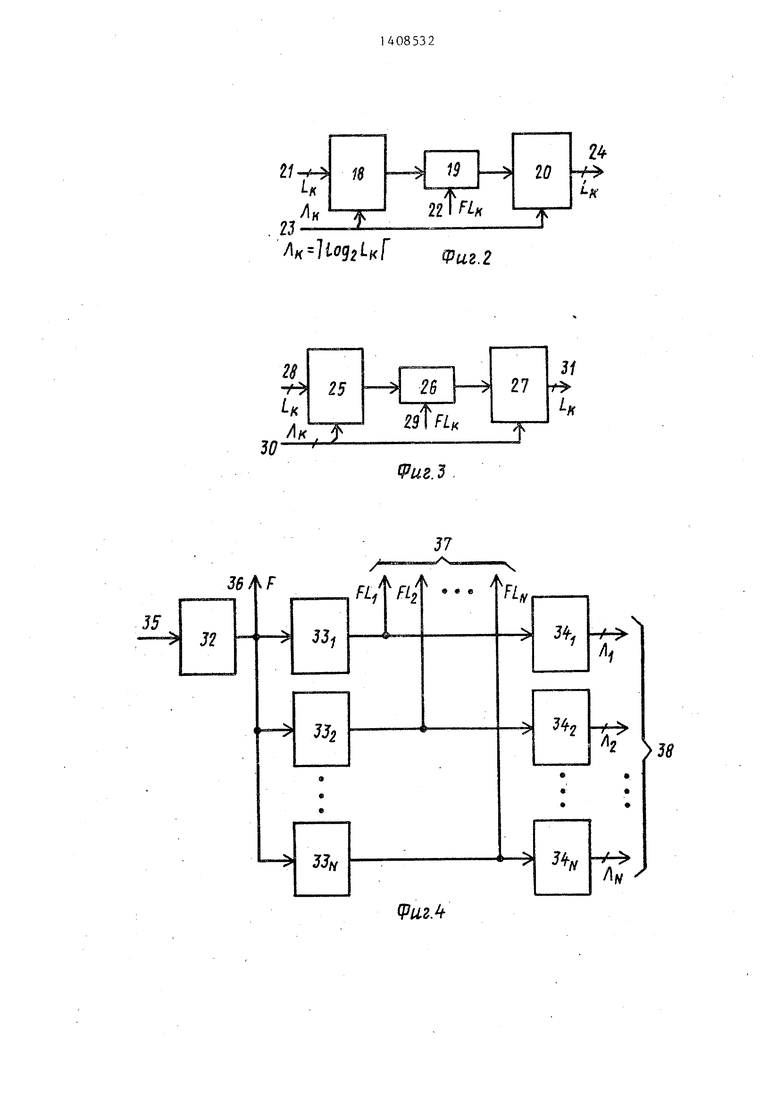

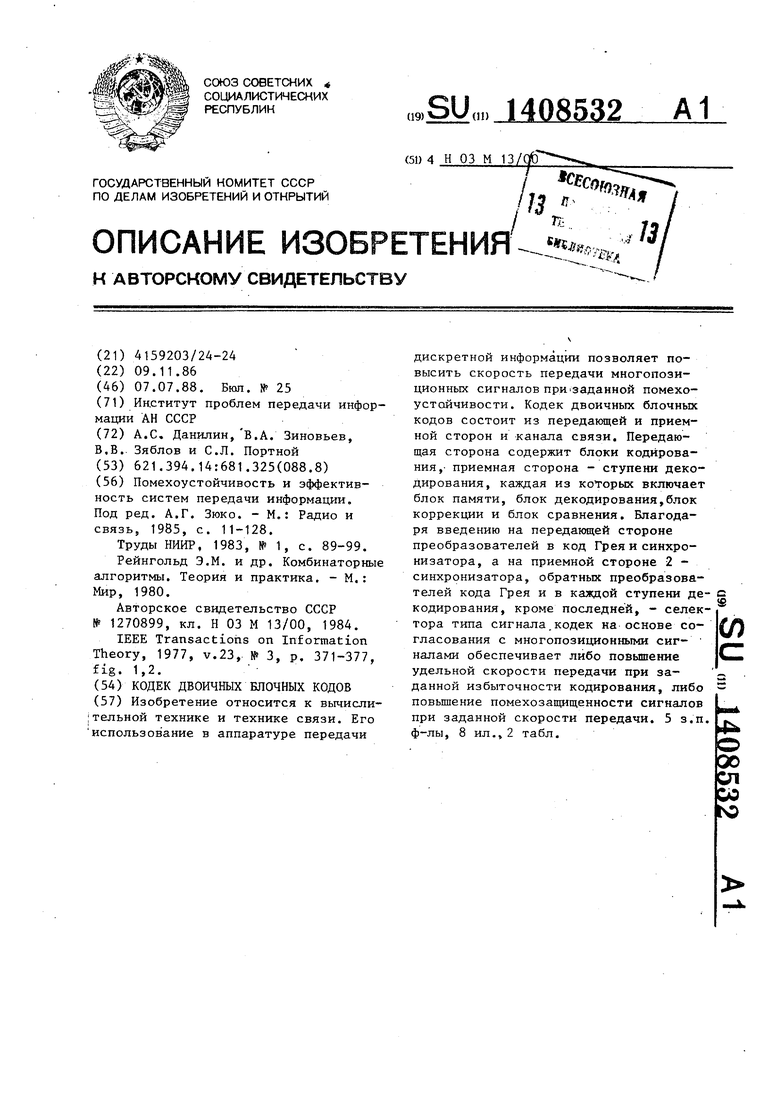

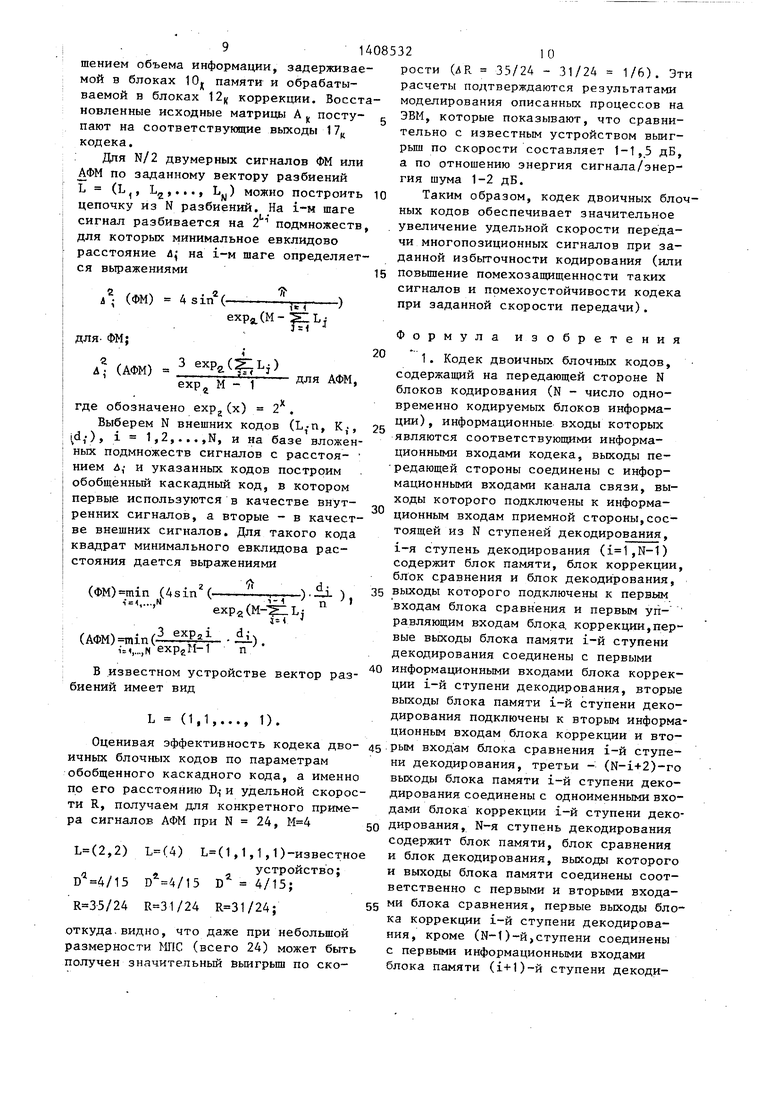

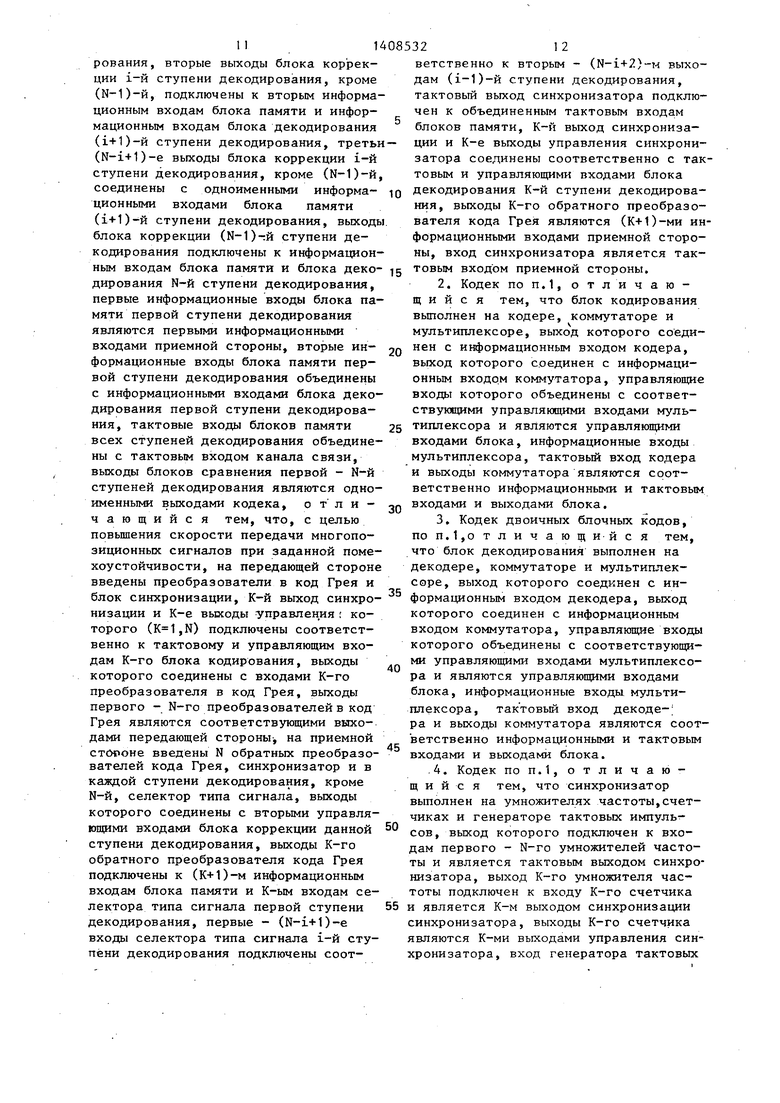

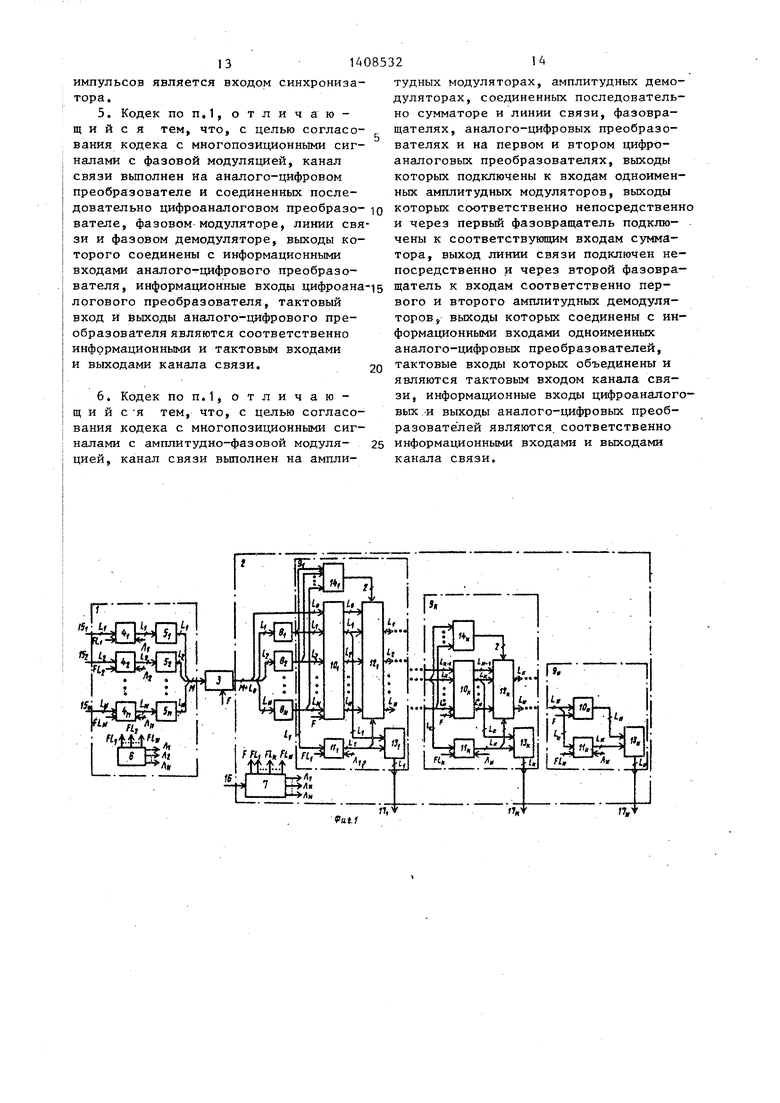

На фиг. 1 изображена функциональ- Q ная схема кодека двоичных блочных кодов; на фиг. 2 и 3 - схемы блока кодирования и блока декодирования; на фиг. 4 - выполнение синхронизатора; на фиг. 5 - структура связи для МПС фазовой модуляцией (ФМ); на фиг. 6 - структура канала связи для МПС с амплитудно-фазовой модуляцией (АФМ); на фиг. 7 - фазовая диаграмма ФМ-сиг- налов для на фиг. 8 - структура JQ ЛФМ-сигналов для , где М - число

позиций МПС.i

I

Кодек двоичных блочных кодов состоит из передающей 1 и приемной 2 сторон и канала 3 связи. Передающая сто-25 рона 1 содержит блоки 4 кодирования, преобразователи 5 в код Грея и синхронизатор 6. Приемная сторона 2 содержит синхронизатор 7, обратные преобразователи 8 кода Грея и ступени 9 ЗО декодирования, каждая из которых включает в себя блок 10 памяти, блок II декодирования, блок 12 коррекции,блок

13сравнения и селектор 14 типа си.г- нала, В последней ступени декоди- .. рования блок 12 коррекции и селектор

14типа сигнала отсутствуют. На фиг.1 обозначены информационные входы 15 кодека, тактовьй вход 16 приемной стороны и выходы 17 кодека. Кратность .Q соединений (число проводов в щине) указана символом возле штриха, перечеркивающего его соединение. При этом размерность управляющих входов в блоках 4 и 1 1 Л j 1 log L Г , где 1 хГ - j наименьшее целое, большее или равное X.

В кодеке используется N блочных кодов (Цп, К,, d,), (, К ,dj,),..., (, К, d|),.. ,,(, KU, d|) разной длины где Lj - кратность (размерность) информационных входов К-го блока 4 кодирования, п - целое число, Кц - количество информационных символов К-го кода (кодового слова, состоящего из информационных и зашзитных - символов), d расстояние Хэмминга К-го кода, К 1,2,...,N, Определяющее число t исправляемых ошибок

(d,- 1)/2.

Блок 4 кодирования вьтолнен (фиг.2) на мультиплексоре 18, кодере 19 и коммутаторе 20. На фиг, 2 обозначены информационные 21,тактовый 22 и управляющие 23 входы и выходы 24.Кодер 19 служит для преобразования входного кода в соответствующий блочный код, обеспечивающий исправляющую способность t .

Блок 11 декодирования выполнен (фиг. 3) на мультиплексоре 25, декодере 26 и коммутаторе 27. На фиг. 3 обозначены информационные 28,тактовый 29 и управляюш 1е 30 входы и выходы 31. Декодер 26 осуществляет декодирование блочного кода, полученного в соответствующем кодере 19.

Синхронизаторы 6 и 7 имеют одинаковое выполнение (фиг. 4) и включают в себя генератор 32 тактовых импульсов, умножители 33 частоты и счетчики 34. На фиг. 4 обозначены вход 35,тактовый выход 36, выходы 37 синхронизации и управляюш -1е выходы 38. Различие в синхронизаторах 6 и 7 состоит в том что на передающей стороне 1 синхронизатор 6 может не иметь входа 35, а выход 36 не используется.

Канал 3 связи для МПС с ФМ и АФМ построен по-разному. Канал 3 связи с использованием ФМ-сигналов (фиг. 5) содержит цифроаналоговый преобразователь ЦАП) 39, фазовьй модулятор 40 на 2 позиций, линию 41 связи, фазовый демодулятор 42 на позиций, и аналого-цифровой преобразователь (АЦП 43. На фиг. 5 обозначены информационные 44 и тактовьй 45 входы и выходы 46

Канал 3 связи с использованием АФМ-сигналов выполнен (фиг. 6) в виде двух квадратурньк каналов и состоит из ЦАП 47,амплитудных модуляторов 48 на 2 позиций каждый, сумматор 49, линии 50 связи, фазовращателей 51 амплитудных демодуляторов 52 на 2 позиций каждьй и АДП 53. На фиг. 6 обозначены информационные 54 и такто- вьй 55 входы и выходы 56.

.

Блок 10 памяти К-й ступени 9 декодирования, кроме последней (т.к. ), содержит M(N-K+2) регистров сдвига длиной п. Тактируемых сигналом F,входы и выходы которых (единичные)5объединенные во входы и выходы кратности Lji (К 0,1 ,2,. . , ,N-1) являются одно-именными информационными входами и выходами блока 10ц памяти.

Блок 10| памяти последней ступени 9 представляет собой набор из L регистров сдвига длиной и каждый, единичные входы и выходы которых объединены и являются информационными входами и выходами кратности блока

10 памяти. Регистры тактируются сиг- ю рядов каждое соответствует разница в налом F. .

Блок 13| сравнения. К-й ступени (К 1,2,,..,N) содержит L элементов неравнозначности (сумматоров по мо- ig дулю два).

Преобразователь 5 в код Грея К-го кода (L.n, К,., d,,)

к выполнен в виде

одном разряде. Этот процесс (вместе с инверсным ему процессом в обратном преобразователе 8| кода Грея) обеспе чивает минимизацию вероятной опмбки кодирования и декодирования. Алгоритм программирования преобразователя 5) в код Грея для случая представлен следующим примером

программируемого (либо перепрограммируемого) постоянного запоминающего устройства (ППЗУ), которое имеет по L, входов и выходов. Их состояния реализуют код Грея: параллельный входной код из L| символов преобразуется в выходной двоичный код, в котором двум соседним числам на L,. раэрядов каждое соответствует разница в

рядов каждое соответствует разница в

одном разряде. Этот процесс (вместе с инверсным ему процессом в обратном преобразователе 8| кода Грея) обеспечивает минимизацию вероятной опмбки кодирования и декодирования. Алгоритм программирования преобразователя 5) в код Грея для случая представлен следующим примером

| название | год | авторы | номер документа |

|---|---|---|---|

| Кодек блочных кодов | 1986 |

|

SU1401613A1 |

| Устройство для декодирования двоичных блочных кодов, согласованных с многопозиционными сигналами | 1987 |

|

SU1587644A1 |

| Устройство для декодирования блочных кодов, согласованных с многопозиционными сигналами | 1987 |

|

SU1543552A1 |

| Кодек блочных кодов | 1984 |

|

SU1270899A1 |

| Кодек самоортогонального квазициклического кода | 1986 |

|

SU1376247A1 |

| Кодек блочной сигнально-кодовой конструкции | 1989 |

|

SU1711337A1 |

| Кодек на основе кода Рида - Маллера первого порядка | 1990 |

|

SU1777243A1 |

| Канальный кодек | 1990 |

|

SU1798922A1 |

| Кодек блочных кодов | 1988 |

|

SU1640829A1 |

| Кодек для системы связи с многократной фазовой модуляцией | 1987 |

|

SU1629992A1 |

Изобретение относится к вычисли- Iтельной технике и технике связи. Его использование в аппаратуре передачи дискретной информации позволяет повысить скорость передачи многопозиционных сигналов при заданной помехоустойчивости. Кодек двоичных блочных кодов состоит из передающей и приемной сторон и канала связи. Передающая сторона содержит блоки кодирования,- приемная сторона - ступени декодирования, каждая из которых включает блок памяти, блок декодирования,блок коррекции и блок сравнения. Благодаря введению на передающей стороне преобразователей в код Грея и синхронизатора, а на приемной стороне 2 - синхронизатора, обратных преобразователей кода Грея и в каждой ступени декодирования, кроме последней, - селектора типа сигнала.кодек на основе согласования с многопозиционными сиг- налами обеспечивает либо повышение удельной скорости передачи при заданной избыточности кодирования, либо повышение помехозащищенности сигналов при заданной скорости передачи. 5 з.п. ф-лы, 8 ил,,2 табл. СП i

Входы 000 001 101 100 110 111 011 010 Выходы 000 001 010 011 100 101 110 111

Обратный преобразователь 8ц кода Грея К-го кода выполнен в виде такого же ППЗУ,- запрограммированного на осу- 25 ществление инверсного процесса, В указанном примере входные трехразрядные коды заменяются на выходные и наобо-. рот.

Блок 12| коррекции (К 1 ,2,,.. ,N-1) выполнен в виде ППЗУ, вторые управляющие входы которого (верхние на фиг. 1) имеют кратность 2, информационные входы кратности L

к-

,

LU, выходы кратности L ,...,Ly для сигналов АФМ. Для сигналов ФИ отсут- ствуют вторые управляющие входы. Блок 12ц коррекции вьфабатьшает исправленный сигнал в виде столбца из -bLjii, + ...+L символов

и запрограммирован на реализацию следующего алгоритма: если сигнал в виде параллельного кода на информационных входах имеет ошибку, то в зависимости от сигнала L.. . весь сигнал -(столбец) должен быть

I

изменен на тот из двух 2 сигналов (четырех в случае АФМ) на выходе, ко- |торый на входах L равен ошибке плюс входной сигнал.

Например, рассмотрим кодек при ФМ, , в первой ступени 9, декодирования (). Для ФМ-сигнала блок 12 имеет корректируемые входы с кратностями LQ 1, L . 2, L

ь

(так что М L L + L 3) и

М

выходы с кратностями L, 2 и L 1. Фазовая структура сигнала в канале имеет вид, показанный на фиг. 7, где

5

5

0

у каждого сигнала указан соответствующий двоичный код.

Алгоритм работы блока 12 следующий.

Если произошла ошибка, то в зависимости от сигнала L сигнал на выходах меняется на один из двух сигналов, отличающихся на ошибку от входного сигнала. Так происходит, если ошибка равна 11. Например, если входной сигнал 000, а ошибка 11, то в случае LQ О выходной сигнал 011, а в случае LO 1 вьйодной сигнал равен 111. В случае другой ошибки сигнал меняется на ближайший с такой же ошибкой вне зависимости от Lg (табл. 1).

В табл. 1 показана работа блока 12 при ФМ, , , , ,

-t-i| ji-iO

Таблица 1

45

55

00 0/1

11

11

0/1

514085326

Продолжение табл. 1 налов селектор 14 выделяет три тигга:

внутренние - тип 1, граничные (имеющие трех соседей) - тип 2, угловые (имеющий двух соседей) - тип 3. Например, в случае (фиг. 8) сигналы 6,7,10 и 11 - типа 1, сигналы 2,3,8,12,15,14, 9 и 8 - типа 2, сигналы 1,4,16 и 13 - типа 3.

ности два. Из множества всех АФМ-сигК 1, N,

а на его выходах получается К-й блок информации, который представляется матрицей В из L х п элементов

и

L

1, L

К

п

к 1, N,

Эта матрица поступает на К-й пре- ,образователь 5к в код Грея, в котором каждый столбец матрицы В подается на входы одного из п ГШЗУ, на выходах которого образуется один из п столбцов матрицы сигналов в коде Грея

1

,U1|

и V .

. S ij

Bee N таких матриц образуют матриЦУ Г

Эта матрица по столбцам

поступает в канал 3 связи,

В канале 3 связи образовавшиеся после модуляции 2 -позиционные сигналы ФМ (фиг. 5) или 2 -позиционные сигналы АФМ (фиг. 6) проходят через линию 41 или 50 связи, в которой под 30 действием помех приобретают неизбежные ошибки, подлежащие в дальнейшем исправлению при декодировании избыточных корректщзующих блочных кодов.

сформированная в канале 3 связи в качестве допол штельной информ ации о/ ближайшем со седе в случае ФМ зона решения по каждому сигналу разбивается на два сектора и нумерация идет по часовой стрелке; в случае АФМ зона решения разбивается на четьфе сектора, (фиг. 7 и 8), поступает в блок 10 памяти первой ступени 9 декодирова-: ния, где они обе задерживаются на время декодирования матрицы ..

11

го частично восстанавливается исходная матрица А, т.е. получается матрица А. с ошибками.

В, в блоке (первого кода), на выходах котороВместе с задержанной матрицей

i

она поступает на блок 13,сравнения, где. завершается восстановление исходной матрицы А. (устранение помех). Для облегчения декодирования ФМ-сиг- 35 появляюшейся на первых выходах 17

кодека.

налы после модуляции сопровождаются

--- М

еще одним битом, т.е. становятся 2 позиционными, а АФМ-сигналы - позиционными в каждом квадратурном канале. После преобразования в АЦП 40 43 или 53 в цифровую форму на выходах канала 3 связи в каждом такте появляются сигналы с ошибками (отмеченВсе незадержанные матрицы (К 1,2,...,N) подаются (в случае АФМ- сигналов) на входы селектора 14 типа

которого вырабатывается одна из двух разрядных кодовых посылок: либо 00 для типа 1, либо 01 для типа 2, либо

ными знаком л) в виде параллельного кода из M+L символов, где М

N : т, или 2 для ФМ- или

К °

АФМ-сигналов соответственно. .

На входы К-го обратного преобразователя Грея (,2,... ,N) поступает один из п столбцов матрицы сигналов в коде Грея с ошибками

А А(И)

r,Hy,j. I

1, N.

На выходах К-го преобразователя 8 последующих ступенях 9к декодирования

образуется матрица В., (аналогичная

(К 2,3,...,N) с постепенным .уменьматрице Bj на входах преобразователя 5|. , но порожденная ошибками)

i 1, L j t. п,

к

К 1, N.

Затем эта матрица Bj(. и одновременно дополнительная матрица

(0

j

i 1, L, j t, n,

Q

15

К 1, N,

0

0

сформированная в канале 3 связи в качестве допол штельной информ ации о/ ближайшем со седе в случае ФМ зона решения по каждому сигналу разбивается на два сектора и нумерация идет по часовой стрелке; в случае АФМ зона решения разбивается на четьфе сектора, (фиг. 7 и 8), поступает в блок 10 памяти первой ступени 9 декодирова-: ния, где они обе задерживаются на время декодирования матрицы ..

11

го частично восстанавливается исходная матрица А, т.е. получается матрица А. с ошибками.

В, в блоке (первого кода), на выходах котороВместе с задержанной матрицей

i

Все незадержанные матрицы (К 1,2,...,N) подаются (в случае АФМ- сигналов) на входы селектора 14 типа

которого вырабатывается одна из двух разрядных кодовых посылок: либо 00 для типа 1, либо 01 для типа 2, либо

10 для типа 3. Эта посыпка одновременно с задержанными матрицами В (К 0,1,2,,..,N) обрабатьшается в блоке 12 коррекции, на выходах которого образуются частично исправленные матрицы В|(К 1 ,2,.. . ,N) число которых становится на единицу меньше

1

BK

55

1, N.

Далее эти операции повторяются в

(К 2,3,...,N) с постепенным .уменьшением объема информации, задерживаемой в блоках 10д памяти и обрабатываемой в блоках 12|{ коррекции. Восстановленные исходные матрицы А посту- g пают на соответствующие выходы 17 кодека.

Для N/2 двумерных сигналов ФМ или ДФМ по заданному вектору разбиений L (L, Lg,..., Ly) можно построить Ю цепочку из N разбиений. На i-н шаге сигнал разбивается на 2 подмножеств, для которых минимальное евклидово расстояние Л{ на i-м шаге определяется выражениями15

А. (ФМ) 4 sin( 1

-)

expa.(

для- ФМ;

для АФМ,

Л (АФМ) 3 ехр(ьр ехр М - 1

где обозначено ехр, (х) 2 .

Выберем N внешних кодов (, К,-, ,), i 1,2,...,N, и на базе вложенных подмножеств сигналов с расстоя- нием л,- и указанных кодов построим обобш;енный каскадный код, в котором первые используются в качестве внутренних сигналов, а вторые - в качестве внешних сигналов. Для такого кода квадрат минимального евклидова расстояния дается выражениями

.

(ФМ)т1п (4sin (

л ,...,М

.Lj

3- i

/,, /3 expji d:

(АФМ) min ( ).

%-,,,..,, Nexpe М-1 п

В известном устройстве вектор разбиений имеет вид

L (1,1 1).

Оценивая эффективность кодека дво- ичных блочных кодов по параметрам обобщенного каскадного кода, а именно по его расстоянию и удельной скорости R, получаем для конкретного примера сигналов АФМ при N 24,

L(2,2) L(4) L(1,1,1,1)-известно

устройство; D 4/15;

R 35/24 R 31/24 R 31/24;

откуда.видно, что даже при небольшой размерности МПС (всего 24) может быть получен значительный вьшгрьпн по ско

g

5

0

5

0

5

0

5 0

5

рости (4R 35/24 - 31/24 1/6), Эти расчеты подтверждаются результатами моделирования описанных процессов на ЭВМ, которые показывают, что сравнительно с известным устройством вьиг- рыш по скорости составляет 1-1,5 дБ, а по отношению энергия сигнала/энергия шума 1-2 дБ.

Таким образом, кодек двоичных блочных кодов обеспечивает значительное увеличение удельной скорости передачи многопозиционных сигналов при заданной избыточности кодирования (или повьшгение помехозаш 1щенности таких сигналов и помехоустойчивости кодека при заданной скорости передачи).

Формула изобретения

i-я ступень декодирования (,N-1) содержит блок памяти, блок коррекции, блок сравнения и блок декодирования, выходы которого подключены к первым входам блока сравнения и первым уп- равляющим входам блока, коррекции,первые выходы блока памяти i-й ступени декодирования соединены с первыми информационными входами блока коррекции i-й ступени декодирования, вторые выходы блока памяти i-й ступени декодирования подключены к вторым информационным входам блока коррекции и вторым входам блока сравнения i-й ступени декодирования, третьи - (N-i+2)-ro выходы блока памяти i-й ступени декодирования соединены с одноименными входами блока коррекции i-и ступени декодирования, N-я ступень декодирования содержит блок памяти, блок сравнения и блок декодирования, выходы которого и выходы блока памяти соединены соответственно с первыми и вторыми входами блока сравнения, первые выходы блока коррекции i-й ступени декодирования, кроме (N-1)-и,ступени соединены с первыми информационными входами блока памяти (i+1)-й ступени декодирования, вторые выходы блока кор рек- ции i-й ступени декодирования, кроме (N-l)-ft, подключены к вторым информационным входам блока памяти и информационным входам блока декодирования

(1+1)-й ступени декодирования, третьи- ции и К-е выходы управления синхрони- (N-i+1)-e выходы блока коррекции i-й ступени декодирования, кроме (Н-1)-й, соединены с одноименными информа- IQ декодирования К-й ступени декодирования, выходы К-го обратного преобразозатора соединены соответственно с тактовым и управляющими входами блока

вателя кода Грея являются (К+1)-ми информационными входами приемной стороны, вход синхронизатора является такционными входами блока памяти (1+1)-й ступени декодирования, выходы, блока коррекции (Н-1)-:й ступени декодирования подключены к информационным входам блока памяти и блока деко- ig товым входом приемной стороны, дирования N-й ступени декодирования, 2. Кодек по п.1, о т л и ч а первые информационные входы блока памяти первой ступени декодирования являются первыми информационными входами приемной стороны, вторые информационные входы блока памяти первой ступени декодирования объединены с информационными входами блока декодирования первой ступени декодирования, тактовые входы блоков памяти 25 всех ступеней декодирования объединены с тактовым входом канала связи, выходы блоков сравнения первой - N-й ступеней декодирования являются одноименными выходами кодека, о т л и - чающийс я тем, что, с целью повьшения скорости передачи многопо- зиционных сигналов при заданной помехоустойчивости, на передающей стороне введены преобразователи в код Грея и

ю щ и и с я тем, что блок кодирования вьтолнен на кодере, коммутаторе и мультиплексоре, выход которого соеди- 2Q нен с информационным входом кодера, выход которого соединен с информационным входом коммутатора, управляющие входы которого объединены с соответствующими управляюпц ми входами мультиплексора и являются управляющими входами блока, информационные входы мультиплексора, тактовый вход кодера и выходы коммутатора являются соответственно информационными и тактовым входами и выходами блока.

блок синхронизации, К-й выход синхро- формационным входом декодера, выход

низации и К-е выходы управления; которого (,N) подключены соответственно к тактовому и управляющим входам К-го блока кодирования, выходы которого соединены с входами К-го преобразователя в код Грея, выходы первого - N-го преобразователей в код Грея являются соответствующими выходами передающей стороны-, на приемной стороне введены N обратных преобразователей кода Грея, синхронизатор и в каждой ступени декодирования, кроме N-й, селектор типа сигнала, выходы которого соединены с вторыми управляющими входами блока коррекции данной ступени декодирования, выходы К-го обратного преобразователя кода Грея подключены к (К+1)-м информационным входам блока памяти и К-ым входам селектора типа сигнала первой ступени декодирования, первые - (N-i+1)-e входы селектора типа сигнала i-й ступени декодирования подключены соответственно к вторым - (N-i+2)-M выходам (-1)-й ступени декодирования, тактовый выход синхронизатора подключен к объединенным тактовым входам блоков памяти, К-й выход синхронизации и К-е выходы управления синхрони- декодирования К-й ступени декодирования, выходы К-го обратного преобразозатора соединены соответственно с тактовым и управляющими входами блока

вателя кода Грея являются (К+1)-ми информационными входами приемной стороны, вход синхронизатора является тактовым входом приемной стороны, 2. Кодек по п.1, о т л и ч а

товым входом приемной стороны, 2. Кодек по п.1, о т л и ч а

ю щ и и с я тем, что блок кодирования вьтолнен на кодере, коммутаторе и мультиплексоре, выход которого соеди- нен с информационным входом кодера, выход которого соединен с информационным входом коммутатора, управляющие входы которого объединены с соответствующими управляюпц ми входами мультиплексора и являются управляющими входами блока, информационные входы мультиплексора, тактовый вход кодера и выходы коммутатора являются соответственно информационными и тактовым входами и выходами блока.

0

5

которого соединен с информационным входом коммутатора, управляющие входы которого объединены с соответствующими управляющими входами мультиплексора и являются управляющими входами блока, информационные входы мультиплексора, тактовый вход декоде- ра и выходы коммутатора являются соответственно информационными и тактовым входами и выходами блока.

.4. Кодек по п.1, отличающийся тем, что синхронизатор выполнен на умножителях частоты,счетчиках и генераторе тактовых импульсов, выход которого подключен к входам первого - N-ro умножителей частоты и является тактовым выходом синхронизатора, выход К-го умножителя частоты подключен к входу К-го счетчика 5 и является К-м выходом синхронизации синхронизатора, выходы К-го счетчика являются К-ми выходами управления синхронизатора, вход генератора тактовых

0

импульсов является входом синхронизатора,

тудных модуляторах, амплитудных демодуляторах, соединенных последовательно сумматоре и линии связи, фазовращателях, аналого-цифровых преобразователях и на первом и втором цифро- аналоговых преобразователях, выходы которых подключены к входам одноименных амплитудных модуляторов, выходы

преобразователе и соединенных последовательно цифроаналоговом преобразо- юкоторых соответственно непосредственно вателе, фазовом модуляторе, линии свя-и через первый фазовращатель подклю- зи и фазовом демодуляторе, выходы ко-чены к соответствунлцим входам сумма- торого соединены с информационнымитора, выход линии связи подключен не- входами аналого- цифрового преобразо-посредственно и через второй фазовра- вателя, информационные входы цифроана-15щатель к входам соответственно перлогового преобразователя, тактовый вход и выходы аналого-цифрового преобразователя являются соответственно информационными и тактовым входами и выходами канала связи.

тудных модуляторах, амплитудных демодуляторах, соединенных последовательно сумматоре и линии связи, фазовращателях, аналого-цифровых преобразователях и на первом и втором цифро- аналоговых преобразователях, выходы которых подключены к входам одноименных амплитудных модуляторов, выходы

которых соответственно непосредственн и через первый фазовращатель подклю- чены к соответствунлцим входам сумма- тора, выход линии связи подключен не- посредственно и через второй фазовра- щатель к входам соответственно пер

вого и второго амплитудных демодуляторов, выходы которых соединены с информационными входами одноименных аналого-цифровьж преобразователей, тактовые входы которых объединены и являются тактовым входом канала связи, информационные входы цифроаналого- вых .и выходы аналого-цифровых преобразователей являются, соответственно информационными входами и выходами канала связи.

/1к 1И21кГ фиг.2

Я

(Риг.З

k-

А,

А,

УЗв

h Л

fPUB.

12

М

)

М/2LO--I

,

101

010

(2) (J) о о

° i-1

Lg. I

W о

(«)

о

(Я (10) (11)

()

о

(/О (75) о о

(Риг 8

(16)

о

| Помехоустойчивость и эффективность систем передачи информации | |||

| Под ред | |||

| А.Г | |||

| Зюко | |||

| - М.: Радио и связь, 1985, с | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Труды НИИР, 1983, № 1, с | |||

| Способ размножения копий рисунков, текста и т.п. | 1921 |

|

SU89A1 |

| Рейнгольд Э.М | |||

| и др | |||

| Комбинаторные алгоритмы | |||

| Теория и практика | |||

| - М.: Мир, 1980 | |||

| Кодек блочных кодов | 1984 |

|

SU1270899A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| IEEE Transactions on Information Theory, 1977, v.23, | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Гидравлическая передача, могущая служить насосом | 1921 |

|

SU371A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1988-07-07—Публикация

1986-11-09—Подача