(21)4280232/24-24

(22)07.07.87

(46) 23.04.89. Бнш. № 15

(71)Ленинградский электротехнический институт им. В.И.Ульянова (Ленина)

(72)А.В.Анисимов

(53)681.32(088.8)

(56)Авторское свидетельство СССР № 1145340, кл. G 06 F 7/548, 1983.

Авторское свидетельство СССР № 1319025, кл. G 06 F 7/548, 1986,

(54)УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИИ СИНУСА

(57)Изобретение относится к области вычислительной техники и может быть

использовано в качестве функционального расширителя для ЭВМ. Целью изобретения является расширение области применения. Устройство содержит триггер 1 знака мантиссы аргумента, триггер 2 знака порядка аргумента, триггер 9 знака мантиссы результата, регистры 3 мантиссы аргумента, 4 порядка аргумента, 10 порядка результата, 11 мантиссы результата, блок 5 нормализации аргумента, блок 7 обработки мантисс, блок 8 вычисления синуса, блок 12 управления, вход 6 пуска устройства. Цель достигается за счет - возможности расчета функции при лкг- бом аргументе. 6 ил.

о (g

| название | год | авторы | номер документа |

|---|---|---|---|

| СУММИРУЮЩЕЕ УСТРОЙСТВО | 1993 |

|

RU2069009C1 |

| Специализированный процессор обработки данных | 1982 |

|

SU1062715A1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1980 |

|

SU959070A1 |

| Специализированный процессор | 1983 |

|

SU1144117A1 |

| Устройство для деления чисел в форме с плавающей запятой | 1988 |

|

SU1566340A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Суммирующее устройство с плавающей запятой | 1982 |

|

SU1056182A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160429A1 |

| Устройство для извлечения квадратного корня | 1988 |

|

SU1564617A2 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1145340A1 |

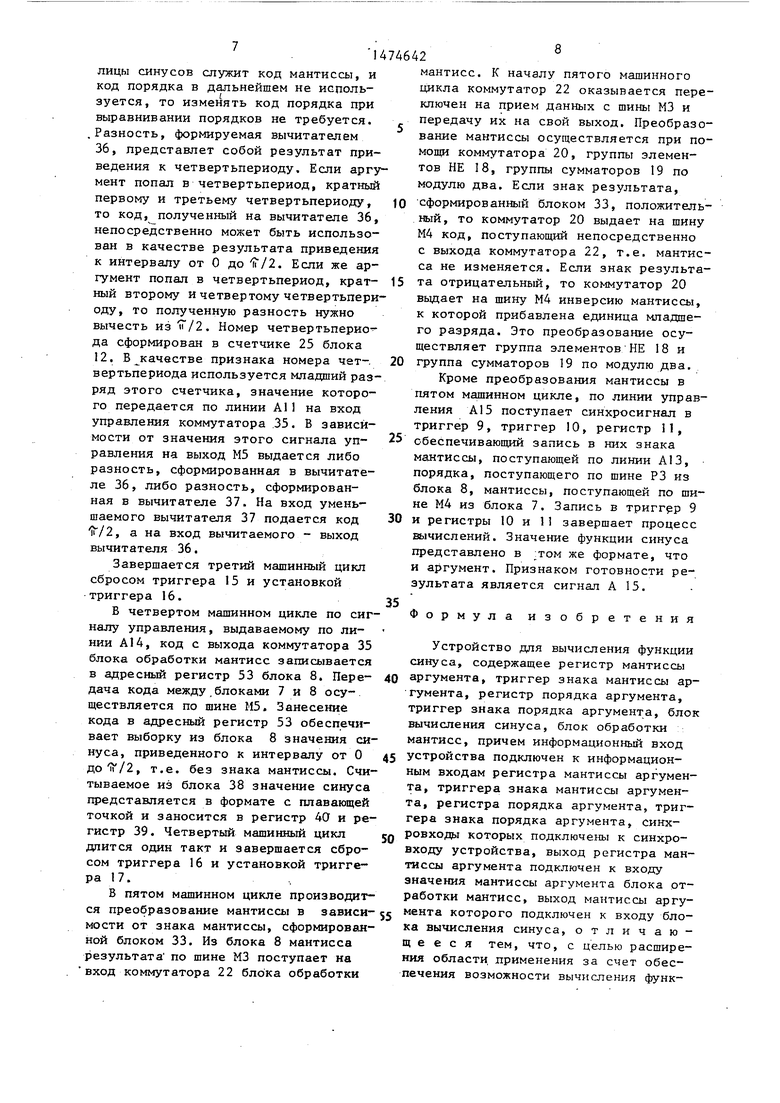

Изобретение относится к области вычислительной техники и может быть использовано в качестве функционального расширителя для ЭВМ. Целью изобретения является расширение области применения. Устройство содержит триггер 1 знака мантиссы аргумента, триггер 2 знака порядка аргумента, триггер 9 знака мантиссы результата, регистры 3, мантиссы аргумента, 4 порядка аргумента, 10 порядка результата, 11 мантиссы результата, блок 5 нормализации аргумента, блок 7 обработки мантисс, блок 8 вычисления синуса, блок 12 управления, вход 6 пуска устройства. Цель достигается за счет возможности расчета функции при любом аргументе. 6 ил.

Сброс

№.АЧ,АЮ,АУ,А1г,АЪ

А П. А15

Го/noS

Ц13

РЗ

47

ю

$ЦгХ

МЪ

мч

АН

гО

л

Ы

Ј

СЯ Ј ГО

ftS

8

A3

Фие.1

Изобретение относится к вычислительной технике и предназначено для использования в качестве функционального расширителя в микро- и мини-ЭВМ.

Цель изобретения - расширение области применения за счет возможности вычисления функции в произвольном диапазоне изменения аргумента.

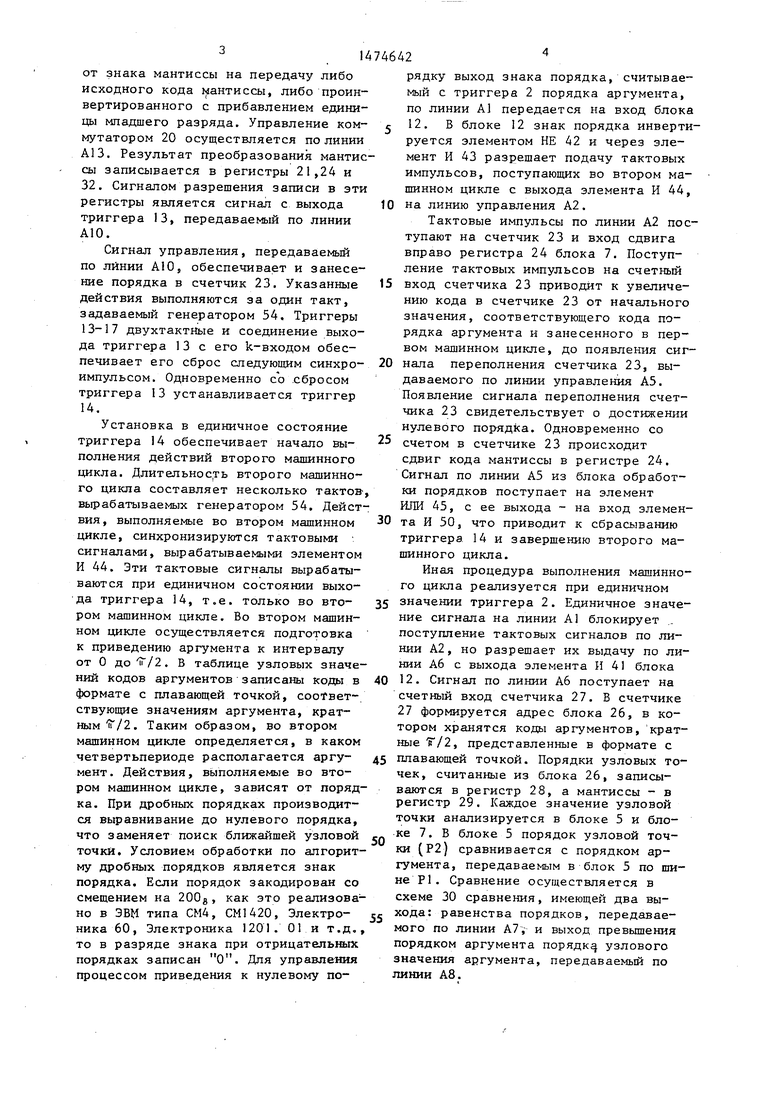

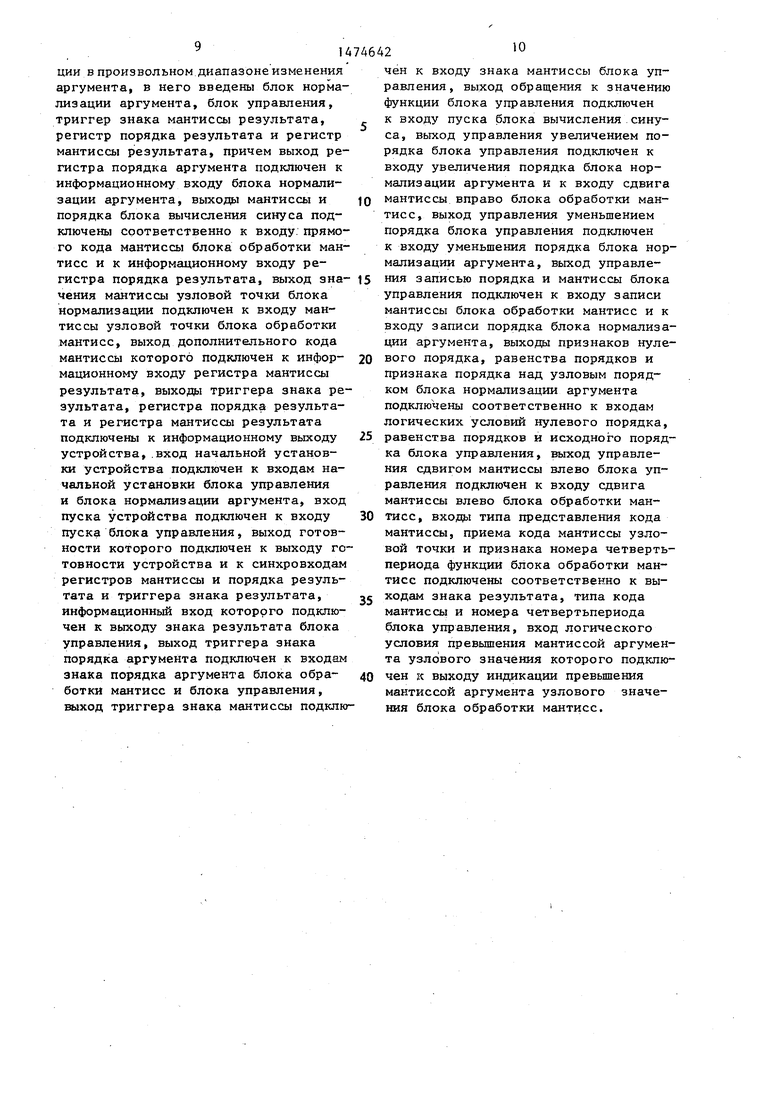

На фиг.1 изображена функциональне требуется, так как начальным значением для него является код порядка аргумента, заносимый в процессе вычислений из регистра 4. Запуск процесса вычислений функции синуса начинается с поступления сигнала Пуск

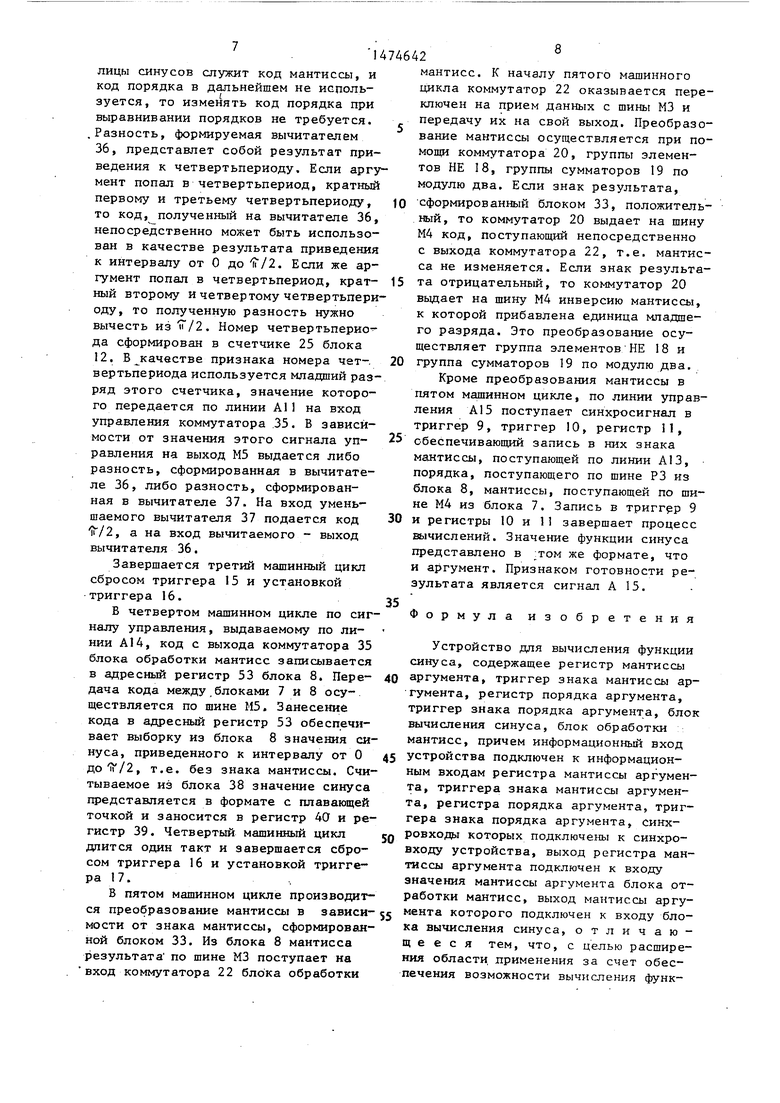

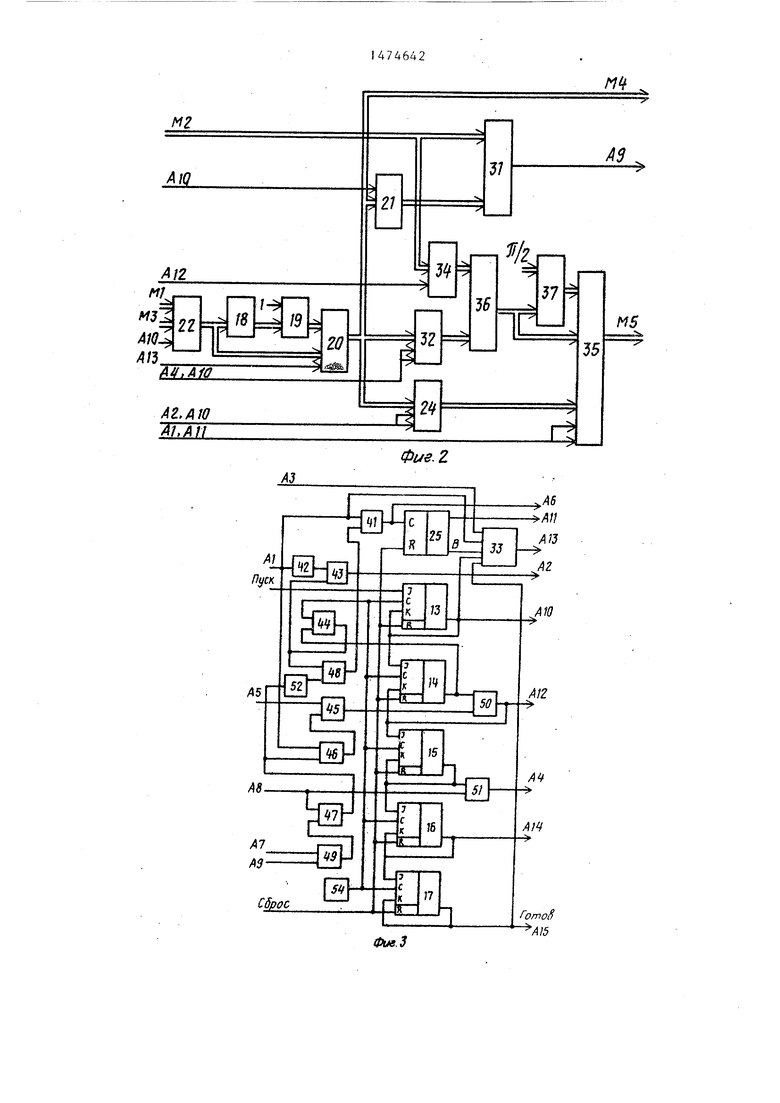

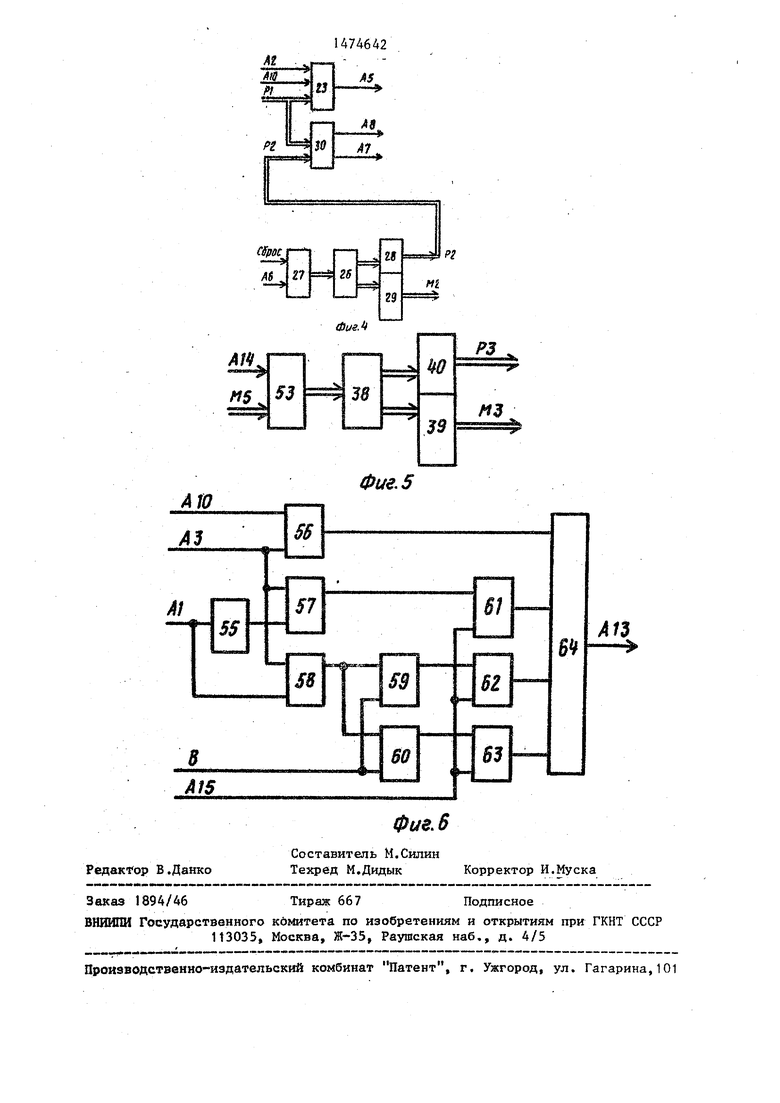

на одноименный вход устройства. Сигнал Пуск устанавливает в единичное состояние триггер 13. Это реализуетная схема устройства; на фиг.2 - схе- ся синхронно с синхросигналом, выра- ма блока обработки мантисс; нафиг.З - батываемым генератором 54. Единичные схема блока управления; на фиг.4 - схема блока нормализации аргумента; на фиг.5 - схема блока вычисления синуса; на фиг.6 - схема блока определения знака.

Устройство содержит триггер 1 знака мантиссы аргумента, триггер 2 знака порядка аргумента, регистр 3 мантиссы аргумента, регистр 4 порядка аргумента, блок 5 нормализации аргумента, вход 6 пуска устройства, блок 7 обработки мантисс, блок 8 вычисления синуса, триггер 9 знака мантиссы результата, регистр 10 порядка результата, регистр 11 мантиссы результата, блок 12 управления, триггеры 13-17, группу элементов НЕ 18, группу сумматоров 19 по модулю два, коммутатор 20, регистр 21, коммутатор 22, счетчик 23, регистр 24, счетчик

20

25

30

состояния триггеров 13-17 соответствуют пяти машинным циклам работы устройства. Машинные циклы имеют различную длительность и тактируются синхроимпульсами от генератора 54 Г

Вычисление значения функции синуса в устройстве производится путем приведения аргумента, определенного в пределах полной разрядной сетки, к интервалу от 0 до f/2. Для этого интервала в устройстве имеется таблица значений синуса, размещенная в блоке.

В первом машинном цикле осуществляется приведение аргумента к положительной полуоси. Для этой цели используется нечетность функции синуса, что позволяет преобразовать отрицательный аргумент в положительный с последующим учетом этого преобразования при определении знака функции. Поскольку мантиссы чисел с плавающей точкой принято представлять в дополнительном коде, то преобразование

В первом машинном цикле осуществляется приведение аргумента к положительной полуоси. Для этой цели используется нечетность функции синуса, что позволяет преобразовать отрицательный аргумент в положительный с последующим учетом этого преобразования при определении знака функции. Поскольку мантиссы чисел с плавающей точкой принято представлять в дополнительном коде, то преобразование

25, блок 26 памяти узловых значений кодов аргументов, счетчик 27, первый регистр 28 порядка, первый регистр 29 мантиссы, схемы 30 и 31 сравнения 35 кода аргумента осуществляется по пра- регистр 32, блок 33 определения зна- вилам1 принятым для дополнительного ка, регистр 34, коммутатор 35, вычи- татели 36 и 37, блок 38 памяти синусов, второй регистр 39 мантиссы, втокода.

Преобразование осуществляется в блоке 7. Для этой цели коммутатор 22

V-VJ13 л О i 1 JL }f 1 хл V Vsti i j л д w

рой регистр 40 порядка, элемент И 41, 40 Устанавливается на прием кода от регистра 3 и передачу его на свой выэлемент НЕ 42, элементы И 43 и 44, элемент ИЛИ 45, элемент И 46, элемент ИЛИ 47, элементы И 48-51, элемент НЕ 52, адресный регистр 53, ге нератор 54 синхроимпульсов, элемент НЕ 55, элементы И 56-59, элемент ИЛИ 60, элементы И 61-63 и элемент ИЛИ 64. Регистр 10 содержит также и знак порядка.

ход. Код от регистра 3 на вход блока 7 поступает по внутренней шине устройства Ml. Сигнал на управление 45 коммутатором 22 поступает по линии управления А10 от блока 12 управления. Сигнал А10 совпадает с состоянием триггера 13 первого машинного цикла, так как настройка коммутатоУстройство работает следующим об- 50 Ра на Рием поступающего по

шине Ml, требуется только в первом машинном цикле. Во всех последующих

Аргумент заносится в триггер 1, триггер 2, регистр 3, регистр 4 по синхросигналу СА. Перед началом вычислений в устройство выдается сигнал Сброс. Сигнал Сброс обеспечивает сброс триггеров 13-17, счетчиков 25 и 27. Счетчик 23 сбрасывать

не требуется, так как начальным значением для него является код порядка аргумента, заносимый в процессе вычислений из регистра 4. Запуск процесса вычислений функции синуса начинается с поступления сигнала Пуск

ся синхронно с синхросигналом, выра- батываемым генератором 54. Единичные

0

5

0

состояния триггеров 13-17 соответствуют пяти машинным циклам работы устройства. Машинные циклы имеют различную длительность и тактируются синхроимпульсами от генератора 54 Г

Вычисление значения функции синуса в устройстве производится путем приведения аргумента, определенного в пределах полной разрядной сетки, к интервалу от 0 до f/2. Для этого интервала в устройстве имеется таблица значений синуса, размещенная в блоке.

В первом машинном цикле осуществляется приведение аргумента к положительной полуоси. Для этой цели используется нечетность функции синуса, что позволяет преобразовать отрицательный аргумент в положительный с последующим учетом этого преобразования при определении знака функции. Поскольку мантиссы чисел с плавающей точкой принято представлять в дополнительном коде, то преобразование

5 кода аргумента осуществляется по пра- вилам1 принятым для дополнительного

ход. Код от регистра 3 на вход блока 7 поступает по внутренней шине устройства Ml. Сигнал на управление коммутатором 22 поступает по линии управления А10 от блока 12 управления. Сигнал А10 совпадает с состоянием триггера 13 первого машинного цикла, так как настройка коммутатомашинных циклах коммутатор 22 оказывается настроенным на передачу кода, поступающего по шине МЗ. Преобразование осуществляется группой элементов НЕ 18, группой сумматоров 19 по модулю два и коммутатором 20. Коммутатор 20 настраивается в зависимости

31

от знака мантиссы на передачу либо исходного кода мантиссы, либо проин- вертированного с прибавлением единицы младшего разряда. Управление ком- мутатором 20 осуществляется по линии А13. Результат преобразования мантиссы записывается в регистры 21,24 и 32. Сигналом разрешения записи в эти регистры является сигнал с выхода

триггера 13, передаваемый по линии А10.

Сигнал управления, передаваемый по линии А10, обеспечивает и занесение порядка в счетчик 23. Указанные действия выполняются за один такт, задаваемый генератором 54. Триггеры 13-17 двухтактные и соединение выхода триггера 13 с его k-входом обеспечивает его сброс следующим синхро- импульсом. Одновременно со сбросом триггера 13 устанавливается триггер 14.

Установка в единичное состояние триггера 14 обеспечивает начало вы- полнения действий второго машинного цикла. Длительность второго машинного цикла составляет несколько тактов вырабатываемых генератором 54. Действия, выполняемые во втором машинном цикле, синхронизируются тактовыми сигналами, вырабатываемыми элементом И 44. Эти тактовые сигналы вырабатываются при единичном состоянии выхода триггера 14, т.е. только во вто- ром машинном цикле. Во втором машинном цикле осуществляется подготовка к приведению аргумента к интервалу от 0 до . В таблице узловых значений кодов аргументов записаны коды в формате с плавающей точкой, соответствующие значениям аргумента, крат

ным fr/2. Таким образом, во втором машинном цикле определяется, в каком четвертьпериоде располагается аргу- дз мент. Действия, выполняемые во втором машинном цикле, зависят от порядка. При дробных порядках производится выравнивание до нулевого порядка, что заменяет поиск ближайшей узловой IJQ точки. Условием обработки по алгоритму дробных порядков является знак порядка. Если порядок закодирован со смещением на 200в, как это реализовано в ЭВМ типа СМ4, СМ1420, Электро- 55 ника 60, Электроника 1201. 01 и т.д., то в разряде знака при отрицательных порядках записан О. Для управления процессом приведения к нулевому пос10

5 0

5 0

0

з Q 5

рядку выход знака порядка, считываемый с триггера 2 порядка аргумента, по линии А1 передается на вход блока 12. В блоке 12 знак порядка инвертируется элементом НЕ 42 и через элемент И 43 разрешает подачу тактовых импульсов, поступающих во втором машинном цикле с выхода элемента И 44, на линию управления А2.

Тактовые импульсы по линии А2 поступают на счетчик 23 и вход сдвига вправо регистра 24 блока 7. Поступление тактовых импульсов на счетный вход счетчика 23 приводит к увеличению кода в счетчике 23 от начального значения, соответствующего кода порядка аргумента и занесенного в первом машинном цикле, до появления сигнала переполнения счетчика 23, выдаваемого по линии управления А5. Появление сигнала переполнения счетчика 23 свидетельствует о достижении нулевого порядка. Одновременно со счетом в счетчике 23 происходит сдвиг кода мантиссы в регистре 24. Сигнал по линии А5 из блока обработки порядков поступает на элемент ИЛИ 45, с ее выхода - на вход элемента И 50, что приводит к сбрасыванию триггера 14 и завершению второго машинного цикла.

Иная процедура выполнения машинного цикла реализуется при единичном значении триггера 2. Единичное значение сигнала на линии А1 блокирует поступление тактовых сигналов по линии А2, но разрешает их выдачу по линии Аб с выхода элемента И 41 блока 12. Сигнал по линии Аб поступает на счетный вход счетчика 27. В счетчике 27 формируется адрес блока 26, в котором хранятся коды аргументов, кратные Т/2, представленные в формате с плавающей точкой. Порядки узловых точек, считанные из блока 26, записываются в регистр 28, а мантиссы - в регистр 29. Каждое значение узловой точки анализируется в блоке 5 и блоке 7. В блоке 5 порядок узловой точки (Р2) сравнивается с порядком аргумента, передаваемым в блок 5 по шине Р1. Сравнение осуществляется в схеме 30 сравнения, имеющей два выхода: равенства порядков, передаваемого по линии А7, и выход превышения порядком аргумента порядка узлового значения аргумента, передаваемый по линии А8.

В блоке обработки мантисс мантисса узловой точки, передаваемая в блок 7 по шине М2, сравнивается с мантиссой аргумента, передаваемой в блок 7 по шине Ml. Сравнение осущест вляется в схеме 31 сравнения, имеющей один выход, фиксирующий превышение мантиссой аргумента узлового значения аргумента, передаваемого по линии А9. Счетчик 27 работает в режиме вычитания от начального значения, соответствующего максимальному коду. Поэтому единичный сигнал на выходе элемента ИЛИ 47 блока 12, блокирующий подачу тактовых импульсов на линию А6, появляется после того, как из блока памяти выбрана ближайшая слева узловая точка аргумента. Блокировка выдачи сигнала на линию А6 обеспечивается благодаря инвертированию единичного сигнала с выхода элемента ИЛИ 47 элементом НЕ 52. Сигнал с выхода элемента НЕ 52 блокирует прохождение тактовых импульсов че- рез элемент И 48, с выхода которого тактовые импульсы подаются на вход элемента И 41, выход которого соединен с линией управления А6. Кроме выходной линии А6 тактовые импульсы с выхода элемента И 41 поступают на вход счетчика 25.

Счетчик 25 позволяет определить, к какому из четвертьпериодов синусоиды относится положение аргумента на числовой оси. Выходной код счетчика 25 сохраняется неизменным после прекращения подачи тактовых импульсов на его счетный вход. Младший разряд кода счетчика 25 выдается на линию управления А11 и используется для управления коммутатором 35 блока 7. Старший разряд кода счетчика 25 поступает на вход блока 33, который вырабатывает сигнал управления на линию А13. Сигнал управления, выдаваемый по линии А13, используется для занесения знака результата в триггер 9 и для управления коммутатором 20 в блоке 7.

Завершение второго машинного цикла при единичном значении триггера 2 происходит после выбора из блока 26 ближайшей слева узловой точки по единичному сигналу на выходе элемента ИЛИ 47, который через элемент И 46 поступает на вход элемента ИЛИ 45, а с ее выхода - на вход элемента И 50, что приводит к сбрасыванию

0

0

5

5

0

5

0

триггера 14 и завершению второго машинного цикла. Кроме сбрасывания триггера 14 и установки триггера 15, что задает начало третьего машинного цикла, выходной сигнал элемента И 50 поступает на линию управления А12. Сигнал по линии управления А12 разрешает запись кода с шины М2 в регистр 34 блока 7. В процессе поиска узловых точек код в регистре 34 меняется, но сброс сигнала управления по линии А12 обеспечивает фиксацию в регистре 34 мантиссы .узловой точки, ближайшей слева к аргументу.

В третьем машинном цикле осущест- вляется приведение аргумента к интер- |Валу от 0 до и/2- При нулевом значении триггера 2, поступающем по линии управления А1 на вход управления коммутатором 35 блока 7, в третьем машинном цикле не требуется производить преобразования кодов мантисс. По сигналу управления, поступающему по линии А1, коммутатор 35 переключается на передачу кода регистра 24 на шину М5, являющуюся выходной шиной блока 7.

При единичном значении триггера 2 на выход коммутатора 35 необходимо выдать разность мантиссы аргумента и ближайшей слева узловой точки. Эта разность вычисляется вычитателем 36, на вход уменьшаемого которого подан выход регистра 32, а на вход вычитаемого - выход регистра 34. Особенностью приведения аргументов, представленных в формате с плавающей запятой, является возможность отличия на единицу порядка аргумента и узловой точки, найденной в результате поиска во втором машинном цикле. Признаком равенства порядков является сигнал, передаваемый по линии управления А7. Для выравнивания порядков после процедуры поиска ближайшей узловой точки используется сигнал, передаваемый по линии А8 и служащий признаком того, что порядок аргумента превышает порядок узловой точки. При единичном значении сигнала на линии А8 установка триггера 15 приводит к появлению на выходе элемента И 51 сигнала управления, передаваемого в блок 7 по линии А4. Этот сигнал используется для сдвига влево на один разряд кода мантиссы аргумента в регистре 32, Этот сдвиг обеспечивает выравнивание порядков. Поскольку адресом для таблицы синусов служит код мантиссы, и код порядка в дальнейшем не исполь10

20

25

30

зуется, то изменять код порядка при выравнивании порядков не требуется. Разность, формируемая вычитателем 36, представлет собой результат приведения к четвертьпериоду. Если аргумент попал в четвертьпериод, кратный первому и третьему четвертьпериоду, то код, полученный на вычитателе 36, непосредственно может быть использо ван в качестве результата приведения к интервалу от 0 до Ъ /2. Если же аргумент попал в четвертьпериод, кратный второму и четвертому четвертьпериоду, то полученную разность нужно вычесть из /2. Номер четвертьперио- да сформирован в счетчике 25 блока 12. В качестве признака номера чет- вертьпериода используется младший разряд этого счетчика, значение которого передается по линии All на вход управления коммутатора 35. В зависимости от значения этого сигнала управления на выход М5 выдается либо разность, сформированная в вычитателе 36, либо разность, сформированная в вычитателе 37. На вход уменьшаемого вычитателя 37 подается код fr/2, а на вход вычитаемого - выход вычитателя 36.

Завершается третий машинный цикл сбросом триггера 15 и установкой триггера 16.35

В четвертом машинном цикле по сигналу управления, выдаваемому по линии А14, код с выхода коммутатора 35 блока обработки мантисс записывается в адресный регистр 53 блока 8. Пере- 40 дача кода между блоками 7 и 8 осуществляется по шине 115, Занесение кода в адресный регистр 53 обеспечивает выборку из блока 8 значения синуса, приведенного к интервалу от 0 45 доЧ| /2, т.е. без знака мантиссы. Считываемое из блока 38 значение синуса представляется в формате с плавающей точкой и заносится в регистр 40 и регистр 39. Четвертый машинный циклJQ длится один такт и завершается сбросом триггера 16 и установкой триггера 17.

В пятом машинном цикле производится преобразование мантиссы в зависи- 55 мости от знака мантиссы, сформированной блоком 33. Из блока 8 мантисса результата по шине МЗ поступает на вход коммутатора 22 блока обработки

15

0

0

5

0

5

мантисс. К началу пятого машинного цикла коммутатор 22 оказывается переключен на прием данных с шины МЗ и передачу их на свой выход. Преобразование мантиссы осуществляется при помощи коммутатора 20, группы элементов НЕ 18, группы сумматоров 19 по модулю два. Если знак результата, сформированный блоком 33, положительный, то коммутатор 20 выдает на шину М4 код, поступающий непосредственно с выхода коммутатора 22, т.е. мантисса не изменяется. Если знак результа- 5 та отрицательный, то коммутатор 20 выдает на шину М4 инверсию мантиссы, к которой прибавлена единица младшего разряда. Это преобразование осуществляет группа элементов НЕ 18 и группа сумматоров 19 по модулю два. Кроме преобразования мантиссы в пятом машинном цикле, по линии управления А15 поступает синхросигнал в триггер 9, триггер 10, регистр 11, обеспечивающий запись в них знака мантиссы, поступающей по линии А13, порядка, поступающего по шине РЗ из блока 8, мантиссы, поступающей по шине М4 из блока 7. Запись в триггер 9 и регистры 10 и 11 завершает процесс вычислений. Значение функции синуса представлено в том же формате, что и аргумент. Признаком готовности результата является сигнал А 15.

Формула изобретения

Устройство для вычисления функции синуса, содержащее регистр мантиссы аргумента, триггер знака мантиссы аргумента, регистр порядка аргумента, триггер знака порядка аргумента, блок вычисления синуса, блок обработки мантисс, причем информационный вход устройства подключен к информационным входам регистра мантиссы аргумента, триггера знака мантиссы аргумента, регистра порядка аргумента, триггера знака порядка аргумента, синх- ровходы которых подключены к синхро- входу устройства, выход регистра мантиссы аргумента подключен к входу значения мантиссы аргумента блока отработки мантисс, выход мантиссы аргумента которого подключен к входу блока вычисления синуса, отличающееся тем, что, с целью расширения области применения за счет обеспечения возможности вычисления функции в произвольном диапазоне изменения аргумента, в него введены блок нормализации аргумента, блок управления, триггер знака мантиссы результата, регистр порядка результата и регистр мантиссы результата, причем выход регистра порядка аргумента подключен к информационному входу блока нормализации аргумента, выходы мантиссы и порядка блока вычисления синуса подключены соответственно к входу прямого кода мантиссы блока обработки мантисс и к информационному входу регистра порядка результата, выход значения мантиссы узловой точки блока нормализации подключен к входу мантиссы узловой точки блока обработки мантисс, выход дополнительного кода мантиссы которого подключен к информационному входу регистра мантиссы результата, выходы триггера знака результата, регистра порядка результата и регистра мантиссы результата подключены к информационному выходу устройства, вход начальной установки устройства подключен к входам начальной установки блока управления и блока нормализации аргумента, вход пуска устройства подключен к входу пуска блока управления, выход готовности которого подключен к выходу готовности устройства и к синхровходам регистров мантиссы и порядка результата и триггера знака результата, информационный вход которого подключен к выходу знака результата блока управления, выход триггера знака порядка аргумента подключен к входам знака порядка аргумента блока обработки мантисс и блока управления, выход триггера знака мантиссы подклю147464210

чен к входу знака мантиссы блока управления, выход обращения к значению функции блока управления подключен к входу пуска блока вычисления синуса, выход управления увеличением порядка блока управления подключен к входу увеличения порядка блока нормализации аргумента и к входу сдвига

10 мантиссы вправо блока обработки мантисс, выход управления уменьшением порядка блока управления подключен к входу уменьшения порядка блока нормализации аргумента, выход управле15 ния записью порядка и мантиссы блока управления подключен к входу записи мантиссы блока обработки мантисс и к входу записи порядка блока нормализации аргумента, выходы признаков нуле20 вого порядка, равенства порядков и признака порядка над узловым порядком блока нормализации аргумента подключены соответственно к входам логических условий нулевого порядка,

25 равенства порядков и исходного порядка блока управления, выход управления сдвигом мантиссы влево блока управления подключен к входу сдвига мантиссы влево блока обработки ман30 тисе, входы типа представления кода мантиссы, приема кода мантиссы узловой точки и признака номера четверть- периода функции блока обработки мантисс подключены соответственно к вы35 ходам знака результата, типа кода мантиссы и номера четвертьпериода блока управления, вход логического условия превышения мантиссой аргумента узлового значения которого подклю40 чен к выходу индикации превышения мантиссой аргумента узлового значения блока обработки мантисс.

AlQ

А /2

Ml

МЗ

-ЭГ

Л/3

AZ.A10

А17АП

т .„

31

A3

М

35

1C

57

MS

35

24

Физ.г

А13

AZ

Фие.З

А 15

А ю

A3

5В

А1

5$

$7

S8

В

Фие.5

§1

6V

МЪ

SB

№

ВО

63

Авторы

Даты

1989-04-23—Публикация

1987-07-07—Подача