шестой групп соединены с выходом дешифратора операции, входами второго и третьего элементов ИЛИ и первыми входами элементов И девятой груйпы, выход второго триггера соединенсо BTOpbJMH входами элементов И третьей, четвертой и седьмой групп, выход третьего триггера соединен со вторыми входами элементов И пятой и восьмой групп, выходы второго и третьего элементов ИЛИ соединены с первыми входами соответственно первого и второго элементов И, вторые входы которых соединены с выходом переноса первого регистра сдвига, выход первого элемента И соединен с информацион.ным входом второго регистра сдвига, выход переноса которого соединен с информационным входом третьего регистра сдвига и выходом второго элемента И, выход первого элемента ИЖ соединен со входом сдвига всех регистров сдвига, выходы разрядов с первого по третий третьего регистра сдвига соединены с первыми входами соответственно с первого по третий триггеров, вторые входы которых соединены с выходом блока сброса, выход третьего разряда первого регистра сдвига соединен со вторыми входами элементов И девятой группы, информационный вход первого регистра сдвига соединен со входом начальной установки устройства, управляняций вход регистра мантиссы результата соединен с выходом пер.вого разряда первого регистра сдвига и выходами элементов И третьей группы, управлякядий вход сумматора результата соединен с выходами элементов И четвертой и седьмой групп, управляющий вход регистра мантиссы члена ряда соединен с выходом первого разряда первого регистра сдвига и выходами элементов И пятой и девятой групп, управ;яяющий вход рёгистра мантиссы псевдо

аргумента соединен с выводами первог и второго разрядов первого регистра сдвига и третьего разряда второго регистра сдвига, управляющий вход регистра мантиссы константы соединен с входами первого разряда первого и .второго регистров, сдвига, управляющий вход коммутатора соединен с выходами элементов И шестой группы, управляющий вход счетчика адреса соединен с выходом первого разряда первого регистра сдвига и выходами элементов И первой группы,- группа управляющих входов первого умножителя соединена с выходом второго разряда второго регистра сдвига и выходами элементов И второй группы, группа управляющих входов второго умножителя соединена с выходами элементов И восьмо группы, управляющий вход регистра мантиссы ошибки соединен с выходом первого разряда первого регистра сдвига, отличающееся тем, чт.о, с целью повышения точности, в него введены счетчик порядка результата, регистр порядка константы, счетчик порядка псевдоаргумента, счетчик порядка члена ряда, первый и второй сумматоры порядка, первые и, вторые промежуточные регистры мантиссы и порядка, регистр порядка ошибки и вычитатель, первьй и второй входы мантиссы которого соединены со входами соответственно регистра мантиссы ошибки и первого промежуточного регистра мантиссы, первый и второй входы порядка вычитателя соединены с выходами соответственно регистра порядка ошибки и первого промежуточного регистра порядка, второй вход мантиссы сумматора результата соединен с выходом второго промежуточного регистра мантиссы, выход второго промежуточного регистра порядка соединен с первым входом порядка сумматора результата и информационньм входом счетчика порядка результата, выход которого соединен со вторым входом порядка сумматора результата, выход регистра мантиссы члена ряда соединен с информационными входами первого и второго промежуточных регистров мантиссы, выход счетчика порядка члена ряда соединен с информационными входами первого и второго промежуточных регистров порядка и .первым информационным входом первого сумматора порядка, выход и второй информационный вход которого соединены соответственно с инфо1рмационным входом счетчика порядка члена ряда и выходом второго сумматора по-, рядка, первый и второй информацион- |ные которого соединены с выходами .соответственно счетчика порядка псевдоаргумента и регистра порядка константы, информационный вход которого соединен с выходом счетчика порядка псевдоаргумента и установочным входом счетчика порядка члена ряда.

информационный вход счетчика порядка псевдоаргумента соединен с выходом регистра порядка константы, установочный вход которого соединен с выходами разрядов порядка блоксЗв памяти с первого по четвертый, выход вычитателя соединен со входом блока сброса, выход сумматора результата соединен с информационным входом регистра мантиссы результата, установочные входы регистра мантиссы псевдоаргумента, счетчика порядка псевдоаргумента, регистра мантиссы ошибки и регистра порядка ошибки соединены доответ ственно со входами мантиссы и порядка аргумента и мантиссы и порядка величины ошибки, причем блок управления содержит десятую и одиннадцатую группы элементов И, первые и вторые входы элементов И десятой группы соединены с выходом первого триггера и первым выходом распределителя -импульсов соответственно, первые , вторые и третьи входы элементов И одиннадцатой группы соединены соответственно с выходом второго триггера, третьим выходом распределителя импульсов и выходом сумматора результата, управлякяций вход счетчика порядка результата соединен с выходом первого разряда первого регистра сдвига, управляюпц1й вход первого промежуточного регистра мантиссы соединен с выходом первого разряда регистра сдвига и выходами элементов И десятой группы, управлямщий вход второго про 11ежуточного регистра мантиссы соединен с выходом первого разряда первого регистра сдвига и выходами элементов И десятой и одиннадцатой групп, управляющие входы первого и второго промежуточных регистров порядка соединены с выходом первого раэ|ряда первого регистра сдвига и выходами элементов И десятой группы, управляющий вход вычитателя соединен с выходами элементов И четвертой и седьмой групп, управляющий вход регистра порядка ошибки соединен с выходом первого разряда первого регистра сдвига, управляющий вход счетчика порядка члена ряда соединен с выходом первого разряда .первого регистра сдвига и выходами элементов И пятой группы, управляющий вход счетчика порядка псевдоаргумента соединен с выходами первого и второго разрядов первого регистра сдвига и второго и третьего разрядов второго регистра сдвига, управляющий вход регистра порядка константы срединен с выходом первого разряда первого регистра сдвига и выходом первого разряда второго регистра сдвига управляющие входы первого и второго сумматоров порядка соединены с выходами соответственно элементов И восьмой и второй групп.

2. Устройство по п.1, отличающее с я тем, что блок сброса содержит два элемента И, два триггера и элемент 2И-ИЛИ, первый и второй входы которого соединены с первым входом блока и первым входом первого элемента И, третий и четвертый входы элемента 2И-ШШ соединены соответственно с первым и третьим выходаъш распределителя импульсов блока управления, третий выход распределителя импульсов которого соединен со вторым входом первого элемента И, выход которого соединен с первым входом первого триггера, второй вход и выход которого соединены соответственно со. входом установки в О блока и пятьм входом элемента 2И-ИЛИ, выход которого подключен к первому входу второго триггера, второй вход и выход которого соединены соответственно со входом установки в О блока и первым входом второго элемента И, второй вход которого соединен со вторым выходом распределителя импульсов блока уп- . равления, выход второго элемента И соединен с выходом блока сброса.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления элементарных функций | 1981 |

|

SU983707A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160429A1 |

| Устройство для вычисления квадратного корня | 1984 |

|

SU1191908A1 |

| Специализированный процессор обработки данных | 1982 |

|

SU1062715A1 |

| Устройство для умножения чисел в модулярной системе счисления | 1986 |

|

SU1352483A1 |

| Устройство для вычисления корня третьей степени | 1985 |

|

SU1288695A1 |

| Устройство для возведения в степень | 1985 |

|

SU1290308A1 |

| Конвейерное устройство для потенцирования массивов двоичных чисел | 1984 |

|

SU1191909A1 |

| Устройство для обработки данных | 1987 |

|

SU1513443A1 |

| Вычислительное устройство | 1979 |

|

SU885994A1 |

1. УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ЭЛЕМЕНТАРНЫХ ФУНКЦИЙ, содержащее регистр операции дешифратор операции, блок управления, блок сброса, регистр мантиссы результата, сумматор результата, первьй и второй умножители, регистр мантиссы члена .ряда, регистр мантиссы псевдоаргумента, регистр мантиссы константы, с первого по четвертый блоки памяти, коммутатор,.счетчик адреса и регистр мантиссы ошибки, причем вход кода операции устройства подключен к информационному входу регистра операции, выход которого соединен со входом дешифратора операции, выход регистра мантиссы константы соединен с первым информационным входом первого умножителя, выход которого соединен с первым информационным входом второго умножителя и информационным входом регистра мантиссы псевдоаргумента, выход которого соединен с информационным входом регистра мантиссы константы, вторым информационным входом первого умножит.еля и установочным входом регистра мантиссы члена ряда, выход и информационный вход которого соединены соответственно со вторым информационным входом и выходом второго умножителя, выход регистра мантиссы результата соединен с первым входом мантиссы сумматцра результата, выход счетчика адреса соединен с информационным входом коммутатора, выходы с первого по четвертый которого соединены с адресными входами соответственно с первого по четвертый блоков памяти, выходы разрядов мантиссы которых соединены с установочным входом регистра мантиссы константы, причем блок управления содержит три регистра сдвига, три элемента ИЛИ, два элемента И, генератор импульсов, распределитель импульсов, три триггера и девять групп элементов И, выход генератора импуль «Л сов соединен со входом распределителя импульсов, первый выход которого соединен с первым входом первого элемента ИЛИ, первыми входами эле ментов И с первой по третью групп, второй выход распределителя импульсов соединен со вторым входом перво1 го элемента ИЛИ, первыми входами О1 элементов И четвертой группы и вто- . со рыми входами элементов И первой груп4 пы, третьи входы которых соединены с выходом первого триггера, третий выход распределителя импульсов соединен с третьим входом первого элемента ИЛИ и первыми входами элементов И пятой группы, четвертый выход распределителя импульсов соединен с четвертым входом первого элемента ИЛИ и первыми входами элементов И Q шестой по восьмую групп, выход первого триггера соединен со вторыми входами элемента И второй и шестой групп, . третьи входы элементов И первой и

Изобретение относится к вычислительной технике и служит для вычисления элементарных функций.

Известно устройство, содержащее генератор импульсов, управляемый делитель частоты, счетчик и дешифратор СО г Недостатком известного устройства является узкий класс решаемых задач Наиболее близким по технической сущности к данному является устройст во для вычисления злементарных функ 1ЩЙ5, содержащее блок управления, сумматор, два умножителя, регистр констант, регистр псевдоаргумента, четыре блока памяти коммутатор, счетчик, регистр операций, дешифратор операций, регистр ошибкиj схему сравнения, формирователь импульсов сброса5 два накопительных регистра,, причем управляющие входы первого и второго накопительных регистров соединены соответственно с первым и вторым выходами блока управления, третий,, четвертый, пятый, шестой. девятый,,десятый и седьмой ВОСЬМОЙ; выходы которого соединены с управляющими входами соответственного сумматора,, первого умножителя, регистра ошибки, второго умножителя, коммутатора, регистра констант, регистра псевдоаргумента и счетчика, выход которого соединен с информационнь1М входом коммутатора, выходы которого соединены с блоками памяти, выходы которых соединены с первым информади онньям входом регистра констант, выхо которого соединен с первым информаци он1№ж входом второго умножителя, вто рой ин.формационньш вход которого соединен с первым выходом регистра псевдоаргумента, второй и третий выходы которого соединены со вторыг-ш икформацнонньми входами регистра констант и второго накопительного ре гистра, вьссод второго умножителя соединен с информационным входом регистра псевдоаргумента и первым информационным входом первого умнолси теля, вьсход которого соединен с первыми инфopмaIЩOHны ш входами второго -накопительного регистра, первьш и BTdpoft выходы второго накопительного регистра соединены соответственно со вторьм информационным входом первого умножителя, выход которого соединен со вторым информационным входом сумматора, выход которого соединен со вторьм информацион ным входом первого накопительного регистра, выход регистра ошибки под ключен ко второму входу схемы срав нения, выход которой через формирователь импульсов сброса соединен с первым входом блока управления, вто рой вход которого сое;(инен с выходом . дешифратора операций, вход которого соединен с выходом регистра операций Г2. Недостатком данного устройства является то, что исходные данные, результаты вычислений представлены в форме, с фиксированной запятой, что значительно усложняет решение задач из-за необходимости масштабирования цифровой информации, снижает точность вычислений., Цель изобретения - повышение точности. Поставленная цель достигается тем, что в устройство для вычисления элементарных функций, содержащее регистр операции, дешифратор операции, блок управления,, блок сброса, регистр мантиссы результата, сумматор результата, первый и второй умно гштели, регистр мантиссы члена ряда, регистр мантиссы псевдоаргумента., регистр мантиссы константы, с первого цо четвертьЕЙ блоки памяти, коммутатор, счетчик адреса и -регистр мантиссы ошибки, причем вход кода операхщи устройства подключен к ин формационноь:п; входу регистра операции, выход которого соединен с входом дешифратора операции, выход регистра мантиссы константы соединен с первьм информаидонньтм входом первого умножителя, выход которого сое™ динен с первым информационным входом второго умножителя и информационным входом регистра мантиссы псевдоар- гумента выход которого.соединен с информагщонным входом регистра мантиссы константы, вторым информационным входом первого умножителя и установочным вко,дом регистра мантиссы члена ряда, выход и информадаонньй вход которого соединены соответственно с вторым информационным входом и выходом второго умножителя, выход регистра мантиссы результата соединен с первьм входом мантиссы сумматора результата., счетчика адреса соединен с информационным входом коммутатора, аыходы с первого по четвертьй которого соединен с адресными входами соответственно с первого по четвертьй блоков памяти, выходы разрядов .мантиссы которых соединены с установочным входом регистра мантиссы константы причем блок управления содержит три регистра , три элемента ИЛИ, два элемента И, генера тор импульсов, распределитель импуль сов, три триггера и девять групп эле ментов И, вьгход генератора импульсов соединен со входом распределителя импульсов, первый выход которого соединен с первым входом первого эле мента ИЛИ, первыми входами элементов И с первой по третью групп, второй выход распределителя импульсов соединен с вторьм входом первого элемента ИЛИ, первыми входами элементов И четвертой группы и вторыми входами элементов И первой группы. третьи входы которых соединены с вы- ходом первого триггера, третий выход распределителя импульсов соединен с третьим входом первого элемента ИЛИ и первыми входами элементов И пятой группы, четвертый выход распредели- теля импульсов соединен с четвертым входом первого элемента ИЛИ и первыми входами элементов И с шестой но восьмую групп, выход первого триггера соединен со вторыми входами эле- ментов И второй и шестой групп, третьи входы элементов И первой и шесто групп соединены с выходом дешифратора операции, входами второго и тре- ,тьего элементов ИЛИ и первыми входами элементов И девятой группы, выход второго триггера соединен со вторыми входами элементов И третьей, четвертой и седьмой групп, выход третье го триггера соединен со вторыми входами элементов И пятой и восьмой групп, выходы второго и третьего элементов, ИЛИ соединены с первыми входами соответственно первого и вто рого элементов И, вторые входы которых соединены с выходом переноса первогоРегистра сдвига, выход первого элемента И соединен с информационным вхбдом второго регистра сдвига, выход переноса которого соединен с информационным входом третье го регистра сдвига и выходом второго элемента И, выход первого элемента ИЛИ соединен со входами сдвига всех регистров сдвига, выходы разрядов с первого по -третий третьего регистра сдвига соединен с первыми входами соответственно с первого по третий триггеров, вторые входы которых соединены с выходом блока сбро- са, выход третьего разряда первого регистра сдвига соединен со вторыми входами элементов И девятой группы. информационный вход первого регистра сдвига соединен со входом начальной установки устройства, управляющий вход регистра мантиссы реэультата соединен с выходом первого разряда первого регистра сдвига и выходами элементов И третьей группы, управляющий вход сумматора результата соединен с выходами элементов И четвертой и седьмой групп, управляющий вход регистра мантиссы члена ряда соединен с выходом первого разряда первого регистра сдвига и выходами элементов И пятой и девятой групп, управляющий вход регистра мантиссы псевдоаргумента соединен с выходами первого и второго разрядов первого регистра сдвига и третьего разряда второго регистра сдвига, управлякяций вход регистра мантиссы константы соединен с входами первого разряда первого и второго регистров сдвига, управляющий вход коммутатора соединен с выходами элементов И шестой группы, управляювщй вход счетчика адреса соединен с выходом первого разряда первого регистра сдвига и выходами элементов И первой группы, группа управляющих входов первого умножителя соединена с выходом второго разряда второго регистра сдвига и выходами элементов И второй группы, группа управляющих входов второго умножителя соединена с выходами элементов И восьмой группы, управляюпщй ВХОД регистра мантиссы ошибки соединен с выходом первого разряда перво го регистра сдвига, дополнительно введены счетчик порядка результата, регистр порядка константы, счетчик порядка псевдоаргумента,счетчик по- рядка члена ряда, первый и второй сумматоры порядка, первые и вторые промежуточные регистры мантиссы и порядка, регистр порядка ошибки и вычитатель, первый и второй входы мантиссы которого соединены с выходами соответственно регистра мантиссы ошибки и первого промежуточного регистра мантиссы, первый и второй входы порядка вычитателя соединены с выходами соответственно регистра порядка ошибки и первого промежуточного регистра порядка, второй вход мантиссы сумматора результата соединен с выходом втсфого промежуточного регистра мантиссы, выкод второго промежуточного регистра порядка осединен с первым входом порядка сумматора результата и информационным входом счетчика порядка результата, выход которого соединен со вторым входом порядка сумматора результата, вьгход регистра мантиссы члена ряда соединен с информационными входами первого и второго промежуточных регистров мантиссы, выход счетчика порядка члена ряда соединен с информационными входами первого и второго, промежуточньк регистров порядка и первым информационным входом первого сумматора порядка, выход и второй информационный вход которого соеди нены соответственно с информационным

,входом счетчика порядка члена ряда и выходом второго сумматора порядка, первьй и второй информационные входы которого соединены с выходами соот-

ретственно счетчика порядка псевдоаргумента и регистра порядка константы, информационный вход которого соединен с выходом счетчика порядка псевдоаргумента и установочным входом счетчика порядка члена ряда, информационньрй вход счетчика порядка псевдоаргумента соединен с выходом регистра порядка константы, установочный вход которого соединен с выходами разрядов порядка блоков памяти с первого и четвертый, выход вычитателя соединен со входом блока сброса, выход сумматора результата соединен с И1в1юрмадионным входом регистра мантиссы результата, установочные входы регистра мантиссы псевдоаргумента, счетчика порядка псевдоаргумента, регистра мантиссы ошибки и регистра порядка ошибки соединены соответственно со входаьш ман;тиссы и порядка аргумента и мантиссы и порядка величины ошибки, причем блок управления содержит десятую и одиннадцатую группы элементов И, первые и вторые входы элементов И десятой группы соединены с выходом первого триггера и первым выходом распределителя импульсов соответственно первые вторые и третьи входы элементов И одиннадцатой группы соединены соответственно с выходом второго триггера, третьим эыходом распределителя импульсов и выходом сумматора результата, управляющий вход счетчика порядка результата соединен с выходом первого разряда первого регистра сдвига, управляющий вход первого промежуточного регистра мантиссы соединен с вд гходом первого разряда регистра сдвига и выходами элементов И десятой группы, управляющий вход второго промежуточного регистра мантиссы соединен с выходом первого разряда первого регистра сдвига и выходами элементов И десятой и одиннадцатой группы, управляющие входы первого и второго промежуточных регистров порядка соединены с выходом первого разряда первого регистра сдвига и выходами элементов И десятой группы, управляющий вход вычитателя соединен с выходами элементов И четвертой и седьмой группы, управляющий вход регистра порядка ошибки соединен с выходом первого разряда первого регистра сдвига, управляющий вход счетчика порядка члена ряда соединен с выходом первого разряда первого регистра сдвига и выходами элементов И пятой группы, управляклдий вход счетчика порядка псевдоаргумента соединен с выходами первого и второго разрядов первого регистра сдвига и второго и третьего разрядов второго регистра сдвига, управляющий вход регистра порядка . конс.танты соединен с выходом первого разряда первого регистра сдвига и выходом первого разряда второго регистра сдвига, управляющие входы первого и второго сумматоров порядка соединены с выходами соответственно элементов И восьмой и второй групп, причем блок сброса содержит два элемента И, два триггера и элемент 2И-ИЛИ, первый и второй входы которого соединены с первым входом блока и первым входом первого элемента И, третий и четвертый входы элемента 2И-ИЛИ соединены соответственно с первым и третьим выходами распределителя импульсов блока управ ления, третий выход распределителя импульсов которого соединен со вторы входом первого элемента И, выход которого соединен с первым входом первого триггера, второй вход и выход которого соединен соответственно со входом установки в О блока и пятым входом, элемента 2И-ИЛИ, выхо которого подключен к первому входу второго триггера, второй вход и выход которого соединены соответственно со входом установки в О блока и первым входом второго элемента И, второй вход которого соединен с вторым выходом распределителя импульсов блока управления, выход нторого з-ирмкита И соединен с выходом блока сброса

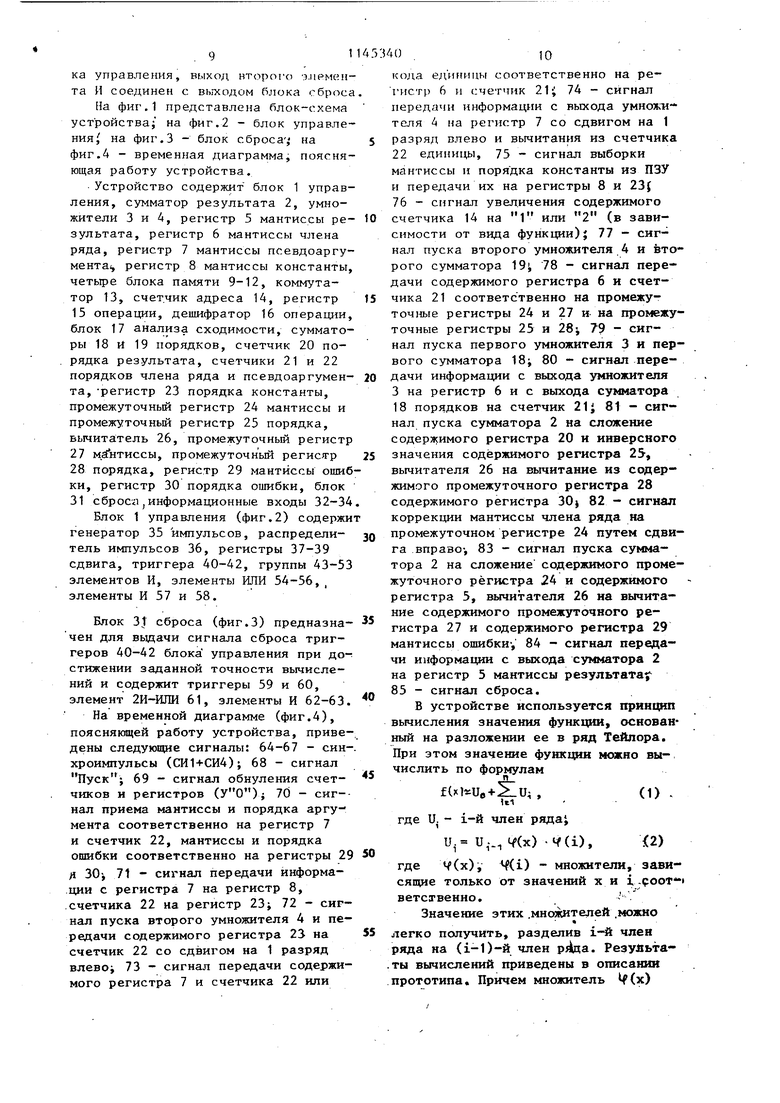

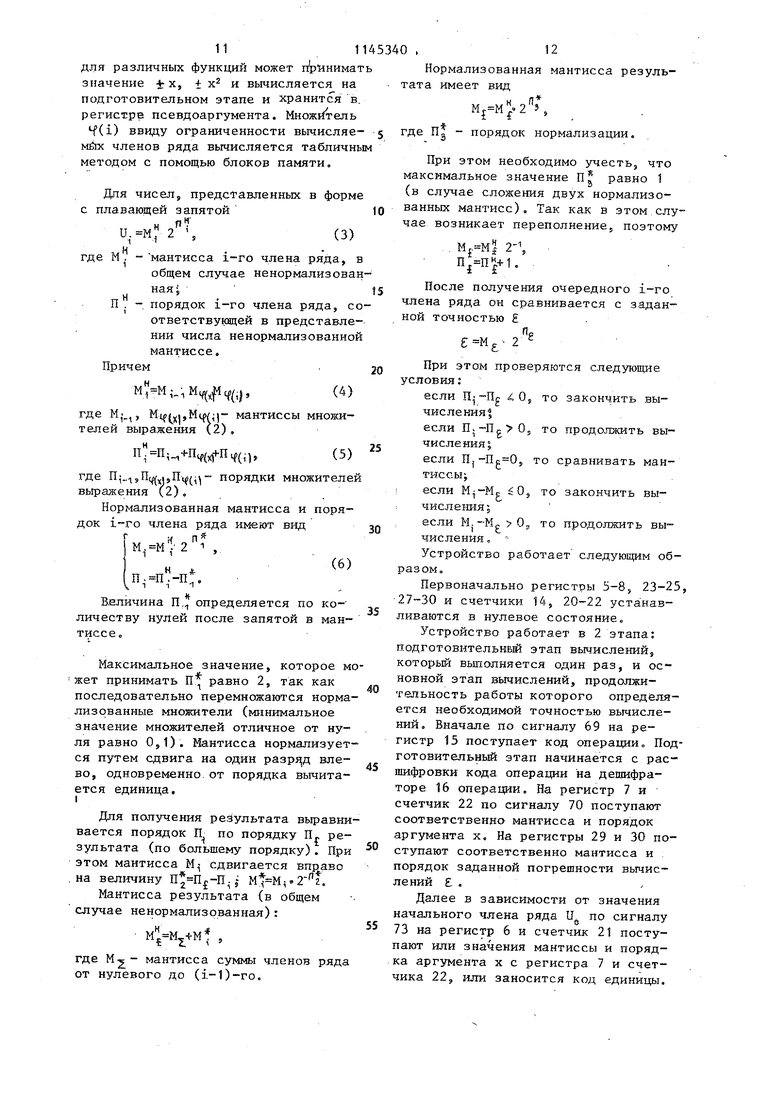

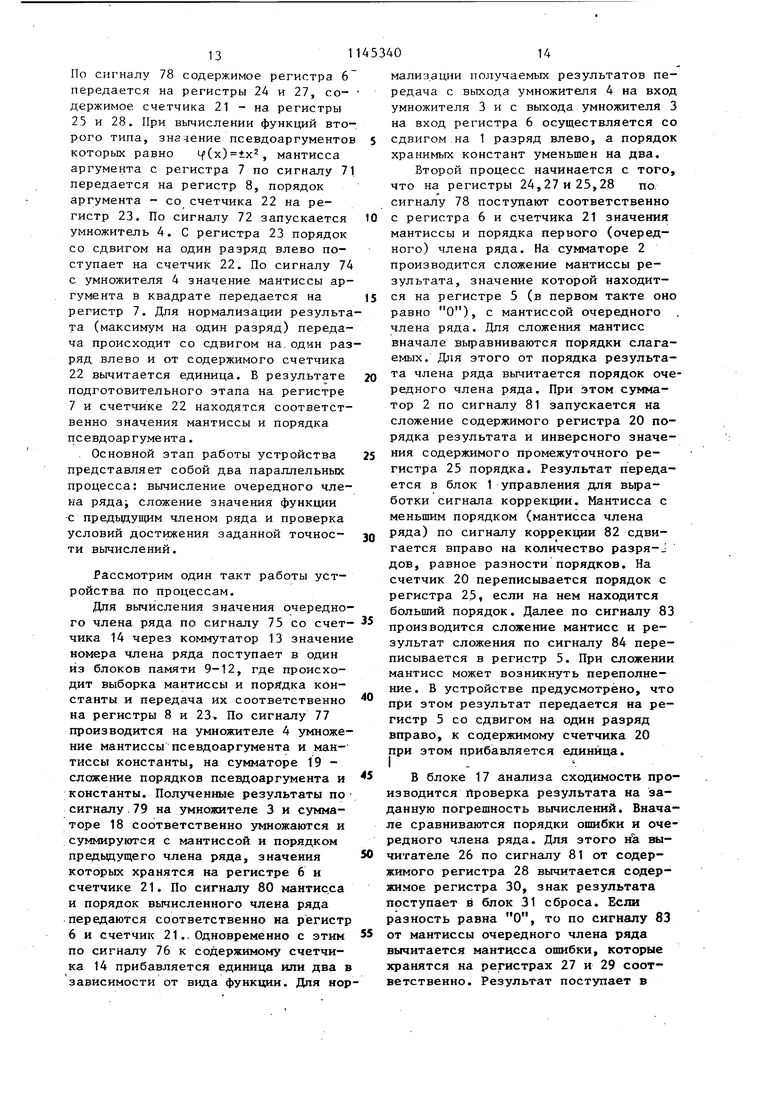

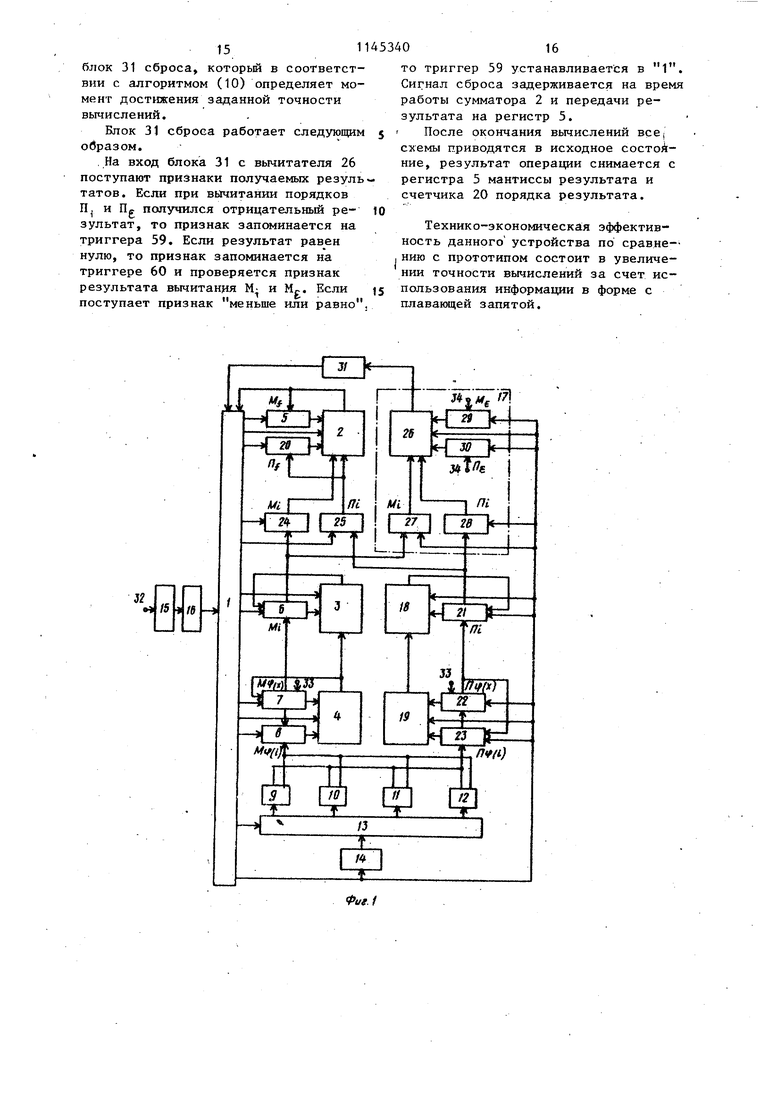

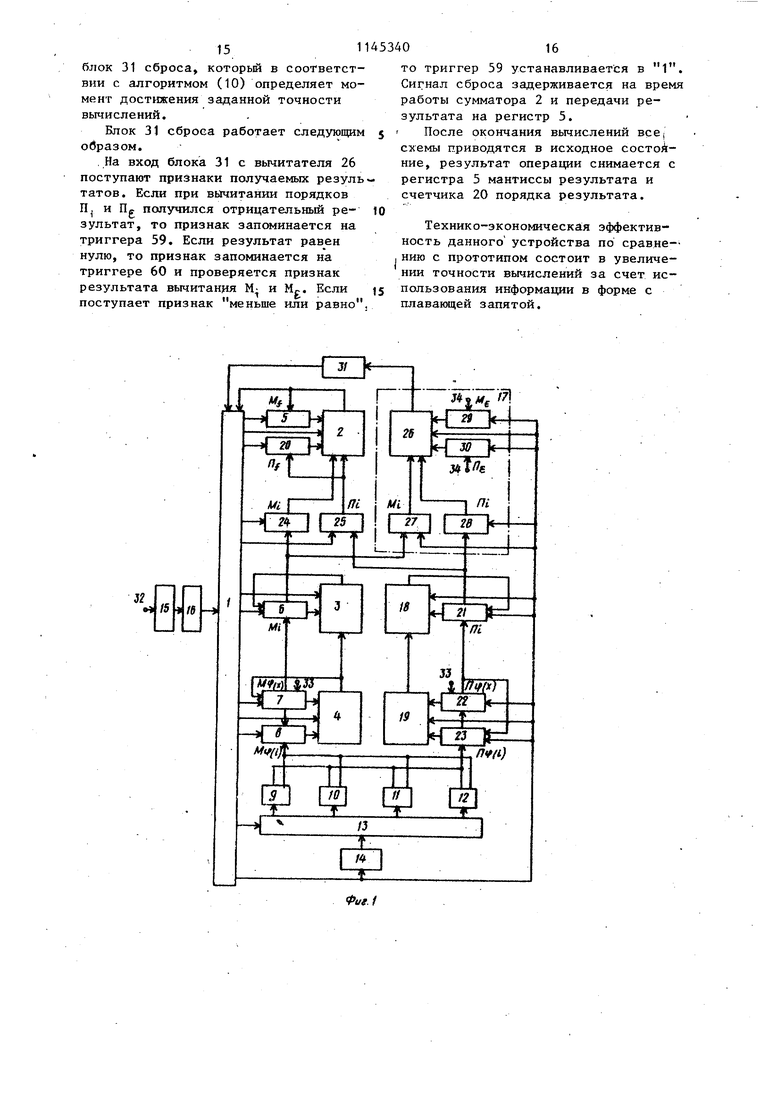

На фиг,1 представлена блок-схема устройства; на фиг.2 - блок управления J на фиг.З - блок сброса , на фиг.4 - временная диаграмма, поясняющая работу устройства.

Устройство содержит блок 1 управления, сумматор результата 2, умножители 3 и 4, регистр 5 мантиссы результата, регистр 6 мантиссы члена ряда, регистр 7 мантиссы псевдоаргумента регистр 8 мантиссы константы, четыре блока памяти 9-12, коммутатор 13, счетчик адреса 14, регистр 15 операции, дешифратор 16 операщш, блок 17 анализа сходимости, сумматоры 18 И 19 порядков, счетчик 20 порядка результата, счетчики 21 и 22 порядков члена ряда и псевдоаргумента, -регистр 23 порядка константы, промежуточный регистр 24 мантиссы и промежуточный регистр 25 порядка, вычитйтель 26, промежуточный регистр

27м.сЕнтиссы, промежуточный регистр

28порядка, регистр 29 мантиссы ошибки, регистр 30 порядка ошибки, блок 31 сброслJинформационные входы 32-34

Блок 1 управления (фиг.2) содержи генератор 35 импульсов, распределитель импульсов 36, регистры 37-39 сдвига, триггера 40-42, группы 43-53 элементов И, элементы ИЛИ 54-56,, элементы И 57 и 58.

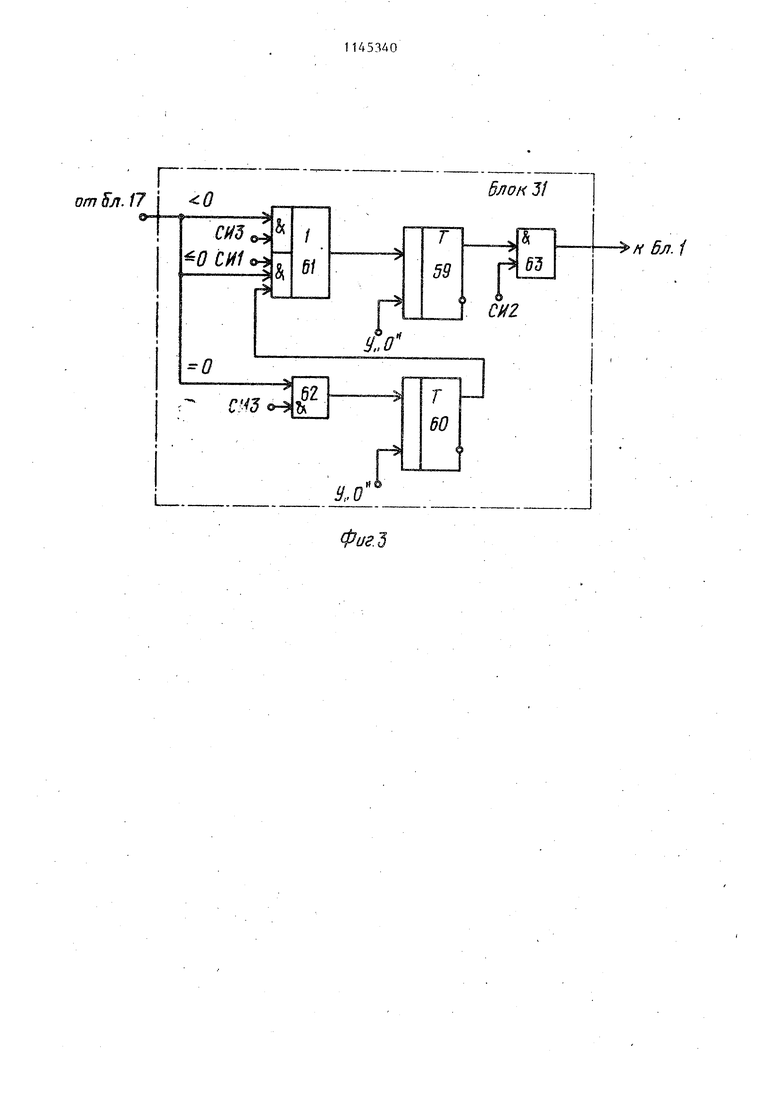

Блок 31 сброса (фиг.З) предназначей для выдачи сигнала сброса триггеров 40-42 блока управления при достижении заданной точности вычислений и содержит триггеры 59 и 60, элемент 2И-ШШ 61, элементы И 62-63.

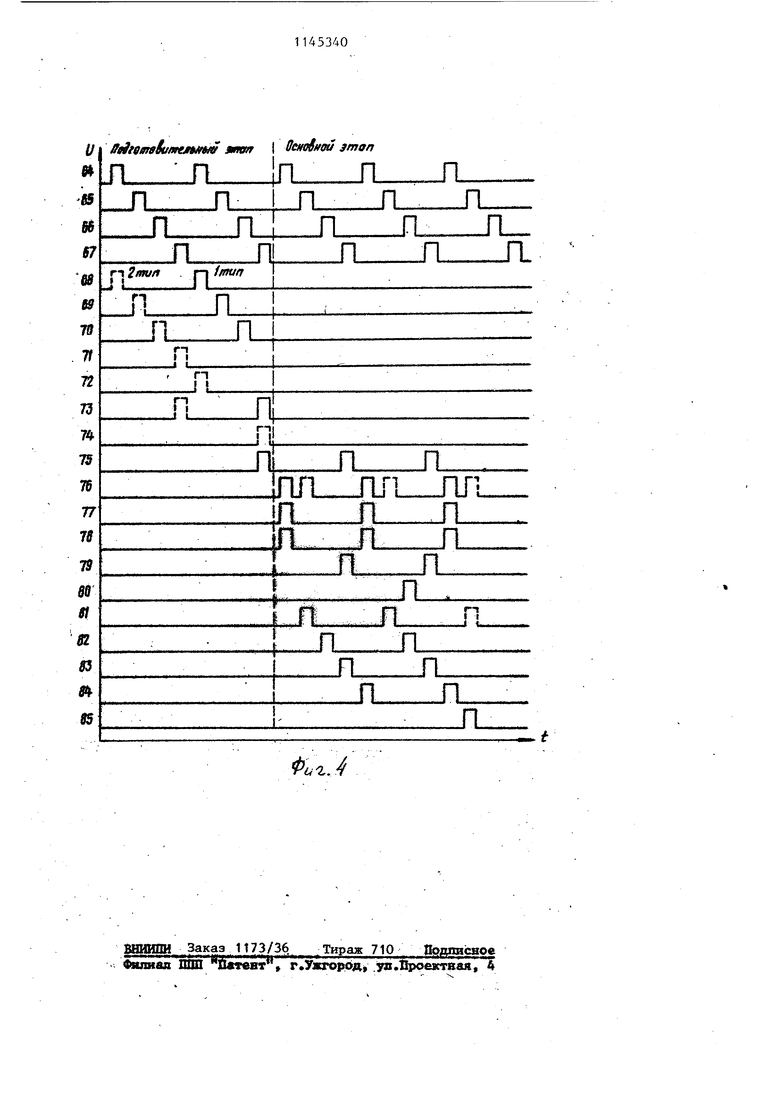

На временной диаграмме (фиг.4), поясняющей работу устройства, призедены следующие сигналы: 64-67 - синхроимпульсы (СИ1+СИ4); 68 - сигнал 69 - сигнал обнуления счетчиков и регистров ()} 70 - сигнал приема мантиссы и порядка аргумента соответственно на регистр 7 и счетчик 22, мантиссы и порядка ошибки соответственно на регистры 29 ft 30j 71 - сигнал передачи информации с регистра 7 на регистр 8, счетчика 22 на регистр 23; 72 - сигнал пуска второго умножителя 4 и передачи содержимого регистра 23 на счетчик 22 со сдвигом на 1 разряд влево; 73 - сигнал передачи содержимого регистра 7 и счетчика 22 или

кода еди1 ицьг соответственно на регистр 6 и счетчик 21i 74 - сигнал передачи информации с выхода умножителя 4 на регистр 7 со сдвигом на 1 разряд влево и вычитания из счетчика 22 едини1у 1, 75 - сигнал выборки мантиссы и порядка константы из ПЗУ и передачи их на регистры 8 и 23 76 - сигнал увеличения содержимого счетчика 14 на 1 или 2 (в зависимости от вида функции); 77 - сигнал пуска второго умножителя 4 и второго сумматора 19; 78 - сигнал передачи содержимого регистра 6 и счетчика 21 соответственно на промежуточные регистры 24 и 27 и на промежуточные регистры 25 и 28; 79 - сигнал пуска первого умножителя 3 и первого сумматора 18; 80 - сигнал передачи информации с выхода умиожителя 3 на регистр бис выхода сумматора 18 порядков на счетчик 21J 81 - сигнал пуска сумматора 2 на сложение содержимого регистра 20 и инверсного значения содержимого регистра 25, вычитателя 26 на вычитание из содержимого промежуточного регистра 28 содержимого регистра 30j 82 - сигнал коррекции мантиссы члена ряда на промежуточном регистре 24 путем сдвига вправо-, 83 - сигнал пуска сумматора 2 на сложение содержимого промежуточного регистра 24 и содержимого регистра 5, вычитателя 26 на вычитание содержимого промежуточного регистра 27 и содержимого регистра 29 мантиссы ошибки-, 84 - сигнал передачи информации с выхода сумматора 2 на регистр 5 мантиссы результатам 85 - сигнал сброса.

В устройстве используется принцип вычисления значения функции, основан ный на разложении ее в ряд Тейлора. При этом значение функции можно вычислить по формулам

Ш1 ив+$1щ, (1) .

U1

где и. - i-й член ряда

и. и.., Ч (х) -4(1), 2)

где VCx), Ж) - множители, зависящие только от значений х и i .роот ветсхвенно,Значение этих .мнозкителей .можно

«

легко получить, разделив i- член ряда на (1-1)-й член рДда. РезуЛьта.ты вычислений приведены в описании прототипа. Причем множитель lf(x) для различных функций может принима значение -t х, f х и вычисляется на подготовительном этапе и хранится в регистре псевдоаргумента. Множитель f(i) ввиду ограниченности вычисляе мйх членов ряда вычисляется табличн методом с помощью блоков памяти, Для чисел, представленных в форм с плавающей запятой U.M.J (3) н где МV - мантисса i-ro члена ряда, общем случае ненормализова ная J П . - порядок i-ro члена ряда, с ответствующей в представле нии числа ненормализованно мантиссе. Причем Mv,flc(,j,(4) -. где М;.д, ifCxI W) мантиссы множиталей выражения (2), ,4-Пц,(+Пц(, где (и9Пх( порядки множителе выражения v2). Нормализованная мантисса и порядок 1-го члена ряда имеют вид М,., ,пг - Величина П, определяется по количеству нулей после запятой в мантиссе. Максимальное значение, которое м жет принимать П равно 2, так как последовательно перемножаются норма лизованные множители (минимальное значение множителей отличное от нуля равно 0,1). Мантисса нормализует ся путем сдвига на один разря;д влево, одновременно, от порядка вычитается единица. I Для получения результата выравни вается порядок П по порядку П,. результата (по большему порядку). При этом мантисса М сдвигается вправо .на величину ,.. Мантисса результата (в общем случае ненормализованная): . (-м , где мантисса суммы членов ряда от нулевого до (i-l)-ro. Нормализованная мантисса результата имеет вид , где П - порядок нормализации. При этом необходимо заесть, что максимальное значение равно 1 (в случае сложения двух нормализованных мантисс). Так как в этом,случае возникает переполнение, поэтому . Mj.Mi 2- . . После получения очередного члена ряда он сравнивается с заданной точностью При этом проверяются следующие условия; если 4Oj то закончить вычисленияесли П. то продолжить вычисления;если П), то сравнивать мантиссы;: если 0j то закончить вычисленияесли ,, то продолжить вычисления , Устройство работает следующим образом. Первоначально регистры 5-8, 23-25, и счетчики 14, 20-22 уста:навливаются в нулевое состояние Устройство работает в 2 этапа: п.одготовительньй этап вычислений, который вьшолняется один раз, и основной этап вычислений, продолжительность работы которого определяется необходимой точностью вычислений. Вначале по сигналу 69 на регистр 15 поступает код операции Подготовительный этап начинается с расншфровки кода операции на дешифраторе 16 операции. На регистр 7 и счетчик 22 по сигналу 70 поступают соответственно мантисса и порядок аргумента х. На регистры 29 и 30 поступают соответственно мантисса и порядок заданной погрешности вычислений . Далее в зависимости от значения начального члена ряда U по сигналу 73 на регистр 6 и счетчик 21 поступают или значения мантиссы и порядка аргумента х с регистра 7 и счетчика 22, или заносится код единицы. По сигналу 78 содержимое регистра 6 передается на регистры 24 и 27, содержимое счетчика 21 - на регистры 25 и 28. При вычислении функций вто рого типа, значение псевдоаргументо которых равно (x)tx , мантисса аргумента с регистра 7 по сигналу 7 передается на регистр 8, порядок аргумента - со счетчика 22 на регистр 23. По сигналу 72 запускается умножитель 4. С регистра 23 порядок со сдвигом на один разряд влево поступает на счетчик 22. По сигналу 74 с умножителя 4 значение мантиссы аргумента в квадрате передается на регистр 7. Для нормализации результа та (максимум на один разряд) передача происходит со сдвигом на.один раз ряд влево и от содержимого счетчика 22 вычитается единица. В результате подготовительного этапа на регистре 7 и счетчике 22 находятся соответственно значения мантиссы и порядка псевдоаргумента. Основной этап работы устройства представляет собой два параллельных процесса: вычисление очередного члена ряда сложение значения функции с предьщущим членом ряда и проверка условий достижения заданной точноети вычислений. Рассмотрим один такт работы устройства по процессам. Для вычисления значения очередного члена ряда по сигналу 75 со счетчика 14 через коммутатор 13 значение номера члена ряда поступает в один из блоков памяти 9-12, где происходит выборка мантиссы и порядка константы и передача их соответственно на регистры 8 и 23. По сигналу 77 производится на умножителе 4 умножение мантиссы псевдоаргумента и мантиссы константы, на сумматоре 19 сложение порядков псевдоаргумента и константы. Полученные результаты по сигналу.79 на умножителе 3 и сумматоре 18 соответственно умножаются и суммируются с мантиссой и порядком предьщущего члена ряда, значения которых хранятся на регистре 6 и счетчике 21. По сигналу 80 мантисса и порядок вычисленного члена ряда передаются соответственно на регистр 6 и счетчик 21.. Одновременно с этим по сигналу 76 к содержимому счетчика 14 прибавляется единица или два в зависимости от вида функции. Для нор мализации получаемых результатов передача с выхода умножителя 4 на вход умножителя 3 и с выхода умножителя 3 на вход регистра 6 осуществляется со сдвигом на 1 разряд влево, а порядок хранимых констант уменьшен на два. Второй процесс начинается с того, что на регистры 24,27 и 25,28 по. сигналу 78 поступают соответственно с регистра 6 и счетчика 21 значения мантиссы и порядка первого (очередного) члена ряда. На сумматоре 2 производится сложение мантиссы результата, значение которой находится на регистре 5 (в первом такте оно равно О), с мантиссой очередного . члена ряда. Для сложения мантисс вначале вьфавниваются порядки слагаег-шх. Для этого от порядка результата члена ряда вычитается порядок очередного члена ряда. При этом сумматор 2 по сигналу 81 запускается на сложение содержимого регистра 20 порядка результата и инверсного значения содержимого промежуточного регистра 25 порядка. Результат передается в блок 1 управления для выработки сигнала коррекции. Мантисса с меньшим порядком (мантисса члена ряда) по сигналу коррекции 82 сдвигается вправо на количество разря-J дов, равное разности порядков. На счетчик 20 переписывается порядок с регистра 25, если на нем находится больший порядок. Далее по сигналу 83 производится сложение мантисс и результат сложения по сигналу 84 переписывается в регистр 5, При сложении мантисс может возникнуть переполнение . В устройстве предусмотрено, что при этом результат передается на регистр 5 со сдвигом на один разряд вправо, к содержимому счетчика 20 при этом прибавляется единица, I В блоке 17 анализа сходимости производится Проверка результата на заданную погрешность вычислений. Вначале сравниваются порядки ошибки и очередного члена ряда. Для этого на вы- читателе 26 по сигналу 81 от содержимого регистра 28 вычитается содержимое регистра 30, знак результата поступает в блок 31 сброса. Если разность равна О, то по сигналу 83 от мантиссы очередного члена ряда вычитается мантисса ошибки, которые хранятся на регистрах 27 и 29 соответственно. Результат поступает в блок 31 сброса, который в соответствии с алгоритмом (10) определяет момент достижения заданной точности вычислений. Блок 31 сброса работает следующим образом. На вход блока 31 с вычитателя 26 поступают признаки получаемых резуль татов. Если при вычитании порядков П, и П получился отрицательный результат, то признак запоминается на триггера 59. Если результат нулю, то признак запоминается на триггере 60 и проверяется признак и Mr.. Если результата вычитания поступает признак меньше или равно то триггер 59 устанавливается в 1. Сигнал сброса задерживается на время работы сумматора 2 и передачи результата на регистр 5. После окончания вычислений все схемы приводятся в исходное состоАние, результат операции снимается с регистра 5 мантиссы результата и счетчика 20 порядка результата. Технико-экономическа я эффективность данного устройства по сравне-нию с прототипом состоит в увеличении точности вычислений за счет использования информации в форме с плавающей запятой.

r&rwff

t

Фа9.2

(Sjt.5-8J,

27-50,

/r . 7 и 22 ff.S 6 и 21

/r 5я 9 и 25 я.и-и 22

/r Sjf. 7 и 22

к5п.24и27. 25 и 28

Г

9,.D

5л О К J/

.J

Ф.г.4

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для вычисления элементарных функций | 1981 |

|

SU983707A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1985-03-15—Публикация

1983-11-30—Подача