являются вторыми информационными вхо- 45 СКОЛЬЗЯ1Чего среднего - нулевой код.

дами коммутатора 19, вход 24 задания режима цифрового фильтра связан с входом задания режима блока 1 памяти.

Цифровой фильтр работает следующим образом.

Предлагаемый фильтр осуществляет в общем случае нелинейную цифровую фильтрацию входного сигнала, Так, например, ранговая фильтрация входного сигнала реализуется по формуле

YK p- Rnj(XKM14l ,...,Хк),

где К(ХЦ. „,, ,. . . ,ХН) - j-тая порядковая стати50

55

Причем на выходах формирователя 11 тактовых импульсов, как и на входе 24 фильтра, при этом поддерживаетс нулевой потенциал.

В режиме вычисления порядковых статистик на вход 24 фильтра поступ ет единичный сигнал. При этом запре щается запись в регистр 6, а мульти плексор 18 связывает выход переноса сумматора 5 с входом преобразовател 8. Кроме того, на вход 21 фильтра поступает сигнал (нулевого или еди- ичного уровня) Работа, т.е. разрешается работа формирователя 11 та

СКОЛЬЗЯ1Чего среднего - нулевой код.

Причем на выходах формирователя 11 тактовых импульсов, как и на входе 24 фильтра, при этом поддерживается нулевой потенциал.

В режиме вычисления порядковых статистик на вход 24 фильтра поступает единичный сигнал. При этом запрещается запись в регистр 6, а мультиплексор 18 связывает выход переноса сумматора 5 с входом преобразователя 8. Кроме того, на вход 21 фильтра поступает сигнал (нулевого или еди- ичного уровня) Работа, т.е. разрешается работа формирователя 11 тактовых импульсов, запрещается запись в блок 1 памяти, а коммутатор 19 связывает выходы сумматора 5 (все выходы суммы, кроме выхода младшего разряда, и выход переноса) с входами регистра 6. При поступлении тактового импульса с первого выхода формирователя .1 1 на вход блока 1 памяти на его выходах формируется старший разряд всех п слов, хранящихся в памяти, данный двоичный код поступает на входы сумматора 13 одноразрядных чисел, на выходах которого формируется код суммы количества единиц входного двоичного jc кода. Если количество единиц входного двоичного кода равно или превышает номер порядковой статистики, записанный в регистре 6, то на выходе переR 5 - R3

to

Таким образом, при / I на вы де фильтра устанавливается резуль 1001.

В режиме выполнения операции скользящего среднего на вход 24 фи тра поступает нулевой сигнал, что препятствует записи информации в р гистр 6 и запрещает запись в тригг ры первой 3 и второй 4 групп. Кром того, мультиплексор 18 связывает в ход младшего разряда сумматора 5 с входом преобразователя 8. При пост лении сигнала на вход 21 фильтра р решается работа формирователя 11 т товых импульсов, запрещается запис в блок 1 памяти, а коммутатор 19 с зывает выходы сумматора 5 с входам регистра 6. Импульсом с первого вы

носа сумматора 5 формируется единич- 20 хода Формирователя 11 разрешается

ный сигнал, который разрешает запись в триггеры второй группы 4. Иначе нулевым сигналом с выхода переноса сум- матора 5 разрешается запись в триггеры первой группы 3. Кроме того, сиг- 25 нал с выхода переноса сумматора 5 поступает на вход преобразователя 8 последовательного кода в параллельный, на выходах которого после окончания m аналогичных тактов работы фильтра -JQ формируется код порядковой статистики R j(X К.П4.1 ,. . . ,ХК) . Причем сигналом с третьего выхода формирователя I I тактовых импульсов разрешается работа умножителя 10, на выходе которого формируется результат вычислений (X fc.M4, ,. . . ,Х k). При этом в триггерах второй группы 4 нулями отмечаются слова, меньшие Rn.(X k.m,,,.. ,ХЧ), а в триггерах первой группы 3 единицами отмечаются слова, большие

Rj ( к- п+1 : к

Пример I. Работа фильтра в режиме вычисления порядковых статистик.

Пусть в блоке I памяти, хранятся 45 5 4-разрядных чисел (, )

1010

1001

0010

П0150

0101 ,

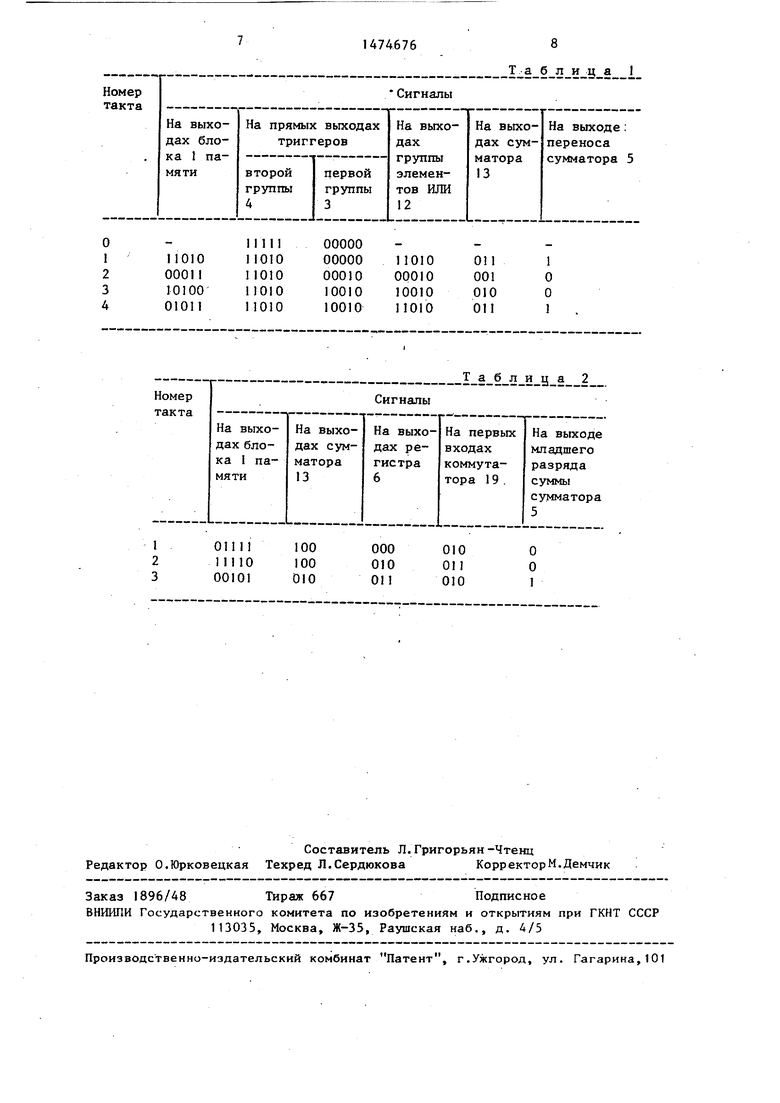

а в регистре 6 записан дополнительный код номера порядковой статистики (j(n+l))101, т.е. вычисляется „ медиана текущих отсчетов входного сигнала. Тогда работа цифрового фильтра в режиме медианной фильтрации иллюстрируется табл.I.

35

40

считывание разрядных срезов всех п слов, хранящихся в блоке I памяти начиная с младших разрядов (режим считывания информации с блока I па ти, начиная с младших разрядов, за ется нулевым сигналом, поступающим на вход блока I с входа 24 фильтра При этом на выходах сумматора 13 ф мируется код количества единиц вхо ного двоичного кода, который сумми ется с содержимым регистра 6. Прич код с выходов суммы сумматора 5 (к ме выхода младшего разряда)и значе ние сигнала с его выхода переноса (как старший разряд выходного кода записываются в регистр 6, а значен младшего разряда суммы поступает н вход преобразователя 8. После окон чания m аналоговых тактов работы фильтра на вторых входах умножител формируется код суммы п чисел, хра щихся в блоке 1 памяти (старшие ра ряды суммы поступают с выходов реги стра 6), а на первых его входах - код коэффициента усиления /5 . При по туплении на управляющий вход умножи теля 10 импульсов с третьего выхода формирователя 11 на его выходе форм руется результат вычислений.

Пример 2. Работа фильтра в режиме выполнения операции скользящего среднего.

Пусть в блоке 1 памяти хранятся 3-разрядных чисел (, m 3)

010 Oil 1 1 1 Oil 101,

c

R 5 - R3

Таким образом, при / I на выходе фильтра устанавливается результат 1001.

В режиме выполнения операции скользящего среднего на вход 24 фильтра поступает нулевой сигнал, что не препятствует записи информации в регистр 6 и запрещает запись в триггеры первой 3 и второй 4 групп. Кроме того, мультиплексор 18 связывает выход младшего разряда сумматора 5 с входом преобразователя 8. При поступлении сигнала на вход 21 фильтра разрешается работа формирователя 11 тактовых импульсов, запрещается запись в блок 1 памяти, а коммутатор 19 связывает выходы сумматора 5 с входами регистра 6. Импульсом с первого вы5 JQ

.

5

0

5

0

считывание разрядных срезов всех п слов, хранящихся в блоке I памяти, начиная с младших разрядов (режим считывания информации с блока I памя- ти, начиная с младших разрядов, задается нулевым сигналом, поступающим на вход блока I с входа 24 фильтра). При этом на выходах сумматора 13 формируется код количества единиц входного двоичного кода, который суммируется с содержимым регистра 6. Причем код с выходов суммы сумматора 5 (кроме выхода младшего разряда)и значение сигнала с его выхода переноса (как старший разряд выходного кода) записываются в регистр 6, а значение младшего разряда суммы поступает на вход преобразователя 8. После окончания m аналоговых тактов работы фильтра на вторых входах умножителя формируется код суммы п чисел, хранящихся в блоке 1 памяти (старшие разряды суммы поступают с выходов регистра 6), а на первых его входах - код коэффициента усиления /5 . При поступлении на управляющий вход умножителя 10 импульсов с третьего выхода формирователя 11 на его выходе формируется результат вычислений.

Пример 2. Работа фильтра в режиме выполнения операции скользящего среднего.

Пусть в блоке 1 памяти хранятся 5 3-разрядных чисел (, m 3)

010 Oil 1 1 1 Oil 101,

а р 101. Тогда работа цифрового фильтра в режиме вычисления среднего арифметического п чисел иллюстрируется табл. 2.

Таким образом, на первых входах умножителя 10 становится код суммы (10100), а на его выходах - результат вычислений (100).

Формула изобретения

Цифровой фильтр, содержащий регистр, выходы которого подключены к старшим разрядам входа множимого ум- ножителя, вход множителя которого соединен с выходом блока памяти коэффициентов, выход множителя является информационным выходом фильтра, формирователь тактовых импульсов, пер- вый выход которого подключен к входу считывания блока памяти,, информационные выходы которого соединены соответственно с первыми входами элементов И группы, первую и вторую группы триггеров, входы установки в 1 триггеров второй группы объединены с входом записи блока памяти и являются входом начальной установки фильтра, прямые выходы триггеров второй труп- пы подключены соответственно к вторым входам элементов И группы, второй выход формирователя тактовых импульсов соединен с тактовым входом преобразователя последовательного кода в параллельный, первый элемент И о т- личающийся тем, что, с целью повышения быстродействия, в него введены сумматор одноразрядных чисел, второй элемент И, элемент ИЛИ- НЕ, первый и второй элементы НЕ, коммутатор, мультиплексор и группа элементов ИЛИ, первые входы которых соединены с выходами соответствующих элементов И группы, а вторые входы - с прямыми выходами соответствующих триггеров первой группы9 синхровхо- ды которых соединены с выходом второго элемента И, информационные входы триггеров первой группы объедине- ны с информационными входами одно

5 0 5 0 5 0 45 0

именных триггеров второй группы, с одноименными входами сумматора одноразрядных- чисел и подключены к выходам соответствующих элементов ИЛИ группы, выход сумматора одноразрядных чисел соединен с входом первого слагаемого сумматора, выход младшего разряда которого соединен с первым входом мультиплексора, выход которого подключен к информационному входу преобразователя последовательного кода в параллельный, выход которого соединен с входом младшего разряда множимого умножителя, тактовый вход умножителя подключен к третьему выходу формирователя тактовых импульсов, вход синхронизации которого объединен с входами установки в О триггеров первой группы, с управляющим входом коммутатора и является входом начальной установки фильтра, вход задания режима блока памяти объединен с первыми входами элемента ИЛИ-НЕ,, первого и второго элементов И, с управляющим входом мультиплексора и является входом задания режима фильтра, второй вход элемента ИЛИ-НЕ подключен к выходу первого элемента НЕ, вход которого объединен с вторыми входами первого и второго элементов И и соединен с вторым выходом формирователя тактовых импульсов, выход переноса сумматора подключен к третьему входу первого элемента И, к второму входу мультиплексора, к одному из информационных входов первой группы коммутатора и к входу второго элемента НЕ, выход которого соединен с третьим входом второго элемента И, выходы старших разрядов сумматора подключены к другим информационным входам первой группы коммутатора, вторая группа информационных входов которого является входом установки фильтра, выход коммутатора соединен с информационным входом регистра, выход которого подключен к входу второго слагаемого сумматора, тактовый вход регистра соединен с выходом элемента ИЛИ-НЕ.

Т j

| название | год | авторы | номер документа |

|---|---|---|---|

| Скалярный умножитель векторов | 1988 |

|

SU1619254A1 |

| Цифровой фильтр | 1985 |

|

SU1244786A1 |

| Устройство для сглаживания сигналов | 1987 |

|

SU1437877A1 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

| Устройство для контроля последовательности байтов данных дисковой памяти | 1985 |

|

SU1315979A1 |

| Устройство для сложения чисел с переменным основанием системы счисления | 1985 |

|

SU1310809A1 |

| Устройство для вычисления порядковых статистик последовательностей из @ - @ -разрядных чисел | 1987 |

|

SU1434424A1 |

| Цифровой рекурсивный фильтр | 1988 |

|

SU1578720A1 |

| ЦИФРОВОЙ ФИЛЬТР | 1991 |

|

RU2029362C1 |

| Последовательное множительное устройство | 1985 |

|

SU1307455A1 |

Изобретение относится к вычислительной технике и может использоваться в системах цифровой обработки информации. Быстродействие цифрового фильтра возрастает за счет распараллеливания процесса вычисления порядковых статистик и скользящего среднего по словам массива памяти. Цифровой фильтр содержит блок памяти 1, состоящий из NM разрядных ячеек, группу N элЕМЕНТОВ И 2, первую 3 и вторую 4 группы N триггеров, сумматор 5, регистра 6, первый элемент И 7, преобразователь 8 последовательного кода в параллельный,блок 9 памяти коэффициентов, умножитель 10, формирователь 11 тактовых импульсов, группу элементов ИЛИ 12, сумматор 13 одноразрядных чисел, второй элемент И 14, элемент ИЛИ-НЕ 15, первый 16 и второй 17 элементы НЕ, мультиплексор 18 и коммутатор 19. Сущность работы цифрового фильтра заключается в том, что процесс вычисления порядковых статистик и скользящего среднего ведется параллельно по словам и последовательно по разрядам, т.е. за M тактов работы цифрового фильтра. 1 ил.

| Устройство для вычисления порядковых статистик последовательности двоичных чисел | 1984 |

|

SU1239708A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Цифровой фильтр | 1985 |

|

SU1244786A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-04-23—Публикация

1987-07-06—Подача