;б

фив.1

Изобретение относится к электросвязи, вычислительной технике и может использоваться в цифровых системах передачи данных в коде Ман- честер-2.

Цель изобретения - расширение функциональных возможностей декодера счет автоматической подстройки к изменению тактовой частоты входно- го сигнала.

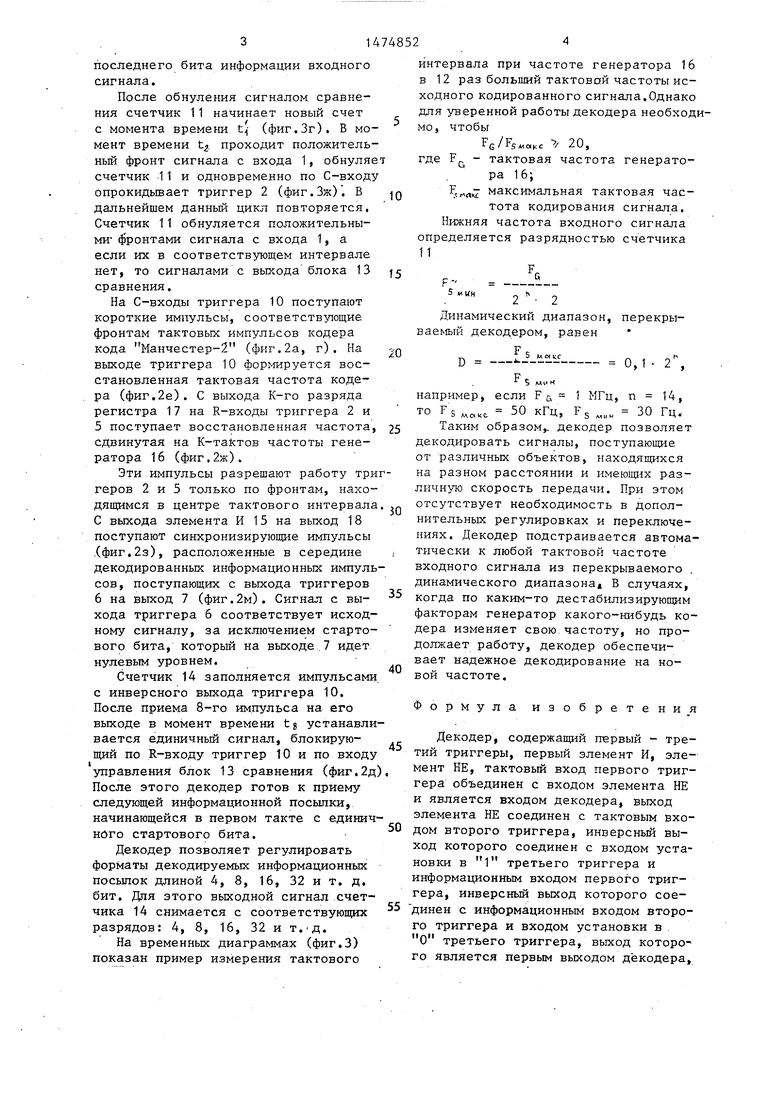

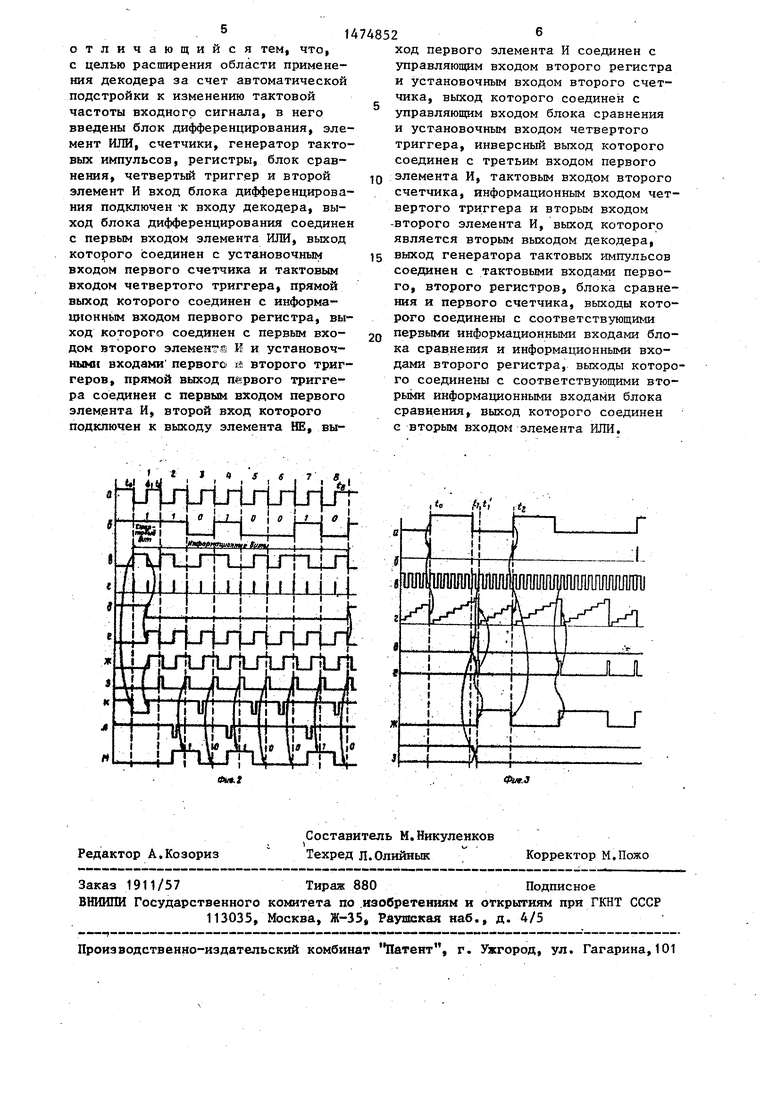

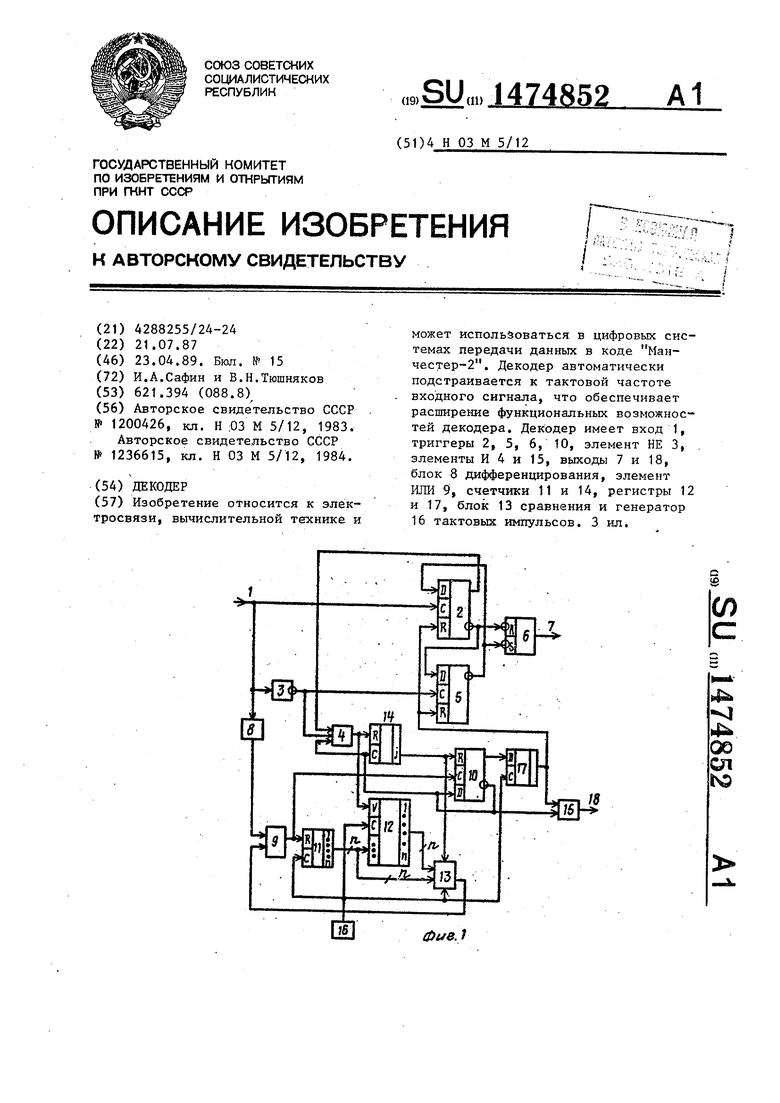

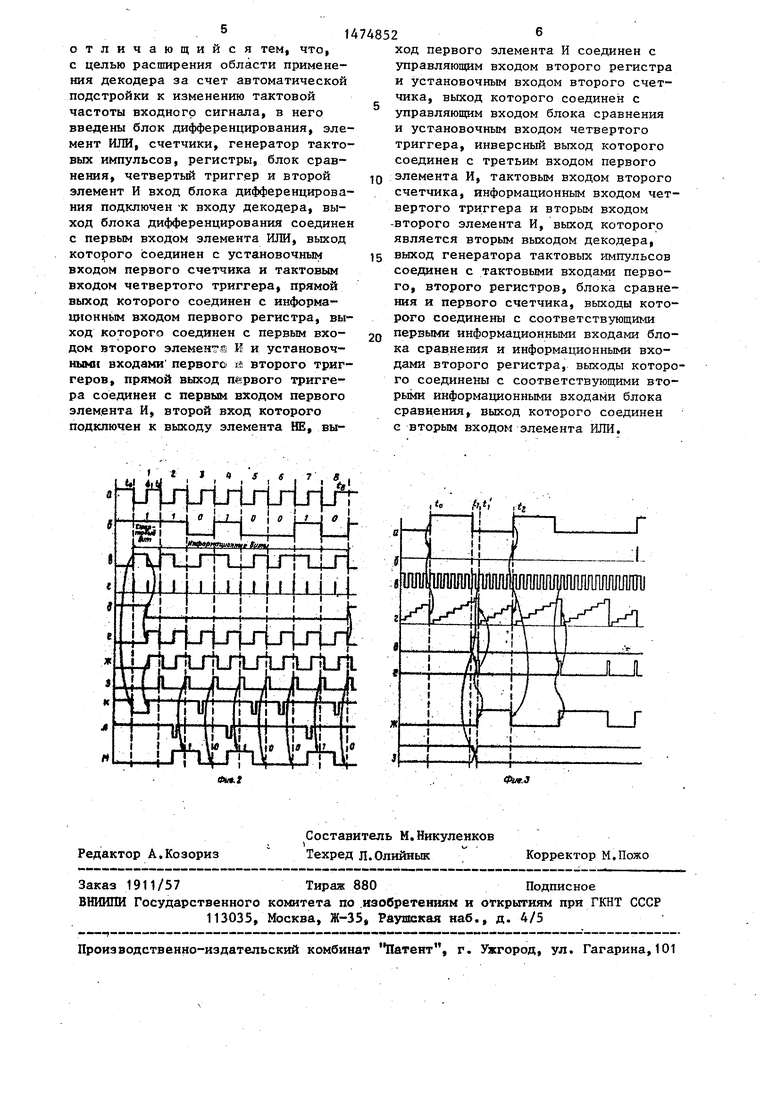

На фиг.1 изображена функциональная схема декодера} на фиг.2 и 3 - временные диаграммы, поясняющие работу и,принцип восстановления тактовой частоты кодера при декодировании сигнала форматом 8 бит.

Декодер (фиг.1) имеет вход 1, первый триггер 2, элемент НЕ 3, первый элемент И 4, второй 5 и третий б триггеры, первый вых;;д 7, блок 8 дифференцирования, элемент ИЛИ 9, четвертый триггер 10, первый счетчик 11, второй регистр 12 параллельной записи, блок 13 сравнения, второй счетчик 14, второй элемент И 15, генератор 16 тактовых импульсов, первый регистр 17 сдвига и второй выход 18.

Принцип работы декодера основан на выделении из выходного сигнала с определенным форматом информационных и тактовых импульсов. Декодер измеряет половину первого тактового интервала сигнала и по измеренному значению воспроизводит импульсы, по частоте и фазе совпадающие с тактовы ми импульсами кодера.

Декодер работает следующим образом.

При отсутствии на входе.1 входного сигнала декодер устанавливается в исходное состояние. При этом счетчик -14 выходным сигналом блокирует триггер 10 по R-входу и по входу управления выключает блок 13 сравнения. Первый 2 и второй 5 триггеры обнулены и готовы к приему информации по С-входам, Нулевой сигнал с прямого выхода триггера 2 блокирует элемент И 4. Регистр 12 параллельной записи находится в состоянии запрета записи. Счетчик 11 последовательно считает по отрицательному фронту импульсы генератора 16.

На фиг.2а, б, в показано формирование кода Манчестер-2 форматом в 8 ;бит в кодере. Единичный бит сигнала, принимаемый в первом тактовом

0 „

0

с

0

интервале, является стартовым битом. В момент времени t0 стартовый бит кода поступает на вход 1 декодера (фиг.2в и За). Положительный фронт сигнала опрокидывает триггер 2 (фиг.2к) и единичный сигнал с его прямого выхода поступает на второй вход элемента И 4. Одновременно продифференцированный фронт сигнала через элемент ИЛИ 9 сбрасывает счетчик 11 в нулевое состояние (фиг.Зб, г). Триггер 10 при этом не реагирует на сигнал по С-входу, так как блокирован сигналом с выхода счетчика 14. Счетчик 11 начинает считать тактовые импульсы (фиг.Зв, г) генератора 16. В момент времени t1, соответствующий половине тактового интервала, на входе 1 устанавливается низкий уро- вень, который через элемент НЕ 3 не открывает элемент И 4. С выхода элемента И 4 единичный сигнал (фиг.Зд) разрешает по входу управления запись в регистр 12, а также обнуляет счетчик 14. Сигнал с выхода счетчика 14 (фиг.2д) разрешает работу по С.-вхо- ду триггера 10 и по входу управления включает блок 13 сравнения. Регистр 12 по положительному фронту тактового импульса генератора 16 переписывает на содержимое счетчика 1 1 (фиг.Зз). По этому же тактовому импульсу блок 13 сравнения выдает сигнал равенства (фиг.Зе) выходных значений счетчика 11 и регистра 12. Этот сигнал через элемент ИЛИ 9 обнуляет счетчик 11 и опрокидывает по С-входу триггер 10. Нулевой сигнал с инверсного триггера 10 закрывает элемент И 4. Тем самым запрещается дальнейшая запись в регистр 12 и снимается блокировка со счетчика 14 (фиг.Зд).

Временное положение сигнала сравнения сдвигается на один такт частоты генератора 16 относительно фронта тактовой частоты кодера, но это несоответствие не будет накапливаться из такта в такт, так как начальное состояние счетчика 11 периодически корректируется положительными фронтами сигнала с шины устройства. i

Таким образом, в регистре 12 фиксируется код, соответствующий во временной области половине периода тактовой частоты кодера. Этот код хранится до окончания декодирования

последнего бита информации входного сигнала.

После обнуления сигналом сравнения счетчик 11 начинает новый счет с момента времени t,, (фиг.Зг). В момент времени t2 проходит положительный фронт сигнала с входа 1, обнуляе счетчик 11 и одновременно по С-входу опрокидывает триггер 2 (фиг.Зж). В дальнейшем данный цикл повторяется. Счетчик 11 обнуляется положительными ф ронтами сигнала с входа 1, а если их в соответствующем интервале нет, то сигналами с выхода блока 13 сравнения.

На С-входы триггера 10 поступают короткие импульсы, соответствующие фронтам тактовых импульсов кодера кода Манчестер-2 (фиг.2а, г). На выходе триггера 10 формируется восстановленная тактовая частота кодера (фиг.2е). С выхода К-го разряда регистра 17 на R-входы триггера 2 и

5поступает восстановленная частота, сдвинутая на К-тактов частоты генератора 16 (фиг.2ж).

Эти импульсы разрешают работу тригеров 2 и 5 только по фронтам, находящимся в центре тактового интервала С выхода элемента И 15 на выход 18 поступают синхронизирующие импульсы (фиг.2з), расположенные в середине декодированных информационных импульсов, поступающих с выхода триггеров

6на выход 7 (фиг.2м). Сигнал с выхода триггера 6 соответствует исходному сигналу, за исключением стартового бита, который на выходе 7 идет нулевым уровнем.

Счетчик 14 заполняется импульсами с инверсного выхода триггера 10. После приема 8-го импульса на его выходе в момент времени tj устанавли

Формула изобретения Декодер, содержащий первый - тре50

мент НЕ, тактовый вход первого триггера объединен с входом элемента НЕ и является входом декодера, выход элемента НЕ соединен с тактовым входом второго триггера, инверсный вывается единичный сигнал, блокирующий по R-входу триггер 10 и по входу тий триггеры, первый элемент И, эле- управления блок 13 сравнения (фиг.2д). После этого декодер готов к приему следующей информационной посылки, начинающейся в первом такте с единичного стартового бита.

Декодер позволяет регулировать форматы декодируемых информационных посылок длиной 4, 8, 16, 32 и т. д. бит. Для этого выходной сигнал счетчика 14 снимается с соответствующих разрядов: 4, 8, 16, 32 и т. д.

На временных диаграммах (фиг.З) показан пример измерения тактового

ход которого соединен с входом установки в 1 третьего триггера и информационным входом первого триггера, инверсный выход которого сое- 55 динен с информационным входом второго триггера и входом установки в

О третьего триггера, выход которого является первым выходом декодера,

О

интервала при частоте генератора 16 в 12 раз больший тактовой частоты исходного кодированного сигнал а. Однако для уверенной работы декодера необходимо, чтобы

F6/F MOIKC 20,

где F - тактовая частота генератора 1 6;

Р,„п- максимальная тактовая частота кодирования сигнала. Нижняя частота входного сигнала определяется разрядностью счетчика 11

F-. , JL

5 «кн 2 n „

Динамический диапазон, перекрываемый декодером, равен

F D -

F,

s м

0,1 2

S ми «

например, если Fu 1 МГц, п 14,

то Г5 Meitt 50 кГц, F,

30 Гц.

Таким образом,, декодер позволяет декодировать сигналы, поступающие от различных объектов, находящихся на разном расстоянии и имеющих различную скорость передачи. При этом отсутствует необходимость в дополнительных регулировках и переключениях. Декодер подстраивается автоматически к любой тактовой частоте входного сигнала из перекрываемого динамического диапазона, В случаях, когда по каким-то дестабилизирующим факторам генератор какого-нибудь кодера изменяет свою частоту, но продолжает работу, декодер обеспечивает надежное декодирование на новой частоте.

Формула изобретения Декодер, содержащий первый - тре

мент НЕ, тактовый вход первого триггера объединен с входом элемента НЕ и является входом декодера, выход элемента НЕ соединен с тактовым входом второго триггера, инверсный вытий триггеры, первый элемент И, эле-

ход которого соединен с входом установки в 1 третьего триггера и информационным входом первого триггера, инверсный выход которого сое- динен с информационным входом второго триггера и входом установки в

О третьего триггера, выход которого является первым выходом декодера,

отличающийся тем, что, с целью расширения области применения декодера за счет автоматической подстройки к изменению тактовой частоты входного сигнала, в него введены блок дифференцирования, элемент ИЛИ, счетчики, генератор тактовых импульсов, регистры, блок сравнения, четвертый триггер и второй элемент И вход блока дифференцирования подключен -к входу декодера, выход блока дифференцирования соединен с первым входом элемента ИЛИ, выход которого соединен с установочным входом первого счетчика и тактовым входом четвертого триггера, прямой выход которого соединен с информационным входом первого регистра, выход которого соединен с первым входом второго элемент И и установочными входами первого if второго триггеров, прямой выход первого триггера соединен с первым входом первого элемента И, второй вход которого подключен к выходу элемента НЕ, вы14748526

ход первого элемента И соединен с управляющим входом второго регистра и установочным входом второго счетчика, выход которого соединен с управляющим входом блока сравнения и установочным входом четвертого триггера, инверсный выход которого соединен с третьим входом первого элемента И, тактовым входом второго

10

15

20

счетчика, информационным входом четвертого триггера и вторым входом -второго элемента И, выход которого является вторым выходом декодера, выход генератора тактовых импульсов соединен с тактовыми входами первого, второго регистров, блока сравнения и первого счетчика, выходы которого соединены с соответствующими первыми информационными входами блока сравнения и информационными входами второго регистра, выходы которо го соединены с соответствующими вторыми информационными входами блока сравнения, выход которого соединен с вторым входом элемента ИЛИ.

ход первого элемента И соединен с управляющим входом второго регистра и установочным входом второго счетчика, выход которого соединен с управляющим входом блока сравнения и установочным входом четвертого триггера, инверсный выход которого соединен с третьим входом первого элемента И, тактовым входом второго

5

0

счетчика, информационным входом четвертого триггера и вторым входом -второго элемента И, выход которого является вторым выходом декодера, выход генератора тактовых импульсов соединен с тактовыми входами первого, второго регистров, блока сравнения и первого счетчика, выходы которого соединены с соответствующими первыми информационными входами блока сравнения и информационными входами второго регистра, выходы которого соединены с соответствующими вторыми информационными входами блока сравнения, выход которого соединен с вторым входом элемента ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Система передачи цифровой информации | 1990 |

|

SU1786679A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ДВОИЧНОЙ ИНФОРМАЦИИ | 1991 |

|

RU2022479C1 |

| Способ маркирования информационных комбинаций в системах последовательной записи с двухчастотным кодированием и устройства записи и воспроизведения для его осуществления | 1987 |

|

SU1543445A1 |

| Адаптивное устройство декодирования кода Манчестер | 1988 |

|

SU1640826A1 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 2001 |

|

RU2202121C2 |

| Контроллер станции локальной сети | 1988 |

|

SU1647590A1 |

| Дельта-кодек | 1987 |

|

SU1427572A1 |

| УСТРОЙСТВО ДИСТАНЦИОННОЙ СИГНАЛИЗАЦИИ | 1992 |

|

RU2032229C1 |

| Устройство для измерения отклонения частоты от номинального значения | 1984 |

|

SU1322450A1 |

| Устройство для формирования пачек импульсов | 1991 |

|

SU1812617A1 |

Изобретение относится к электросвязи, вычислительной технике и может использоваться в цифровых системах передачи данных в коде "Манчестер-2". Декодер автоматически подстраивается к тактовой частоте входного сигнала, что обеспечивает расширение функциональных возможносте декодера. Декодер имеет вход 1, триггеры 2,5,6,10, элемент 3 НЕ, элементы 4,15 И, выходы 7,18, блок 8 дифференцирования, элемент 9 ИЛИ, счетчики 11,14, регистры 12,17, блок 13 сравнения и генератор 16 тактовых импульсов. 3 ил.

ЯНллЯЯЯ г

i I «-I 0

Ш

I . I

tim

t 9

t ж 3

к

4

.V/ itf

г

| Преобразователь биимпульсного двоичного сигнала в бинарный сигнал | 1983 |

|

SU1200426A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Декодер | 1984 |

|

SU1236615A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-04-23—Публикация

1987-07-21—Подача