Ј -4

ОО Ю

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1985 |

|

SU1282117A1 |

| Устройство для деления чисел | 1985 |

|

SU1429109A1 |

| Устройство для деления | 1990 |

|

SU1803913A1 |

| Устройство для деления чисел | 1988 |

|

SU1580353A1 |

| Устройство для деления чисел | 1985 |

|

SU1247862A1 |

| Устройство для деления | 1984 |

|

SU1249551A1 |

| Устройство для деления | 1988 |

|

SU1520510A1 |

| Устройство для деления чисел | 1990 |

|

SU1735844A1 |

| Устройство для деления чисел | 1986 |

|

SU1417010A1 |

| Устройство для деления | 1990 |

|

SU1783522A1 |

Изобретение относится к вычислительной технике и может быть использовано для быстродействующих арифметических устройств для выполнения операции деления чисел. Цель изобретения - сокращение объема оборудования, необходимого для реализации устройства. Устройство для деления содержит регистры 1, 2 остатка, регистр 3 делителя, сумматор 4 частного, блок 5 деления усеченных чисел, компараторы 6, 11, блок 7 умножения, вычитатель 8, сумматор 9, элемент ИЛИ 10, блок 12 управления с соответствующими связями. 3 ил.

Шиг.1

Изобретение относится к вычислительной технике и может быть использовано для быстродействующих арифметических устройств для выполнения операции деления чисел.

Цель изобретения - сокращение объема оборудования, необходимого для реализации устройства.

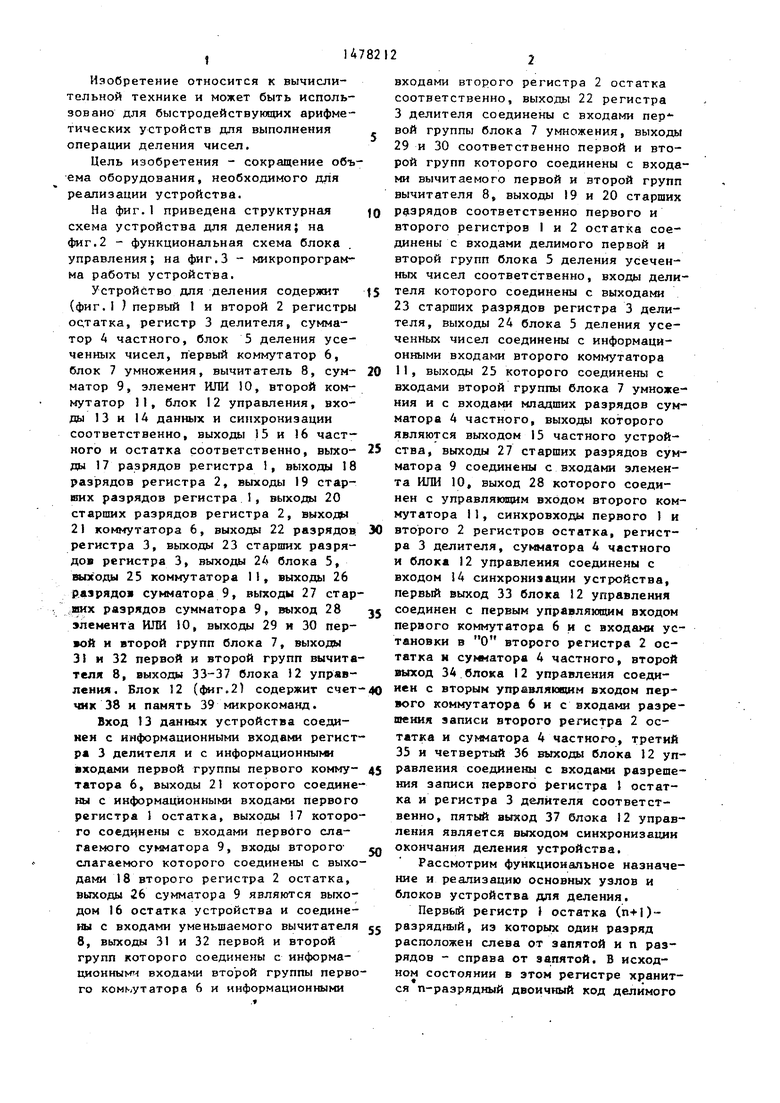

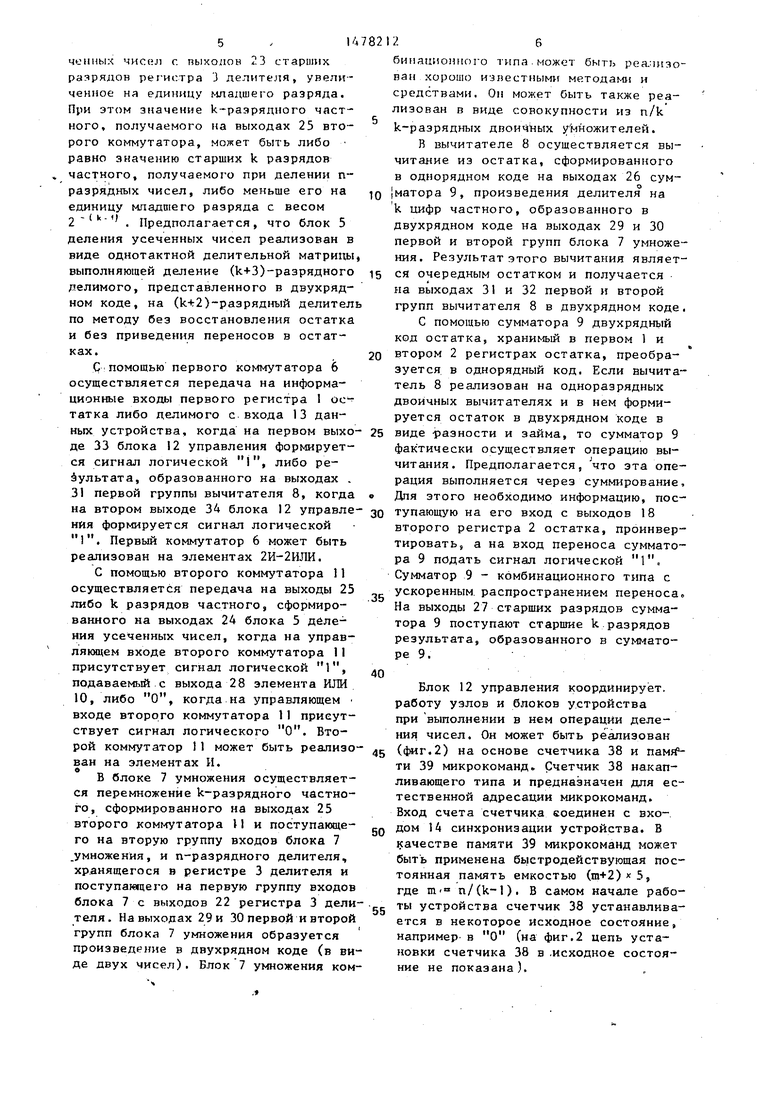

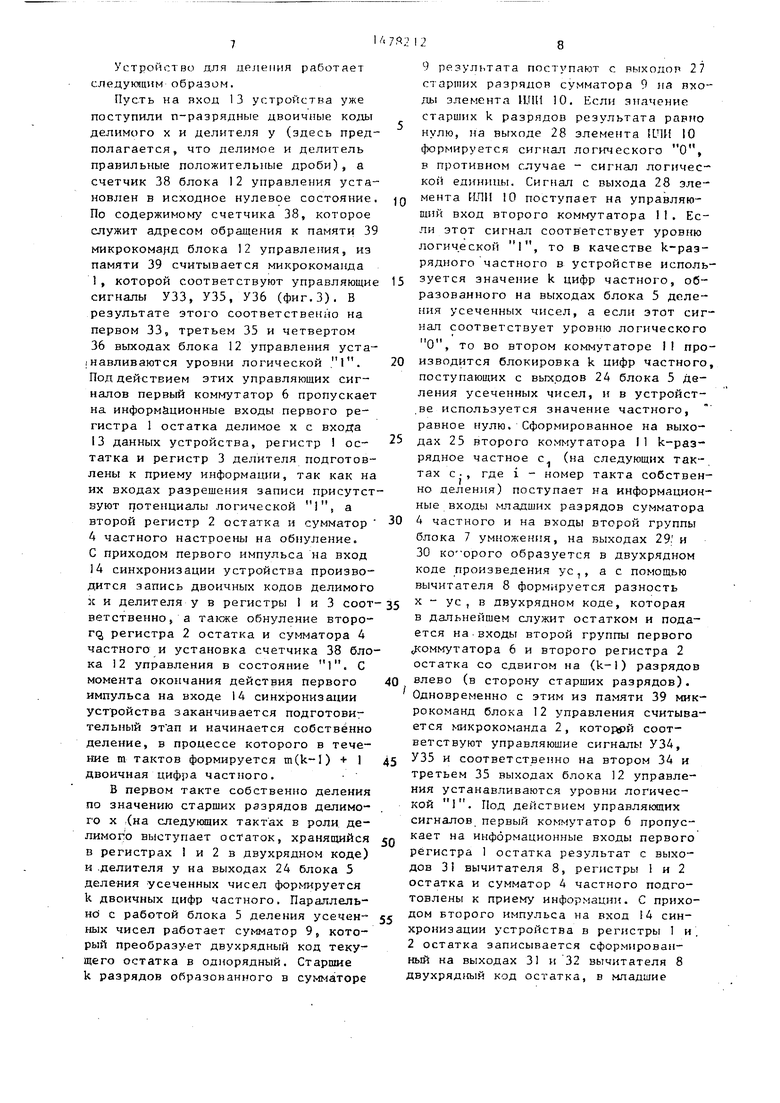

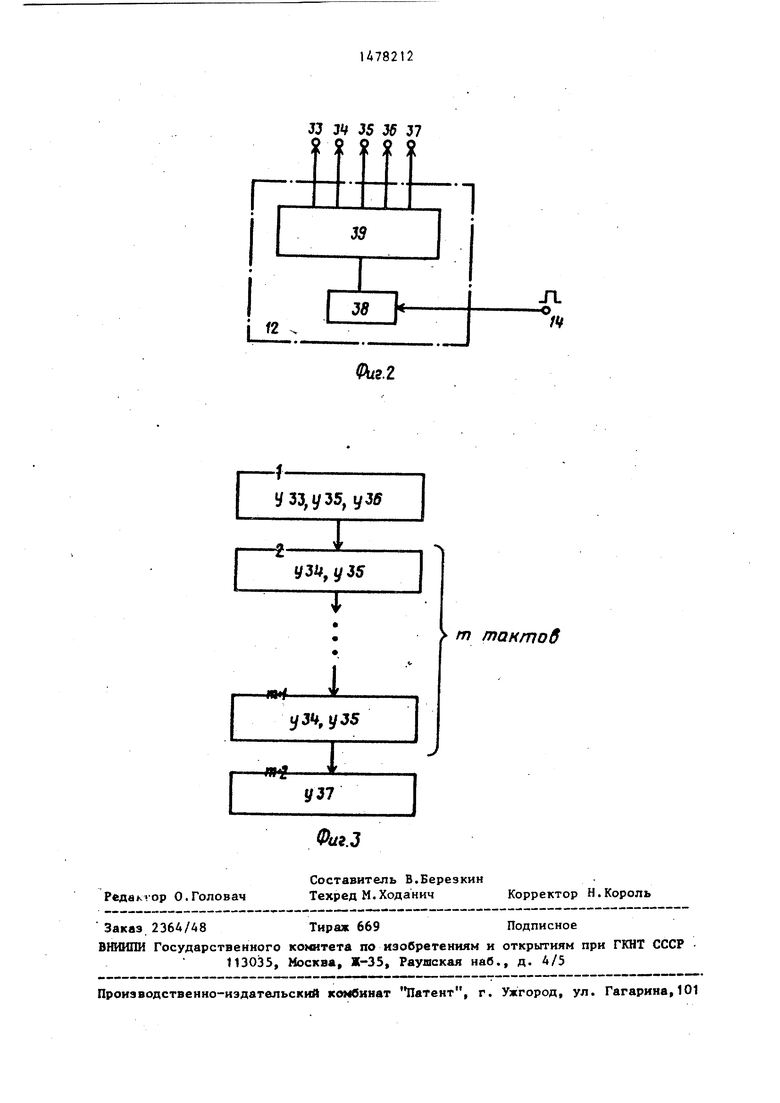

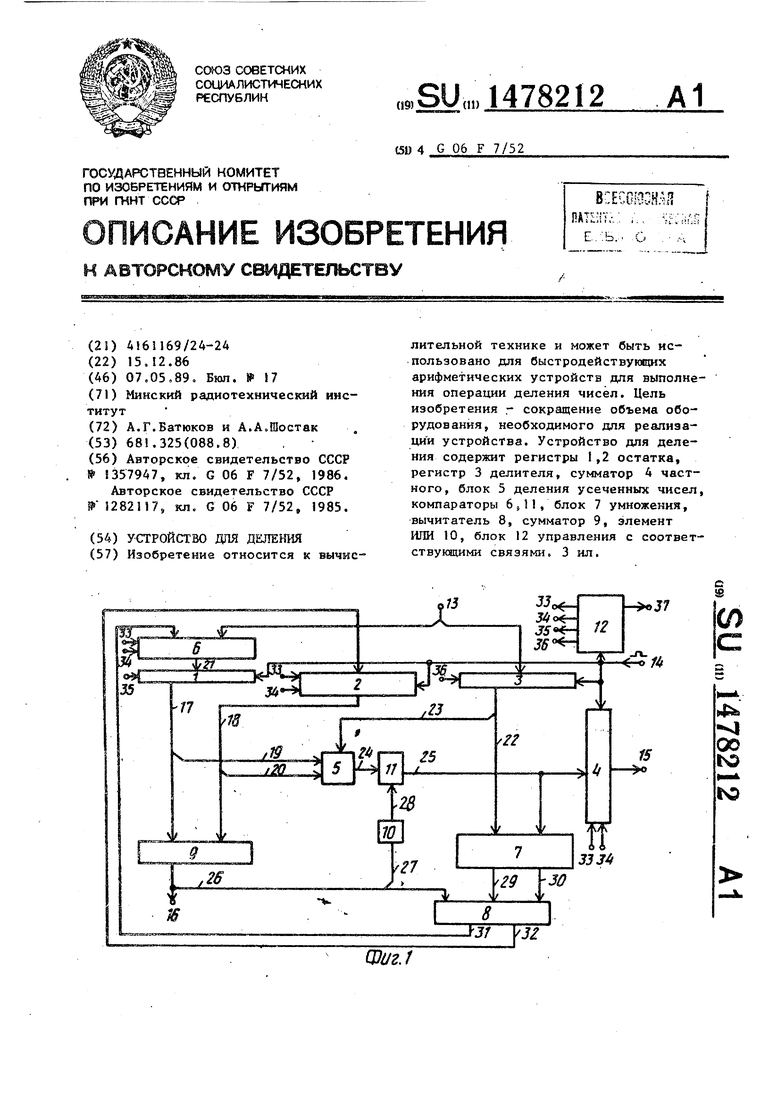

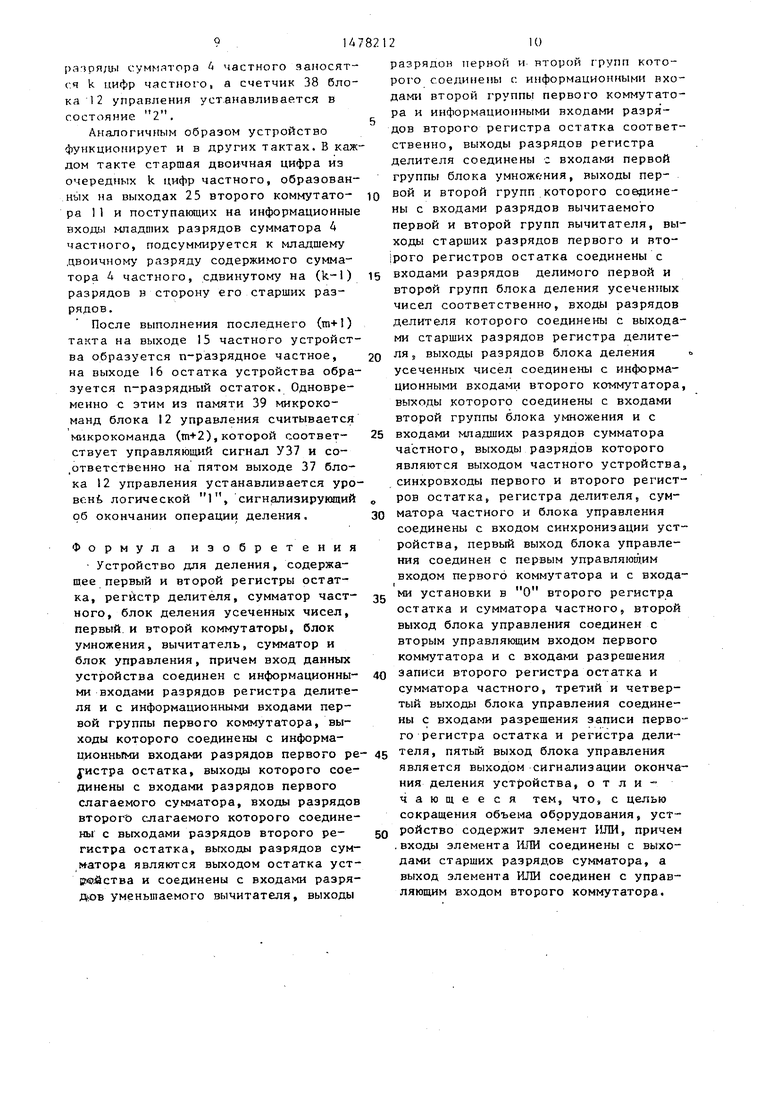

На фиг.1 приведена структурная схема устройства для деления; на фиг.2 - функциональная схема блока управления; на фиг.З - микропрограмма работы устройства.

Устройство для деления содержит (фиг.1 ) первый 1 и второй 2 регистры остатка, регистр 3 делителя, сумматор 4 частного, блок 5 деления усеченных чисел, первый коммутатор 6, блок 7 умножения, вычитатель 8, сум- матор 9, элемент ИЛИ 10, второй коммутатор 11, блок 12 управления, входы 13 и 14 данных и синхронизации соответственно, выходы 5 и 16 частного и остатка соответственно, выхо- ды 17 разрядов регистра 1, выходы 18 разрядов регистра 2, выходы 19 старших разрядов регистра 1, выходы 20 старших разрядов регистра 2, выходы 21 коммутатора 6, выходы 22 разрядов регистра 3, выходы 23 старших разрядов регистра 3, выходы 24 блока 5, выходы 25 коммутатора 11, выходы 26 разрядов сумматора 9, выходы 27 стар- лих разрядов сумматора 9, выход 28 элемента ИЛИ 10, выходы 29 и 30 первой и второй групп блока 7, выходы 31 и 32 первой и второй групп вычита- теля 8, выходы 33-37 блока 12 управления. Блок 32 (фиг.2) содержит счет чих 38 и память 39 микрокоманд.

Вход 13 данных устройства соединен с информационными входами регистра 3 делителя и с информационными входами первой группы первого комму- татора 6, выходы 21 которого соединены с информационными входами первого регистра 1 остатка, выходы 7 которого соединены с входами первого слагаемого сумматора 9, входы второго слагаемого которого соединены с выходами 18 второго регистра 2 остатка, выходы 26 сумматора 9 являются выходом 16 остатка устройства и соединены с входами уменьшаемого вычитателя 8, выходы 31 и 32 первой и второй групп которого соединены с информационными входами второй группы первого коммутатора 6 и информационными

входами второго регистра 2 остатка соответственно, выходы 22 регистра 3 делителя соединены с входами пер4- вой группы блока 7 умножения, выходы 29 и 30 соответственно первой и второй групп которого соединены с входами вычитаемого первой и второй групп вычитателя 8, выходы 19 и 20 старших разрядов соответственно первого и второго регистров 1 и 2 остатка соединены с входами делимого первой и второй групп блока 5 деления усеченных чисел соответственно, входы делителя которого соединены с выходами 23 старших разрядов регистра 3 делителя, выходы 24 блока 5 деления усеченных чисел соединены с информационными входами второго коммутатора 11, выходы 25 которого соединены с входами второй группы блока 7 умножения и с входами младших разрядов сумматора 4 частного, выходы которого являются выходом 15 частного устройства, выходы 27 старших разрядов сумматора 9 соединены с входами элемента ИЛИ 10, выход 28 которого соединен с управляющим входом второго коммутатора 11, синхровходы первого 1 и второго 2 регистров остатка, регистра 3 делителя, сумматора 4 частного и блока 12 управления соединены с входом 14 синхронизации устройства, первый выход 33 блока 2 управления соединен с первым управляющим входом первого коммутатора бис входами установки в О второго регистра 2 остатка м сумматоре 4 частного, второй выход 34 блока 12 управления соединен с вторым управляющим входом первого коммутатора бис входами разрешения записи второго регистра 2 остатка и сумматора 4 частного, третий 35 и четвертый 36 выходы блока 12 управления соединены с входами разрешения записи первого регистра 1 остатка и регистра 3 делителя соответственно, пятый выход 37 блока 12 управления является выходом синхронизации окончания деления устройства.

Рассмотрим функциональное назначение и реализацию основных узлов и блоков устройства для деления.

Первый регистр I остатка (п-Н)- разрядный, из которых один разряд расположен слева от запятой и п разрядов - справа от запятой. В исходном состоянии в этом регистре хранится п-раэрядный двоичный код делимого

без знака, а в процессе деления в него записываются значения сумм очередных остатков, формируемых в устройстве, в двухрядном коде (в виде двух чисел: первое число является поразрядной суммой, а второе - его поразрядными переносами). Второй регистр 2 остатка содержит п разрядов, из которых один расположен слева от запятой, а остальные - справа. В исходном состоянии этот регистр обнулен. Регистр 3 делителя n-раэрядный, причем все разряды расположены справа от запятой. В регистре 3 делителя в исходном состоянии хранится п-раэряд- ный двоичный код делителя без знака. Предполагается что регистры реализованы на основе двухтактных синхронных DV-триггеров. Запись информации в регистры производится по синхроимпульсу при наличии разрешающего потенциала иа их V-входах.

Сумматор 4 частного предназначен для хранения частного и участвует в процессе формирования правильного значения частного. В первом такте деления сумматор 4 частного обнуляется путем подачи импульса с входа 14 синхронизации устройства на его синхро- входы и разрешающего потенциала с первого выхода 33 блока 12 управления на вход разрешения установки в О сумматора 4 частного. Во всех других тактах работы устройства в сумматоре 4-частного накапливается значение частного. Для этого к значению частного, сформированному на предыдущих тактах работы устройства и сдвинутому на (k-1) разряд влево (в сторону старших разрядов), прибавляется значение k цифр частного, сформированных на выходах. 25 второго коммутатора 11 в текущем такте. Запись результата этого суммирования в сумматор 4 частного производится по синхроимпульсу при наличии разрешающего потенциала на входе разрешения записи, который подключен к второму входу 34 блока 12 управления. После завершения деления образованное в сумматоре 4 частное поступает на выход 15 частного устройства. Предполагается t что сумматор 4 частного реализован на основе комбинационного сумматора и регистра.

Формирование k цифр частного на каждом такте работы устройства производится путем деления значения стар0

5

0

5

ших разрядов непрнрр-дечного остатке на значение старших разрядов делителя, увеличенное на единицу младшего разряда. Увеличение значения старших разрядов делителя на единицу младшего разряда устраняет возможность получения в устройстве k цифр частноге г. избытком. Так как в предлагаемом устройстве при формирования k цифр частного используются только старшие разряды остатка, не приведенного к однорядному коду, то становится возможным образование неправильного значения k цифр частного. Так, если значение старших разрядов приведенного остатка, полученного на выходах 26 сумматора 9, равно нулю, то значение старших разрядов остатка на выходах 19 и 20 старших разрядов первого 1 и второго 2 регистров остатка может быть меньше, чем нуль на единицу младшего разряда, т.е. значение

1

1 1

где

количество стар1

0

5

0

5

0

5

ших разрядов остатка, участвующих в формировании k цифр частного. Для исключения возможности получения в этом -случае неверного значения k цифр частного в устройстве предусмотрена блокировка (Формирование значения k цифр частного, равного нулю) цифр частного, полученных на выходах 24 блока 5 деления усеченных чисел, чПутем подачи на управляющий вход второго коммутатора i1 уровня логического О с выхода 28 элемента ИЛИ 10, Уровень логического О на его выходе 28 устанавливается в том случае, если значение k старших разрядов однорядного кода остатка, полученного на выходах 27 старших разрядов сумма- ,тора 9, равно нулю. Во всех других случаях на выходы 25 второго коммутатора 1 i пропускается значение k цифр частного с выходов 24 блока 5 деления усеченных чисел.

В блоке 5 деления усеченных чисел производится деление значения старших (k+З) разрядов неприведенного остатка, поступающего на входы делимого первой и второй групп блока 5 деления усеченных чисел с выходов 19 и 20 старших разрядов первого 1 и второго 2 регистров остатка соответственно, на значение старших (k+2) разрядов делителя, поступающего на входы делителя блока 5 деления усе5 , 14 ченных чисел г пыхолов 23 старших разрядов регистра 3 делителя, увеличенное на единицу младшего разряда. При этом значение k-раэрядного частного, получаемого на выходах 25 второго коммутатора, может быть либо равно значению старших k разрядов частного, получаемого при делении п разрядных чисел, либо меньше его на единицу младшего разряда с весом . Предполагается, что блок 5 деления усеченных чисел реализован в виде однотактной делительной матрицы, выполняющей деление (К+3)-разрядного делимого, представленного в двухрядном коде, на +2)разрядный делитель по методу без восстановления остатка и без приведения переносов в остатках.

С помощью первого коммутатора 6 осуществляется передача на информационные входы первого регистра 1 остатка либо делимого с входа 13 данных устройства, когда на первом выхо- де 33 блока 12 управления формируется сигнал логической I, либо результата, образованного на выходах . 31 первой группы вычитателя 8, когда на втором выходе 34 блока 12 управле- ния формируется сигнал логической . Первый коммутатор 6 может быть реализован на элементах 2И-2ИЛИ.

С помощью второго коммутатора 11 осуществляется передача на выходы 25 либо k разрядов частного, сформированного на выходах 24 блока 5 деления усеченных чисел, когда на управляющем входе второго коммутатора 11 присутствует сигнал логической 1, подаваемый с выхода 28 элемента ИЛИ 10, либо О, когда на управляющем входе второго коммутатора 11 присутствует сигнал логического О. Второй коммутатор 11 может быть реалиэо ван на элементах И.

ф

В блоке 7 умножения осуществляется перемножение k-разрядного частного, сформированного на выходах 25 второго коммутатора И и поступающего на вторую группу входов блока 7 .умножения, и n-разрядного делителя, хранящегося в регистре 3 делителя и поступающего на первую группу входов блока 7 с выходов 22 регистра 3 делителя. На выходах 29 и 30 первой и второй групп блока 7 умножения образуется произведение в двухрядном коде (в виде двух чисел). Блок 7 умножения ком

Q 5 0

5 о

д с

5

50

55

I6

бинационпого типа может быть реашчо- ван хорошо изпестными методами и средствами. Он может быть также реализован в виде совокупности из n/k k-раэрядных двоичных Умножителей.

В вычитателе 8 осуществляется вычитание из остатка, сформированного в однорядном коде на выходах 26 сум- (матора 9, произведения делителя на k цифр частного, образованного в двухрядном коде на выходах 29 и 30 первой и второй групп блока 7 умножения. Результат этого вычитания является очередным остатком и получается на выходах 31 и 32 первой и второй групп вычитателя 8 в двухрядном коде.

С помощью сумматора 9 двухрядный код остатка, хранимый в первом 1 и втором 2 регистрах остатка, преобразуется в однорядный код. Если вычита- тель 8 реализован на одноразрядных двоичных вычитателях и в нем формируется остаток в двухрядном коде в виде -разности и займа, то сумматор 9 фактически осуществляет операцию вычитания. Предполагается, что эта операция выполняется через суммирование, Для этого необходимо информацию, поступающую на его вход с выходов 18 второго регистра 2 остатка, проинвер- тировать, а на вход переноса сумматора 9 подать сигнал логической 1. Сумматор 9 - комбинационного типа с ускоренным распространением переноса. На выходы 27 старших разрядов сумматора 9 поступают старшие k разрядов результата, образованного в сумматоре 9.

Блок 12 управления координирует, работу узлов и блоков устройства при выполнении в нем операции деления чисел. Он может быть реализован (фиг.2) на основе счетчика 38 и памя3- ти 39 микрокоманд. Счетчик 38 накапливающего типа и предназначен для естественной адресации микрокоманд. Вход счета счетчика еоединен с входом 14 синхронизации устройства. В качестве памяти 39 микрокоманд может быть применена быстродействующая постоянная память емкостью (т+2)х5, где n/(k-l), В самом начале работы устройства счетчик 38 устанавливается в некоторое исходное состояние, например в О (на фиг.2 цепь установки счетчика 38 в .исходное состояние не показана).

Устройство для деления работает следующим образом.

Пусть на вход 13 устройства уже поступили п-раэрядные двоичные коды делимого х и делителя у (здесь предполагается, что делимое и делитель правильные положительные дроби), а счетчик 38 блока 12 управления установлен в исходное нулевое состояние. По содержимому счетчика 38, которое служит адресом обращения к памяти 39 микрокоманд блока 12 управления, из памяти 39 считывается микрокоманда 1, которой соответствуют управляющие сигналы УЗЗ, У35, У36 (фиг.З). В результате этого соответственно на первом 33, третьем 35 и четвертом 36 выходах блока 12 управления устанавливаются уровни логической 1. Под действием этих управляющих сигналов первый коммутатор 6 пропускает на информационные входы первого регистра 1 остатка делимое х с входа

13данных устройства, регистр остатка и регистр 3 делителя подготовлены к приему информации, так как на их входах разрешения записи присутствуют потенциалы логической , а второй регистр 2 остатка и сумматор 4 частного настроены на обнуление.

С приходом первого импульса на вход

14синхронизации устройства производится запись двоичных кодов делимого х и делителя у в регистры 1 и 3 соот ветственно, а также обнуление второ- rq регистра 2 остатка и сумматора 4 частного и установка счетчика 38 блока 12 управления в состояние 1. С момента окончания действия первого импульса на входе 14 синхронизации устройства заканчивается подготовительный эт ап и начинается собственно деление, в процессе которого в течение m тактов формируется m(k-l) + I двоичная цифра частного,

В первом такте собственно деления по значению старших разрядов делимого х (на следующих тактах в роли делимого выступает остаток, хранящийся в регистрах 1 и 2 в двухрядном коде) и делителя у на выходах 24 блока 5 деления усеченных чисел формируется k двоичных цифр частного. Параллельно с работой блока 5 деления усечен™ ных чисел работает сумматор 9, который преобразует двухрядный код текущего остатка в однорядный. Старшие k разрядов образованного в сумматоре

10

15

20

25

30

35

40

45

50

55

9 результата поступают с выходов 27 старших разрядов сумматора 9 на входы элемента ИЛИ 10. Если значение старших k разрядов результата равно нулю, на выходе 28 элемента (ПИ 10 формируется сигнал логического О, в противном случае - сигнал логической единицы. Сигнал с выхода 28 элемента ИЛИ 10 поступает на управляющий вход второго коммутатора 11. Если этот сигнал соответствует уровню логической 1, то в качестве k-раэ- рядного частного в устройстве используется значение k цифр частного, образованного на выходах блока 5 деления усеченных чисел, а если этот сигнал соответствует уровню логического О, то во втором коммутаторе 11 производится блокировка k цифр частного, поступающих с выходов 24 блока 5 деления усеченных чисел, и в устройстве используется значение частного, равное нулю. Сформированное на выходах 25 второго коммутатора II k-раз- рядное частное с (на следующих тактах с , где i - номер такта собственно деления) поступает на информационные входы младших разрядов сумматора 4 частного и на входы второй группы блока 7 умножения, на выходах 29 и 30 ко орого образуется в двухрядном коде произведения ус,, а с помощью вычитателя 8 формируется разность х - ус , в двухрядном коде, которая в дапьненшем служит остатком и подается на входы второй группы первого коммутатора 6 и второго регистра 2 остатка со сдвигом на (k-1) разрядов влево (в сторону старших разрядов). Одновременно с этим из памяти 39 микрокоманд блока 12 управления считывается микрокоманда 2, которой соответствуют управляющие сигналы У34, УЗЗ и соответственно на втором 34 и третьем 35 выходах блока 12 управления устанавливаются уровни логической 1. Под действием управляющих сигналов первый коммутатор 6 пропускает на информационные входы первого регистра 1 остатка результат с выходов 31 вычитателя 8, регистры 1 и 2 остатка и сумматор 4 частного подготовлены к приему информации. С приходом второго импульса на вход 14 синхронизации устройства в регистры 1 и, 2 остатка записывается сформированный на выходах 31 и 32 вычитателя 8 двухрядный код остатка, в младшие

pa то яды (. уммятора 4 частного заносятся k цифр частного, а счетчик 38 блока 12 управления устанавливается в состояние 2.

Аналогичным образом устройство функционирует и в других тактах. В каждом такте старшая двоичная цифра из очередных k цифр частного, образованных на выходах 25 второго коммутатора 1 1 и поступающих на информационные входы младших разрядов сумматора А частного, подсуммируется к младшему двоичному разряду содержимого сумматора 4 частного, сдвинутому на (k-1) разрядов в сторону его старших разрядов.

После выполнения последнего (тп+1) такта на выходе 15 частного устройства образуется n-разрядное частное, на выходе 16 остатка устройства образуется n-разрядный остаток. Одновременно с этим из памяти 39 микрокоманд блока 12 управления считывается микрокоманда (т+2), которой соответствует управляющий сигнал У37 и со- .ответственно на пятом выходе 37 блока 12 управления устанавливается уровень логической 1, сигнализирующий об окончании операции деления.

Формула изобретения

Устройство для деления, содержа- шее первый и второй регистры остатка, регистр делителя, сумматор частного, блок деления усеченных чисел, первый и второй коммутаторы, блок умножения, вычитатель, сумматор и блок управления, причем вход данных устройства соединен с информационными входами разрядов регистра делителя и с информационными входами первой группы первого коммутатора, выходы которого соединены с информационными входами разрядов первого ре- уистра остатка, выходы которого соединены с входами разрядов первого слагаемого сумматора, входы разрядов второго слагаемого которого соединены с выходами разрядов второго регистра остатка, выходы разрядов сумматора являются выходом остатка устройства и соединены с входами разрядов уменьшаемого вычитателя, выходы

разрядов первой и второй групп которого соединены с информационными входами второй группы первого коммутатора и информационными входами разрядов второго регистра остатка соответственно, выходы разрядов регистра делителя соединены ; входами первой группы блока умножения, выходы пер- вой и второй групп которого соединены с входами разрядов вычитаемого первой и второй групп вычитателя, выходы старших разрядов первого и вто- ,рого регистров остатка соединены с 5 входами разрядов делимого первой и второй групп блока деления усеченных чисел соответственно, входы разрядов делителя которого соединены с выходами старших разрядов регистра делите- ля, выходы разрядов блока деления « усеченных чисел соединены с информационными входами второго коммутатора, выходы которого соединены с входами второй группы блока умножения и с 5 входами младших разрядов сумматора частного, выходы разрядов которого являются выходом частного устройства, синхровходы первого и второго регист- ров остатка, регистра делителяs сум- 0 матора частного и блока управления соединены с входом синхронизации устройства, первый выход блока управления соединен с первым управляющим входом первого коммутатора и с входа- 5 ми установки в О второго регистра остатка и сумматора частного, второй выход блока управления соединен с вторым управляющим входом первого коммутатора и с входа и разрешения 0 записи второго регистра остатка и сумматора частного, третий и четвертый выходы блока управления соединены с входами разрешения записи первого регистра остатка и регистра дели- 5 теля, пятый выход блока управления является выходом сигнализации окончания деления устройства, отличающееся тек, что, с целью сокращения объема оборудования, уст- 0 ройство содержит элемент ИЛИ, причем .входы элемента ИЛИ соединены с выходами старших разрядов сумматора, а выход элемента ИЛИ соединен с управляющим входом второго коммутатора.

12

I J0

«/33,1/35, у 36

Ј1

УЫ,у35

-т.

I

«/J1, у J5

--J.

i

tif

JL

т тан то б

| Устройство для деления | 1986 |

|

SU1357947A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для деления | 1985 |

|

SU1282117A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-05-07—Публикация

1986-12-15—Подача