§

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для локализации неисправностей | 1980 |

|

SU903888A1 |

| Устройство для фиксации неустойчивых сбоев | 1985 |

|

SU1277117A1 |

| Устройство для тестового контроля цифровых вычислительных машин | 1981 |

|

SU964647A1 |

| Устройство для контроля цифровых узлов | 1982 |

|

SU1059576A1 |

| Устройство для контроля и диагностики логических блоков | 1985 |

|

SU1302284A1 |

| Устройство для контроля хода программы | 1988 |

|

SU1663612A1 |

| Устройство для фиксации неустойчивых сбоев | 1986 |

|

SU1388872A2 |

| Логическое запоминающее устройство | 1981 |

|

SU1014036A1 |

| Устройство для контроля цифровых систем | 1983 |

|

SU1130871A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

Изобретение относится к вычислительной технике. Цель изобретения - расширение функциональных возможностей устройства за счет выборочной проверки отдельных бит контролируемой последовательности. Устройство содержит регистр 1 сдвига, коммутатор 2, элемент 3 сравнения, триггер 4, элемент И 5, счетчики 6, 7, блок 8 индикации, регистр 14, коммутатор 15, элемент И-НЕ 16 и имеет информационный вход 9, вход 10 синхронизации, установочный вход 11, выход 12 ошибки, вход 13 маски. Устройство позволяет осуществлять выборочную проверку отдельных бит контролируемой последовательности за счет маскирования результата контроля для определенных бит. Положительный эффект достигается за счет введения второго коммутатора и элемента И-НЕ с соответствующими связями. 1 ил.

NU

00

vj

ю

Изобретение относится к вычислительной технике.

Цель изобретения - расширение функциональных возможностей устройства за счет выборочной проверки отдельных бит контро- лируемой последовательности.

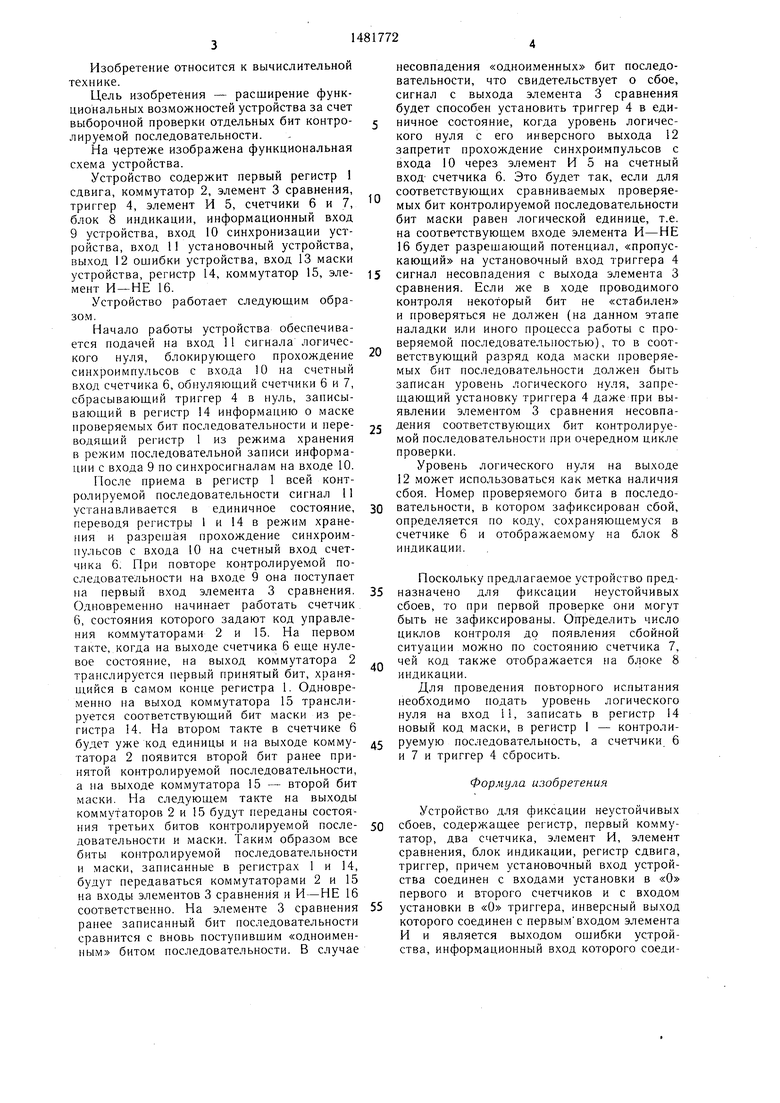

На чертеже изображена функциональная схема устройства.

Устройство содержит первый регистр 1 сдвига, коммутатор 2, элемент 3 сравнения, триггер 4, элемент И 5, счетчики 6 и 7, блок 8 индикации, информационный вход 9 устройства, вход 10 синхронизации устройства, вход 11 установочный устройства, выход 12 ошибки устройства, вход 13 маски устройства, регистр 14, коммутатор 15, эле- мент И - НЕ 16.

Устройство работает следующим образом.

Начало работы устройства обеспечивается подачей на вход 11 сигнала логического нуля, блокирующего прохождение синхроимпульсов с входа 10 на счетный вход счетчика 6, обнуляющий счетчики 6 и 7, сбрасывающий триггер 4 в нуль, записывающий в регистр 14 информацию о маске проверяемых бит последовательности и пере- водящий регистр 1 из режима хранения в режим последовательной записи информации с входа 9 по синхросигналам на входе 10.

После приема в регистр 1 всей контролируемой последовательности сигнал 11 устанавливается в единичное состояние, переводя регистры 1 и 14 в режим хранения и разрешая прохождение синхроимпульсов с входа 10 на счетный вход счетчика 6. При повторе контролируемой последовательности на входе 9 она поступает на первый вход элемента 3 сравнения. Одновременно начинает работать счетчик 6, состояния которого задают код управления коммутаторами 2 и 15. На первом такте, когда на выходе счетчика 6 еще нулевое состояние, на выход коммутатора 2 транслируется первый принятый бит, хранящийся в самом конце регистра 1. Одновременно на выход коммутатора 15 транслируется соответствующий бит маски из регистра 14. На втором такте в счетчике 6 будет уже код единицы и на выходе комму- татора 2 появится второй бит ранее принятой контролируемой последовательности, а на выходе коммутатора 15 - второй бит маски. На следующем такте на выходы коммутаторов 2 и 15 будут переданы состояния третьих битов контролируемой после- довательности и маски. Таким образом все биты контролируемой последовательности и маски, записанные в регистрах 1 и 14, будут передаваться коммутаторами 2 и 15 на входы элементов 3 сравнения и И-НЕ 16 соответственно. На элементе 3 сравнения ранее записанный бит последовательности сравнится с вновь поступившим «одноименным битом последовательности. В случае

несовпадения «одноименных бит последовательности, что свидетельствует о сбое, сигнал с выхода элемента 3 сравнения будет способен установить триггер 4 в единичное состояние, когда уровень логического нуля с его инверсного выхода 12 запретит прохождение синхроимпульсов с входа 10 через элемент И 5 на счетный вход счетчика 6. Это будет так, если для соответствующих сравниваемых проверяемых бит контролируемой последовательности бит маски равен логической единице, т.е. на соответствующем входе элемента И-НЕ 16 будет разрешающий потенциал, «пропускающий на установочный вход триггера 4 сигнал несовпадения с выхода элемента 3 сравнения. Если же в ходе проводимого контроля некоторый бит не «стабилен и проверяться не должен (на данном этапе наладки или иного процесса работы с проверяемой последовательностью), то в соответствующий разряд кода маски проверяемых бит последовательности должен быть записан уровень логического нуля, запрещающий установку триггера 4 даже при выявлении элементом 3 сравнения несовпадения соответствующих бит контролируемой последовательности при очередном цикле проверки.

Уровень логического нуля на выходе 12 может использоваться как метка наличия сбоя. Номер проверяемого бита в последовательности, в котором зафиксирован сбой, определяется по коду, сохраняющемуся в счетчике 6 и отображаемому на блок 8 индикации.

Поскольку предлагаемое устройство предназначено для фиксации неустойчивых сбоев, то при первой проверке они могут быть не зафиксированы. Определить число циклов контроля до появления сбойной ситуации можно по состоянию счетчика 7, чей код также отображается на блоке 8 индикации.

Для проведения повторного испытания необходимо подать уровень логического нуля на вход 11, записать в регистр 14 новый код маски, в регистр 1 - контролируемую последовательность, а счетчики 6 и 7 и триггер 4 сбросить.

Формула изобретения

Устройство для фиксации неустойчивых сбоев, содержащее регистр, первый коммутатор, два счетчика, элемент И, элемент сравнения, блок индикации, регистр сдвига, триггер, причем установочный вход устройства соединен с входами установки в «О первого и второго счетчиков и с входом установки в «О триггера, инверсный выход которого соединен с первым входом элемента И и является выходом ошибки устройства, информационный вход которого соединен с информационным входом регистра сдвига и первым входом элемента сравнения, второй вход которого соединен с выходом первого коммутатора, управляющий вход которого объединен с первым информационным входом блока индикации и подключен к информационному выходу первого счетчика, выход переполнения которого соединен со счетным входом второго счетчика, информационный выход регистра сдвига соединен с информационным входом первого коммутатора, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет выборочной проверки отдельных бит контролируемой последовательности, в него введены второй коммутатор и элемент И-НЕ, причем вход синхронизации устройства соединен с вторым входом элемента И и тактовым входом

0

регистра сдвига, вход режима которого соединен с входом режима регистра, с третьим входом элемента И и подключен к установочному входу устройства, вход маски которого соединен с информационным входом регистра, выход которого соединен с информационным входом второго коммутатора, выход которого соединен с первым входом элемента И-НЕ, выход которого соединен с входом установки в «1 триггера, установочный вход второго коммутатора соединен с информационным выходом первого счетчика, информационный выход второго счетчика соединен с вторым информационным входом блока индикации, выход элемента И соединен со счетным входом первого счетчика, выход элемента сравнения соединен с вторым входом элемента И-НЕ.

| Устройство для фиксации неустойчивых сбоев | 1983 |

|

SU1126965A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для фиксации неустойчивых сбоев | 1985 |

|

SU1277117A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-05-23—Публикация

1987-10-14—Подача