I

Изобретение относится к вычислительной технике и может быть использовано при построении доменных запоминающих устройств.

Целью изобретения является повышение надежности за счет блокировки записи в маркерный регистр.

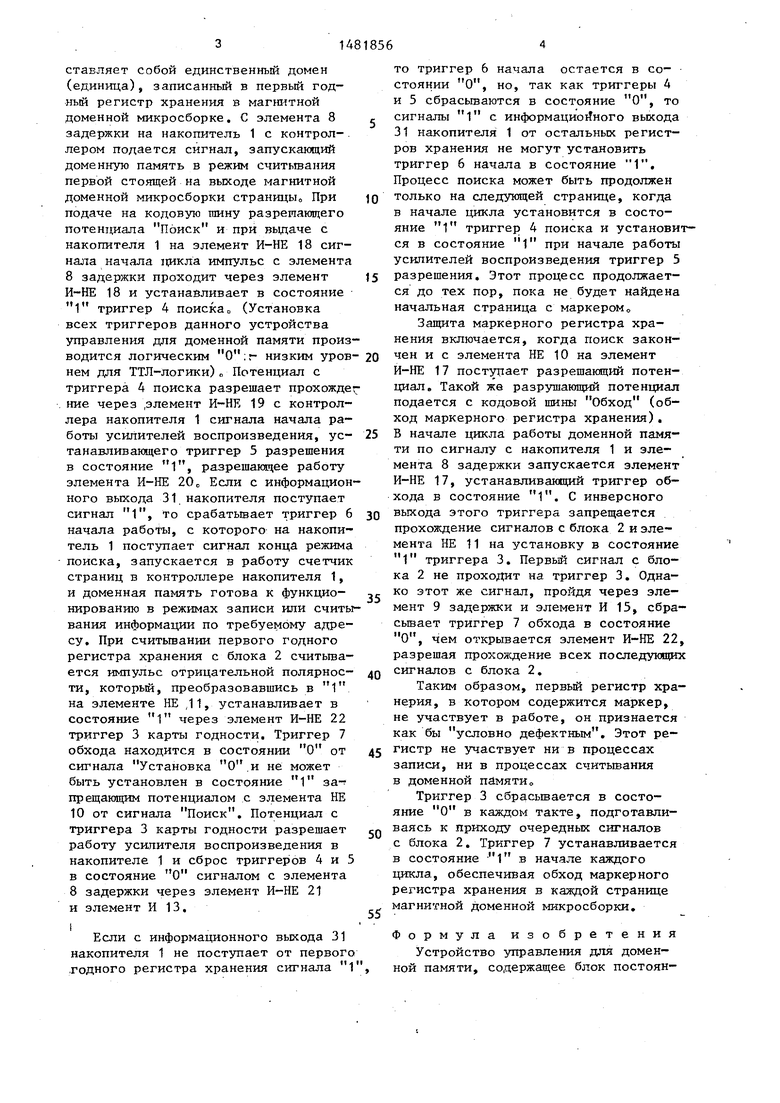

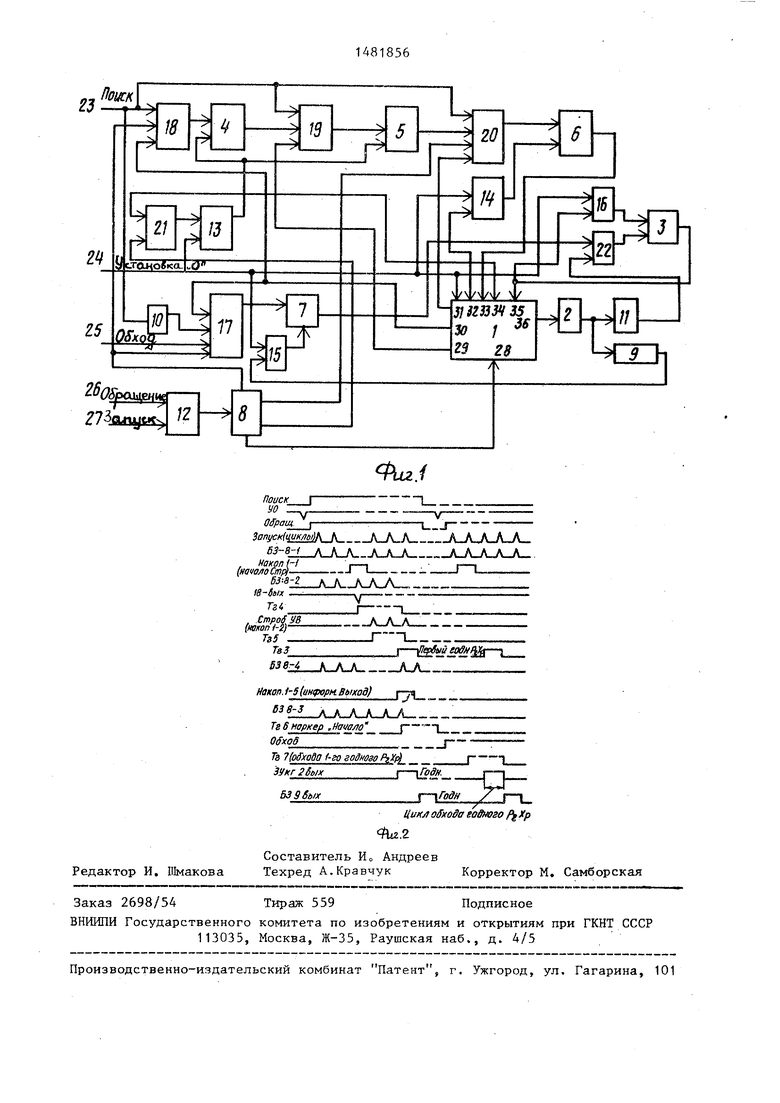

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 - временные диаграммы работы устройства

На схеме (фиг0 О обозначены блок 1 накопителя информации, блок 2 постоянной памяти, четвертый 3, первый 4, второй 5, третий 6 и пятый 7 триггеры, первый 8 и второй 9 элементы задержки, первый 10 и второй 11 элементы НЕ, первьй 12, второй 13, третий 14, четвертый 15 и пятый 16 элементы И, первьй 17, второй 18, пятый 19, третий 20, четвертый 21 и шестой 22 элементы И-НЕ, вхо(Л

ды 23-27 соответственно режима поиска, установки в ноль, признака режима Обход, обращения и запуска устройства, выход 28 запуска, входы 29- 32 соответственно строба считывания, начала первой страницы, информационный и переполнения счетчика страниц - устройства, выходы 33 конца поиска и 34 маски устройства, вход 35 сброса триггера маски и тактовый вход 36 устройства.

Устройство работает следующим образом.

L Накопитель 1 содержит контроллер, импульсы с него, управляющие доменной памятью, используются для работы устройства управления..

При обращении к доменной памяти по сигналам с кодовых шин Обращение и Запуск начинается поиск начальной страницы с маркером запуска элемента 8 задержки. Маркер предоо

оо ел

б

ставляет собой единственный домен (единица), записанный в первый годный регистр хранения в магнитной доменной микросборке. С элемента 8 задержки на накопитель 1 с контроллером подается сигнал, запускающий доменную память в режим считывания первой стоящей на выходе магнитной доменной микросборки страницы,, При подаче на кодовую шину разрешающего потенциала Поиск и при выдаче с накопителя 1 на элемент И-НЕ 18 сигнала начала никла импульс с элемента 8 задержки проходит через элемент И-НЕ 18 и устанавливает в состояние 1 триггер 4 поиска о (Установка всех триггеров данного устройства управления для доменной памяти производится логическим О. г- низким уров- нем для ТТЛ-логики)0 Потенциал с триггера 4 поиска разрешает прохожде; ние через .элемент И-НЕ 19 с контроллера накопителя 1 сигнала начала работы усилителей воспроизведения, ус- танавливающего триггер 5 разрешения в состояние 1, разрешающее работу элемента И-НЕ 20„ Если с информационного выхода 31 накопителя поступает сигнал 1, то срабатывает триггер 6 начала работы, с которого на накопитель 1 поступает сигнал конца режима поиска, запускается в работу счетчик страниц в контроллере накопителя 1, и доменная память готова к функцио- нированию в режимах записи или считывания информации по требуемому адресу. При считывании первого годного регистра хранения с блока 2 считывается импульс отрицательной полярное- ти, который, преобразовавшись в 1 на элементе НЕ ,11, устанавливает в состояние 1 через элемент И-НЕ 22 триггер 3 карты годности. Триггер 7 обхода находится в состоянии О от сигнала Установка О и не может быть установлен в состояние 1 запрещающим потенциалом с элемента НЕ 10 от сигнала Поиск. Потенциал с триггера 3 карты годности разрешает работу усилителя воспроизведения в накопителе 1 и сброс триггеров 4 и 5

8 задержки через элемент И-НЕ 21 и элемент И 13.

Если с информационного выхода 31 накопителя 1 не поступает от первого годного регистра хранения сигнала 1,

Q 5 0 5 0 о 5 Q

5

то триггер 6 начала остается в состоянии О, но, так как триггеры 4 и 5 сбрасываются в состояние О, то сигналы 1 с информационного выхода 31 накопителя 1 от остальных регистров хранения не могут установить триггер 6 начала в состояние 1. Процесс поиска может быть продолжен только на следующей странице, когда в начале цикла установится в состояние 1 триггер 4 поиска и установится в состояние 1 при начале работы усилителей воспроизведения триггер 5 разрешения. Этот процесс продолжается до тех пор, пока не будет найдена начальная страница с маркером

Защита маркерного регистра хранения включается, когда поиск закончен и с элемента НЕ 10 на элемент И-НЕ 17 поступает разрешающий потенциал. Такой же разрушающий потенциал подается с кодовой шины Обход (обход маркерного регистра хранения). В начале цикла работы доменной памяти по сигналу с накопителя 1 и элемента 8 задержки запускается элемент И-НЕ 17, устанавливающий триггер обхода в состояние 1. С инверсного выхода этого триггера запрещается прохождение сигналов с блока 2 и элемента НЕ 11 на установку в состояние 1 триггера 3. Первый сигнал с блока 2 не проходит на триггер 3. Однако этот же сигнал, пройдя через элемент 9 задержки и элемент И 15, сбрасывает триггер 7 обхода в состояние О, чем открывается элемент И-НЕ 22, разрешая прохоясдение всех последующих сигналов с блока 2.

Таким образом, первый регистр хра- нерия, в котором содержится маркер, не участвует в работе, он признается как бы условно дефектным. Этот регистр не участвует ни в процессах записи, ни в процессах считывания в доменной памяти0

Триггер 3 сбрасывается в состояние О в каждом такте, подготавливаясь к приходу очередных сигналов с блока 2. Триггер 7 устанавливается в состояние 1 в начале каждого цикла, обеспечивая обход маркерного регистра хранения в каждой странице магнитной доменной микросборки.

Формула изобретения

Устройство управления для доменной памяти, содержащее блок постоянной памяти, вход которого является тактовым входом устройства, триггеры с первого по третий, элементы И с первого по пятый, отличающейся тем, что, с целью повышения надежности устройства за счет блокировки записи в маркерный регистр, в него введены два элемента НЕ, два элемента задержки, четвертый и пятый триггеры, элементы И-НЕ с первого по шестой, причем первый и второй входы первого элемента И являются соответственно входами запуска и обращения устройства, выход первого элемента И соединен с входом первого элемента задержки, первый выход которого соединен с первыми входами первого и второго элементов И-НЕ, второй и третий выходы первого элемента задержки соединены соответственно с первыми входами третьего и четвертого элементов И-НЕ, четвертый выход первого элемента задержки является выходом запуска устройства, первый вход пятого элемента И-НЕ соединен с вторыми входами второго и третьего элементов И-НЕ, с входом режима поиска устройства и с входом первого элемента НЕ, выход которого соединен с вторым входом первого элемента И-НЕ, третий вход которого соединен с входом начала первой страницы устройства и с третьим входом второго i

элемента И-НЕ, выход которого соединен с входом установки первого триггера, вход сброса которого соединен с входом сброса второго триггера и с выходом второго элемента И, первый вход которого соединен с входом установки в О устройства и с первыми входами элементов И с третьего по

пятый, выход первого триггера соединен с вторым входом пятого элемента И-НЕ, третий вход которого является входом строба считывания устройства, выход пятого элемента И-НЕ соединен с входом установки второго триггера, выход которого соединен с третьим входом третьего элемента И-НЕ, выход

которого соединен с входом установки третьего триггера, вход сброса которого соединен с выходом третьего элемента И, второй вход которого является входом переполнения счетчика

5 страниц устройства, четвертый вход третьего элемента И-НЕ является информационным входом устройства, выход третьего триггера является выходом конца поиска устройства, второй

о вход второго элемента И соединен с выходом четвертого элемента И-НЕ, второй вход которого соединен с выходом маски устройства и с выходом четвертого триггера, вход установки

5 которого соединен с выходом шестого элемента И-НЕ, первый вход которого (соединен с выходом пятого триггера, вход установки которого соединен с выходом первого элемента И-НЕ, четвертый вход которого является входом признака режима Обход устройства, вход сброса пятого триггера соединен с выходом четвертого элемента И, второй вход которого соединен через второй элемент задержки с выходом

5 блока постоянной памяти и с входом второго элемента НЕ, выход которого соединен с вторым входом шестого элемента И-НЕ, вход сброса триггера маски устройства соединен с вторым входом пятого элемента И, выход которого соединен с входом сброса четвертого триггера.

0

0

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство поиска и контроля адреса страницы для доменной памяти | 1983 |

|

SU1095242A1 |

| Запоминающее устройство | 1983 |

|

SU1117709A1 |

| Запоминающее устройство | 1982 |

|

SU1295447A1 |

| Устройство для приема заказов | 1985 |

|

SU1316020A1 |

| Устройство управления для доменной памяти | 1987 |

|

SU1499407A1 |

| Устройство для контроля доменной памяти | 1982 |

|

SU1022216A1 |

| Устройство управления для памяти на цилиндрических магнитных доменах | 1984 |

|

SU1265855A1 |

| Устройство для контроля доменной памяти | 1988 |

|

SU1501160A1 |

| АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2045787C1 |

| Устройство управления для доменной памяти | 1988 |

|

SU1566409A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении доменных запоминающих устройств. Целью изобретения является повышение надежности за счет блокировки записи в маркерный регистр. Устройство расчитано на использование единичного домена в маркерном регистре, который может быть объявлен "негодным" в режиме блокировки при подаче внешнего сигнала на вход устройства. 2 ил.

| Устройство для начальной установки динамической памяти | 1983 |

|

SU1215134A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство управления для доменной памяти | 1982 |

|

SU1020863A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1989-05-23—Публикация

1987-02-16—Подача