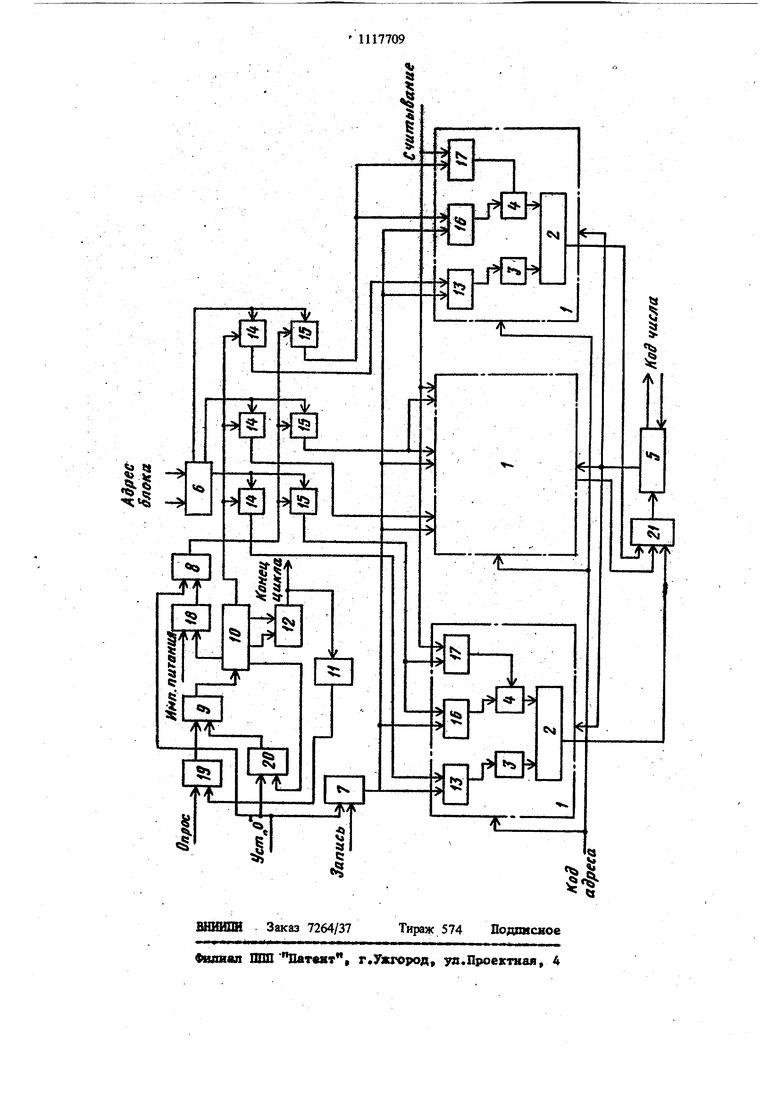

. .Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных машинах и других вычис лительных устройствах. Известно запоминающее устройство, со держащее накопитель, регистр адреса, счетчик адреса, усилитель, дешифратор адреса, ре- : гастр числа, схему управления, дополнительны счетчик, дополнительные ключевые схемы и схему режима работы. Это устройство имеет несколько более высокое быстродействие по сравнению с обычными оперативными запоминающими устройствами за счет непрерьшного заполнения накопителя 1. Однако в этом устройстве при записи произвольной информации по произвольным адресам и при частой смене режимов вьшгрыша в быстродействии не происходит, а надежность устройства снижается за счет введения дополн тельного счетчика, дополнительных ключевых схем и схем режима работы. Наиболее близким к изобретению является устройство, содержащее блоки памяти, адресный регистр, связанный с преобразователем кода адреса, адресные коммутаторы, соединенные с дешифратором, формирователь признака готовности, выходные коммутаторы, выходы которых являются выходами устройства 2. В известном устройстве при произвольном обмейе информацией словами, группами слов и отдельными словами повышения быстродействия не происходит и, кроме того, тратится время на формирование признака готов ности и выходную коммутацию сигналов. Автоматического переключения режимов работ памяти в таком устройстве не осуществляется и не производится совмещения работы режим различных блоков путем выполнения раздель-.но адресных и считывающих операций (причем .такое, совмещение может производиться и в одном блоке памяти для повышения быстродействия). В известном устройстве значительн снижается надежность и повышается мощность потребления из-за одновременной подачи питания на формирователи разрядных токов всех блоков памяти. Кроме того, устройство содержит большое количество оборудования в каждом блоке памяти, что снижает надежность устройства в целом. Целью изобретения является повышение быстродействия и упрощение устройства. Поставленная цель достигается тем, что в запоминающее устройство, содержащее дешиф ратор, блоки памяти, адресные входы которых являются одними из адресных входов устройства, а/информационные входы подкЛю ны к выходам регистра числа, введены три триггера, злемент задержки, злемент НЕ, фор мирователь управляющих отгналов, пять групп злементов И, два злемента И и два элемента ИЛИ, причем первые входы первого и Btopo- го триггеров являются первым управляющим входом устройства, второй вход первого триггера является вторым входом устройства, а его выход соединен с первыми входами зле ментов И первой группь, вторые входы которых подключены к выходам элементов И второй группы, второй вход второго триггера подключен к выходу первого элемента И, первый вход которого соединен с ийиной имг пульного питания, второй вход - с первым выходом элемента задержки, вход которого подключен к выходу третьего триггера, первый вход которого соединен с выходом второ го злемента И, а второй вход - с выходом первого злемента ИЛИ, первый вход которого соединен с первым управляющим входом устройства, а второй вход - с вторым выходом злемента задержки, третий .выход которого подключен к первым входам йтементов И второй группы, а четвертый и пятый выходы - к входам формирователя управляющих сигналов, выход которого является управляющим выходом устройства и входом злемента НЕ, выход которого соединен с первым входом второго элемента И, второй вход которого является третьим упр ляющим входом устройства, причем входы дешифратора являются другими адресными входами устройства, а выходы соединены с вто рыми входами элементов И второй грзшпы и с первыми входами элементов И третьей группы, выходы которых соединены с первыми входами злементов И четвфтой и пятой групп, вторые входы элементов И чертвертой группы подключены к -выходу первого триггера, вторые входы элементов И пятой группы являются четвертым управляющим входом устройства, выход второго триггера соединен с вторыми входами элементов И третьей группы, входы второго злемента ИЛИ соединены с выходами блоков памяти, а выход соединен с вторым входом числового регистра,выходы злементов И первой, четвертой и групп подключены к управляющим входам . блоков памяти. На чертеже представлена структурная схема запоминающего устройства. Запоминающее устройство содержит блоки 1 памяти с включенными в них накопителями 2 и формирователями разрядных 3 и адресных 4 токов, регистр 5 числа, дешифратор 6, первый триггер 7, второй триггер 8, третий триггер 9, злемент 10 задержки, злемент НЕ 11, формирователь 12 управляющих сигналов группы 13-17 элементов И с первой по пятую элементы И и первый первый 18 и второй 20 и второй. 21 элементы ИЛИ. Устройство работает следующим образом. . Перед началом работы и началом любого режима все элементы и узлы устройства устанавливаются в исходное состояние отгналом Установка О. В режиме записи на первый триггер 7 ступает сигнал Запись, который устанавливается в состояние 1, ,открьша1Я элементы И 13 и 16 первой и четЬертой групп соответственно. После этого поступает на второй элемент И 19 импульс Опрос, который при отсутствии запрещающего сигнала с элемента НЕ 11 устанавливает в состояние 1 третий триггер 9, выдающий импульс на запуск элемента 10. Длительность импульса опроса на выходе третьего триггера 9 определяется . тем же самым импульсом, но задержанным иа определенное время в элементе 10 задержки и подаваемым на сброс третьего триггера 9через первый элемент ИЛИ 20. Сигнал Адрес блока поступает на дешифратор 6, а сигнал Код адреса поступает одновременно на все блоки 1 памяти. Дешифратор 6 в соответствии с подаи1сым адресом блока выбира ет по одному элементу И из второй 14 и третьей 15 групп соответственно, при этом сигнал запуска формирователя 4 адресных токов проходит с элемента 10 через соответствуюший элемент И 14 второй группы и чере «Соответствующий элемент И 16 четвертой группы Иа выбранный формирователь 4 адресного тока, заставляя его срабатьгеать. Одновременно подается сигнал Импульс питания на первый элемент И 18 и импульс с элемента 10задержки проходит через этот элемент, устанавливая в состояние 1 второй триггер 8, разрешающий через соответствующие элементы И 14 и 13 второй и первой групп соответственно работу формирователей 3 разрядных токов в выбранном блоке. Таким образом, дающие наибольшее потребление мощности формирователи разрядных 3 и адресных 4 токов работают только в выбранном блоке, а также блокируется подача питания на предусилители (не показаны) невыбранных блоков чем достигается зна.чительное снижение общей потребляемой мощности. В результате в выб-.. ранную ячейку выданного блока 1 памяти за писывается код числа, поступающий на регистр . 5, а с него на формирователи 3 разрядных токов. На формирователе 12 импульсами с члемента 10 форм1фуется сигнал Коиец цик19 ла , который передается в другие устройства ЦВМ, управляющие работой данного запоминающего устройства. Этот же сигнал запрещает прием новых сигналов Опрос да зяп пшения всех процессов в управляющей части. Однако сигнал Конец цикла формируется раньще, чем закончены все процессы записи, в результате чего второй элемент И 19 также открывается раньше для приема новых сигналов Юпрос (до завершения первого цикла записи). Этим самым достигается совмещение циклов работы запоминающего устройства как в режиме записи; так и в других режимах (л том числе и чередующихся), что значительно увелйЫвает быстродействие запоминающего устройства при его миогоцикловой работе. В режиме считывания с гашением сигнал Считьшаиие поступает на элементы И 17 пятой группы, разрешая при подаче импульса Опрос и запуске третьего триггера 9 прохождение сформированного импульса элемента 10 задержки через выбранный (согласно поданному адресу блока на дешифратор 6) элемент И 15 третьей группы на запуск соответствующего формирователя 4 адресных токов в выбранном блоке I памяти. Из накопителя 2 этого блока считьгеается код числа, подаваемый через второй элемент ИЛИ 21 и регистр 5 на выход устройства, а в соответствующую ячейку автоматически записывается О (за исключением контрольных разрядов, куда записьшается код II). В режиме считывания с регенерацией подается сигнал Опрос и устройство работает как и в режиме считьгоания с гашением. Однако после того, как код числа Появится в регистре 5, в такте записи происходит перезапись считанного числа по заданному адресу. Следует отметить, что в режимах с штывания с гашением и считывания с регенерацией, как и в режиме записи, производится совмещение различных циклов с помощью формирователя 12 и злементаНЕ 11 путем более раннего Открьгеаиия второго элемента И 19. Таким образом, исгользоваиие предлагаемого запоминающего устройства позволяет значительно подиять быстродействие устройства при его многократном опросе за счет совмещения циклов при любых режимах работы, сократить количество используемого оборудования в устройстве, состоящем из нескольких блоков и тем самым повысить иадежиость устройства в целом, уменьшить потребление мощности в результате подачи питания на формирователи разрядных токов только выбранного блока .

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с автономным контролем | 1983 |

|

SU1100640A1 |

| Устройство для сопряжения ЭВМ с абонентами | 1987 |

|

SU1411760A1 |

| Микропрограммное устройство для анализа программ | 1980 |

|

SU943729A1 |

| Многоканальное устройство для регистрации аналоговых и цифровых сигналов | 1988 |

|

SU1564649A1 |

| Оперативное запоминающее устройство | 1983 |

|

SU1095233A1 |

| Измеритель временных интервалов | 1983 |

|

SU1155990A1 |

| Постоянное запоминающее устройство | 1985 |

|

SU1247949A1 |

| Устройство для отображения графической информации | 1988 |

|

SU1566339A1 |

| Многоканальная система измерения и регистрации | 1988 |

|

SU1707546A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ОДНОВРЕМЕННОЙ ВЫБОРКОЙ НЕСКОЛЬКИХ СЛОВ | 1990 |

|

RU2022371C1 |

ЗАПОМИНАЮЩЕЕ УСТЮЙСТЮ, содержащее дешифратор, блоки памяти, адресные входы которых являются одними из адресных входов устройства, а информационные входы подключены к выходам регистра числа, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия и упрощения устройства, в него введены три триггера, элемент задержки, элемент НЕ, формирователь управляющих сигналов, пять групп элементов И, два элемента И и два элемента ИЛИ, причем первые входы первого и второго триггеров явля ются первым управляющим входом устройства, второй вход первого триггера является вторым входом устройства, а его выход соединен с первыми входами элементов И первой группы, вторые входы которых подключены к -выходам элементов И второй группы, второй вход второго триггера подключен к выходу первого элемента И, первый вход которого соединен с щиной импульсного питания, второй вход - с перъым выходом элемента задержки, вход которого подключен к выходу третьего триггера, первый вход, которого соединен с выходом второго элемента И, а второй вход - с выходом первого элемента ИЛИ, первый вход которого соединен с первым управляющим входом устройства, а второй вход - с вторым выходом эЛ1емента задержки, третий выход которого подключен к первым входам элементов И второй группы, а четвертый и пятый выходы - к входам формирователя управляющих сигналов, выход которого является управляюпшм выходом устройства и соединен с входом элемента НЕ, выход которого соединен с первым входом второго элемента И, второй вход которого является третьим управляющим входом устройства, причем входы дещифратора являются др1угими адресными входами устройства, а выходы соединены с вторыми входами элементов И второй группы и с первыми входа ми элементов И третьей группы, выходы которых соединены с первыми входами элементов И четвертой н пятой групп, вторые входы элементов И четвертой группы подключены к выходу первого т|жггера, вторые входы элементов И пятой груптад являются четвертым управляющи1м входом устройства, выЬ1 ход второго триггера соединен с вторыми вхоч дами элементов И третьей группы, входы второго элйугента ИЛИ соединены с выходами блоков памяти, а выход соединен с вторым входом числового регистра, выходы элементов И первой, четвертой и пятой групп подключены к управляющим входам блоков памяти.

t «

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для управления оперативным накопителей | 1972 |

|

SU463145A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для управления блоками памяти | 1976 |

|

SU636676A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1984-10-07—Публикация

1983-06-27—Подача