О

3 00со

4 С& С5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цифрового функционального преобразования | 1981 |

|

SU993271A1 |

| Функциональный генератор | 1983 |

|

SU1120308A1 |

| Линейный интерполятор | 1988 |

|

SU1538166A2 |

| Устройство для термокомпенсации кварцевого генератора | 1985 |

|

SU1241406A1 |

| Многоканальный функциональный генератор | 1984 |

|

SU1191922A1 |

| Интерполятор | 1987 |

|

SU1413602A1 |

| Цифровой функциональный преобразователь | 1983 |

|

SU1098006A1 |

| Устройство для измерения временных интервалов | 1985 |

|

SU1293692A1 |

| Устройство термокомпенсации кварцевого генератора | 1990 |

|

SU1709492A1 |

| Устройство программного управления | 1984 |

|

SU1246055A1 |

Изобретение относится к автоматике и вычислительной технике. Цель изобретения - упрощение интерполятора за счет сокращения объема блока памяти. Кусочно-линейный интерполятор содержит ключ 1, два счетчика 2 и 3, блок памяти 4 узловых значений функции, линейный преобразователь 5 код - вероятность, блок 6 синхронизации, делитель частоты 7, генератор импульсов 8, переключатель 9, триггер 10 и два формирователя 11 и 12 коротких импульсов. Устройство выполняет интерполяцию не только по аргументу функции, но и по ее значениям, т.е. истинные значения функции вычисляются на основе осреднения значений функции по ряду узлов интерполяции, что позволяет уменьшить разрядность представления функции в блоке памяти и тем самым уменьшить его объем. 4 ил.

Фиг. 1

Изобретение относится к области автоматики и вычислительной техники и может использоваться для линейного преобразования информации.

Целью изобретения является упрощение интерполятора за счет сокращения объема блока памяти.

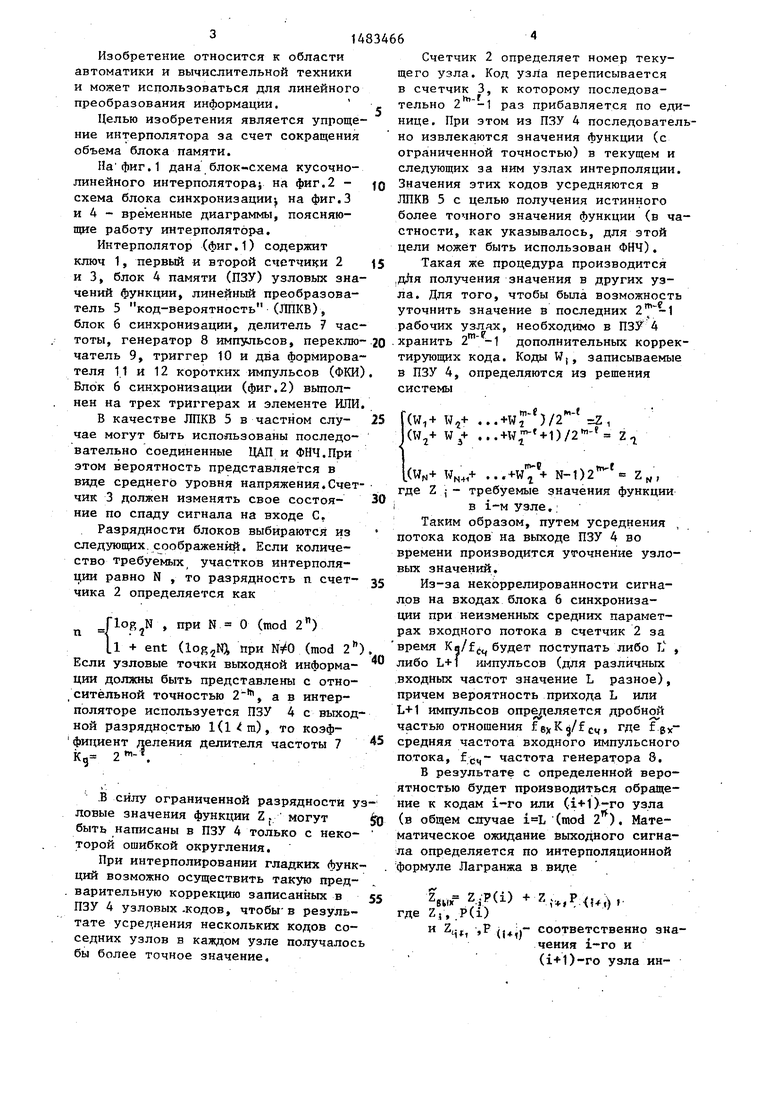

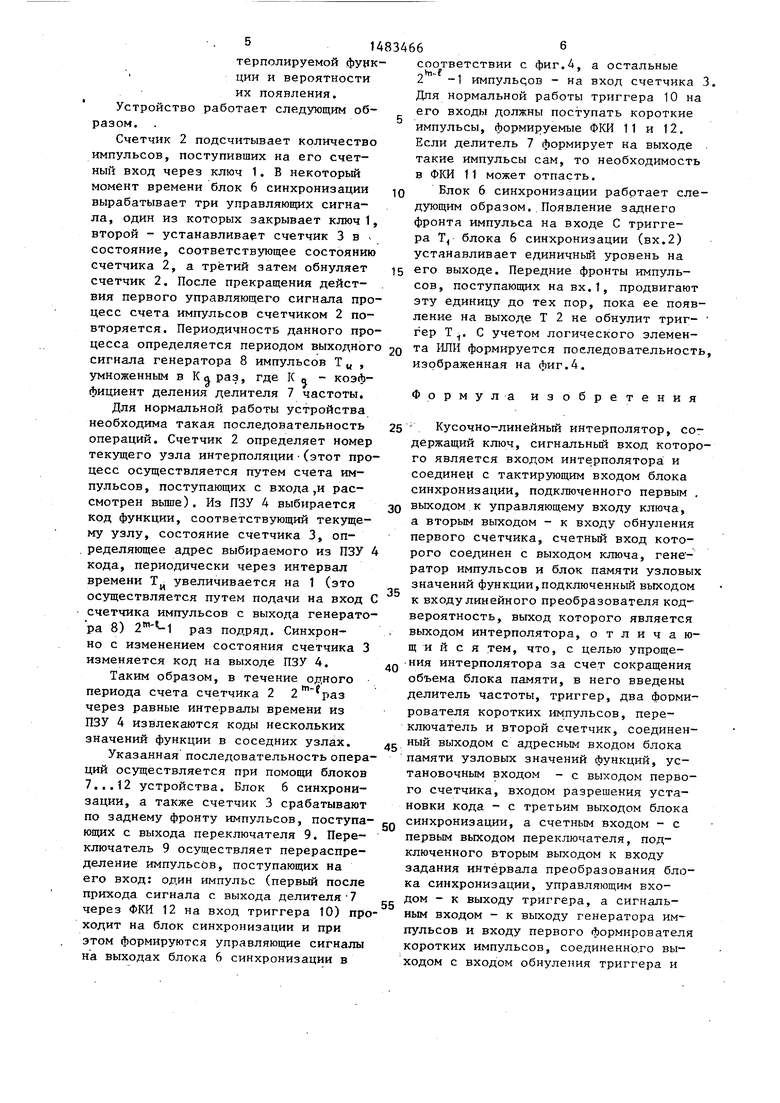

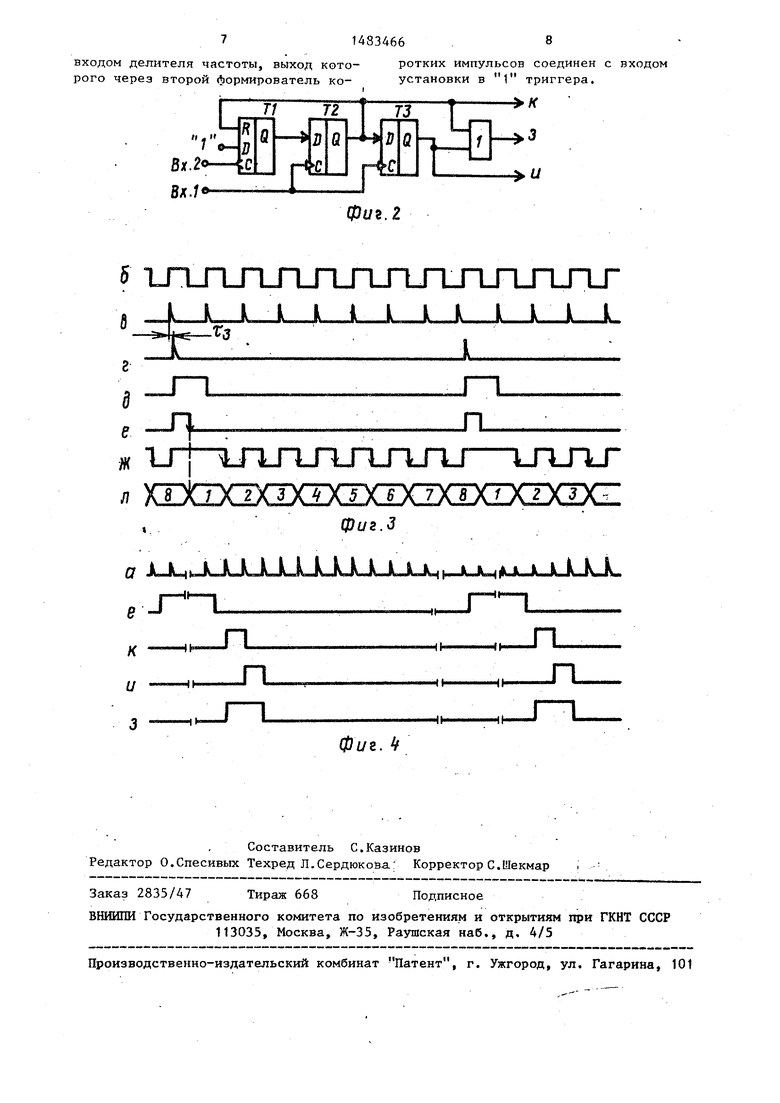

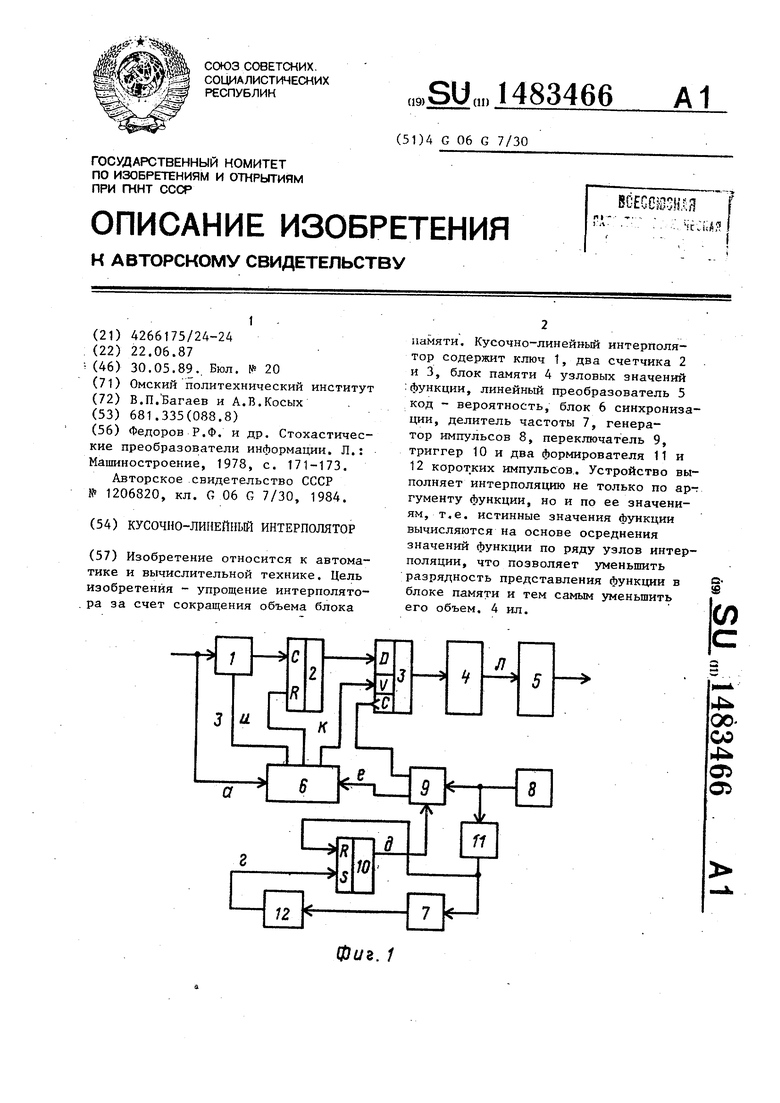

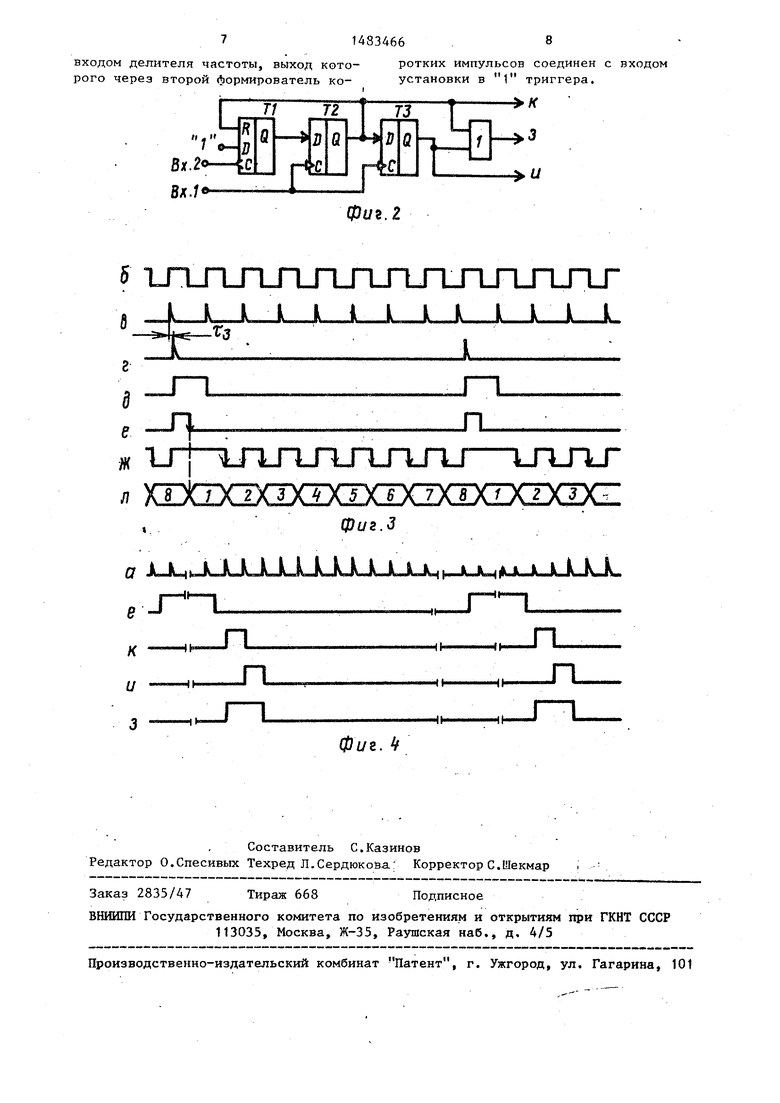

На1 фиг.1 дана блок-схема кусочно- линейного интерполятора; на фиг.2 - схема блока синхронизации-, на фиг.З и 4 - временные диаграммы, поясняющие работу интерполятора.

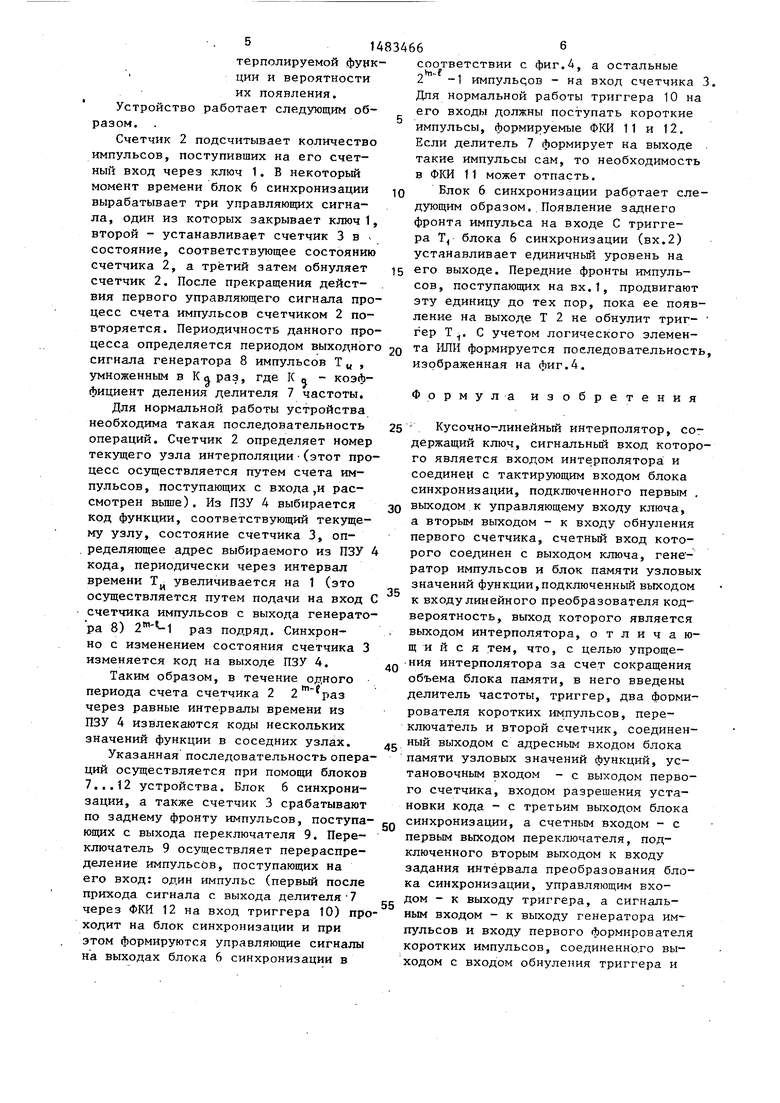

Интерполятор (фиг.1) содержит ключ 1, первый и второй счетчики 2 и 3, блок 4 памяти (ПЗУ) узловых значений функции, линейный преобразователь 5 код-вероятность (ЛПКВ), блок 6 синхронизации, делитель 7 частоты, генератор 8 импульсов, переклю- чатель 9, триггер 10 и два формирователя 11 и 12 коротких импульсов (ФКИ) Блок 6 синхронизации (фиг.2) выполнен на трех триггерах и элементе ИЛИ.

В качестве ЛПКВ 5 в частном случае могут быть использованы последовательно соединенные ЦАП и ФНЧ.При этом вероятность представляется в виде среднего уровня напряжения.Счетчик 3 должен изменять свое состояние по спаду сигнала на входе С.

Разрядности блоков выбираются из следующих соображений. Если количество требуемых, участков интерполяции равно N , то разрядность п счетчика 2 определяется как

n 1 + ent

при N О (mod 2)

(log2NX при HMO (mod 2h) Если узловые точки выходной информации должны быть представлены с относительной точностью , а в интерполяторе используется ПЗУ 4 с выходной разрядностью 1(1 т), то коэф- фициент деления делителя частоты 7

К,

т-Т

В силу ограниченной разрядности узловые значения функции Z. могут Ј0 быть написаны в ПЗУ 4 только с неко- торой ошибкой округления.

При интерполировании гладких функций возможно осуществить такую пред- „ варительную коррекцию записанных в 55 ПЗУ 4 узловых .кодов, чтобы в результате усреднения нескольких кодов соседних узлов в каждом узле получалось бы более точное значение.

O

0

Счетчик 2 определяет номер текущего узла. Код узла переписывается в счетчик 3, к которому последовательно 2 -1 раз прибавляется по единице. При этом из ПЗУ 4 последовательно извлекаются значения функции (с ограниченной точностью) в текущем и следующих за ним узлах интерполяции. Значения этих кодов усредняются в ЛПКВ 5 с целью получения истинного более точного значения функции (в частности, как указывалось, для этой цели может быть использован ФНЧ).

Такая же процедура производится для получения значения в других узла. Для того, чтобы была возможность уточнить значение в последних рабочих узлах, необходимо в ПЗУ 4 хранить 2т -1 дополнительных корректирующих кода. Коды Wj, записываемые в ПЗУ 4, определяются из решения системы

(W,+ W4+ ...+кГ ) Z,

(w2+

W3+

I(WN+ w,

...+wjbl+i)/2ln- - z

,+ ...+W7+ N-1) N

где Z ,- - требуемые значения функции в i-м узле.

Таким образом, путем усреднения потока кодов на выходе ПЗУ 4 во времени производится уточнение узловых значений.

Из-за некоррелированности сигналов на входах блока 6 синхронизации при неизменных средних параметрах входного потока в счетчик 2 за время Kn/fC4 будет поступать либо L1 , либо L+f импульсов (для различных входных частот значение L разное), причем вероятность прихода L или L+1 импульсов определяется дробной

частью отношения feyKq/fcv гЯе f Bx средняя частота входного импульсного потока, fC4- частота генератора 8.

В результате с определенной вероятностью будет производиться обращение к кодам 1-го или (i+l)-ro узла (в общем случае (mod 2 ). Математическое ожидание выходного сигнала определяется по интерполяционной формуле Лагранжа в виде

где

чения i-ro и (i-M)-ro узла ин514

терполируемой функции и вероятности их появления.

Устройство работает следующим образом.

Счетчик 2 подсчитывает количество импульсов, поступивших на его счетный вход через ключ 1. В некоторый момент времени блок 6 синхронизации вырабатывает три управляющих сигнала, один из которых закрывает ключ 1, второй - устанавливает счетчик 3 в состояние, соответствующее состоянию счетчика 2, а третий затем обнуляет счетчик 2. После прекращения действия первого управляющего сигнала процесс счета импульсов счетчиком 2 повторяется. Периодичность данного про

25

30

35

цесса определяется периодом выходного 20 та ИЛИ формируется последовательность, сигнала генератора 8 импульсов Т н , умноженным в К л раз, где К о - коэффициент деления делителя 7 частоты. Для нормальной работы устройства необходима такая последовательность операций. Счетчик 2 определяет номер текущего узла интерполяции (этот процесс осуществляется путем счета импульсов , поступающих с входа ,и рассмотрен выше) . Из ПЗУ 4 выбирается код функции, соответствующий текущему узлу, состояние счетчика 3, определяющее адрес выбираемого из ПЗУ 4 кода, периодически через интервал времени Т.. увеличивается на 1 (это

п

осуществляется путем подачи на вход С счетчика импульсов с выхода генератора 8) раз подряд. Синхронно с изменением состояния счетчика 3 изменяется код на выходе ПЗУ 4.

Таким образом, в течение одного периода счета счетчика 2 через равные интервалы времени из ПЗУ 4 извлекаются коды нескольких значений функции в соседних узлах.

Указанная последовательность операций осуществляется при помощи блоков 7...12 устройства. Блок 6 синхронизации, а также счетчик 3 срабатывают по заднему фронту импульсов, поступающих с выхода переключателя 9. Переключатель 9 осуществляет перераспределение импульсов, поступающих на его вход: один импульс (первый после прихода сигнала с выхода делителя 7 через ФКИ 12 на вход триггера 10) проходит на блок синхронизации и при этом формируются управляющие сигналы на выходах блока 6 синхронизации в

40

45

50

55

изображенная на фиг.4. Формула изобретения

Кусочно-линейный интерполятор, содержащий ключ, сигнальный вход которого является входом интерполятора и соединен с тактирующим входом блока синхронизации, подключенного первым . выходом к управляющему входу ключа, а вторым выходом - к входу обнуления первого счетчика, счетный вход которого соединен с выходом ключа, генератор импульсов и блок памяти узловых значений функции,подключенный выходом к входу линейного преобразователя код- вероятность, выход которого является выходом интерполятора, о т л и ч а ю- щ и и с я тем, что, с целью упрощения интерполятора за счет сокращения объема блока памяти, в него введены делитель частоты, триггер, два Формирователя коротких импульсов, переключатель и второй счетчик, соединенный выходом с адресным входом блока памяти узловых значений функций, установочным входом - с выходом первого счетчика, входом разрешения установки кода - с третьим выходом блока синхронизации, а счетным входом - с первым выходом переключателя, подключенного вторым выходом к входу задания интервала преобразования блока синхронизации, управляющим входом - к выходу триггера, а сигнальным входом - к выходу генератора импульсов и входу первого формирователя коротких импульсов, соединенного выходом с входом обнуления триггера и

соответствии с фиг.4, а остальные

Vvi 9

2 -1 импульсов - на вход счетчика

Для нормальной работы триггера 10 на его входы должны поступать короткие импульсы, формируемые ФКИ 11 и 12. Если делитель 7 формирует на выходе такие импульсы сам, то необходимость в ФКИ 11 может отпасть.

Блок 6 синхронизации работает следующим образом. Появление заднего фронта импульса на входе С триггера Т блока 6 синхронизации (вх.2) устанавливает единичный уровень на его выходе. Передние фронты импульсов, поступающих на вх.1, продвигают эту единицу до тех пор, пока ее появление на выходе Т 2 не обнулит триггер Т ... С учетом логического элемен5

0

5

0 та ИЛИ формируется последовательность,

0

5

0

5

изображенная на фиг.4. Формула изобретения

Кусочно-линейный интерполятор, содержащий ключ, сигнальный вход которого является входом интерполятора и соединен с тактирующим входом блока синхронизации, подключенного первым . выходом к управляющему входу ключа, а вторым выходом - к входу обнуления первого счетчика, счетный вход которого соединен с выходом ключа, генератор импульсов и блок памяти узловых значений функции,подключенный выходом к входу линейного преобразователя код- вероятность, выход которого является выходом интерполятора, о т л и ч а ю- щ и и с я тем, что, с целью упрощения интерполятора за счет сокращения объема блока памяти, в него введены делитель частоты, триггер, два Формирователя коротких импульсов, переключатель и второй счетчик, соединенный выходом с адресным входом блока памяти узловых значений функций, установочным входом - с выходом первого счетчика, входом разрешения установки кода - с третьим выходом блока синхронизации, а счетным входом - с первым выходом переключателя, подключенного вторым выходом к входу задания интервала преобразования блока синхронизации, управляющим входом - к выходу триггера, а сигнальным входом - к выходу генератора импульсов и входу первого формирователя коротких импульсов, соединенного выходом с входом обнуления триггера и

входом делителя частоты, выход которого через второй формирователь коВх.2 Вх.1

Фиг.2

5 TJTJTJIJTJTJTJTJTJ

ж

lJT LTlJ LJTJlJ LriJLTLTLT

a JUL,JLLlJiiAAlXJLJL

Фиг. f

ротких импульсов соединен с входом установки в 1 триггера.

и

| Федоров Р.Ф | |||

| и др | |||

| Стохастические преобразователи информации | |||

| Л.: Машиностроение, 1978, с | |||

| Аппарат для передачи изображений на расстояние | 1920 |

|

SU171A1 |

| Стохастический кусочно-линейный интерполятор | 1984 |

|

SU1206820A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-05-30—Публикация

1987-06-22—Подача