4; со

о а:

00

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор для мультипроцессорной системы | 1987 |

|

SU1517035A1 |

| РЕЗЕРВИРОВАННАЯ СИСТЕМА | 1991 |

|

RU2010315C1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ МАТРИЦЫ НЕПОЛНОГО ПАРАЛЛЕЛИЗМА | 2009 |

|

RU2421804C2 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| Многоканальная система управления распределением ресурсов в вычислительном комплексе | 1987 |

|

SU1432580A1 |

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

| СПОСОБ АРБИТРАЖА ДОСТУПА ГРУППЫ АБОНЕНТОВ К ОБЩИМ РЕСУРСАМ | 1999 |

|

RU2153775C1 |

| Микропроцессорное устройство обработки данных | 1982 |

|

SU1291999A1 |

| Устройство для отладки программно-аппаратных блоков | 1985 |

|

SU1315984A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С ТЕЛЕФОННЫМИ ЛИНИЯМИ СВЯЗИ | 1992 |

|

RU2006927C1 |

Изобретение относится к вычислительной технике и предназначено для организации двухпроцессорных систем. Цель изобретения - уменьшение времени доступа к памяти. Устройство содержит элементы И 27, 28, элементы НЕ 29, 30, элементы И 31, 32, элемент НЕ 33, элементы И 34, 35, триггер 36 арбитража, элемент ИЛИ 37, коммутаторы 38, 39, элемент НЕ 40, триггеры готовности 41, 42, триггер 43 выбора порта, элементы И 44-47, элементы НЕ 48, 49, триггер 50 синхронизации, элементы НЕ 51, 52, элементы И 53, 54, элементы НЕ 55, 56. 3 ИЛ.

.2

Изобретение относится к вычислительной технике и предназначено для организации двухпроцессорных систем.

Цель изобретения - уменьшение времени доступа к памяти.

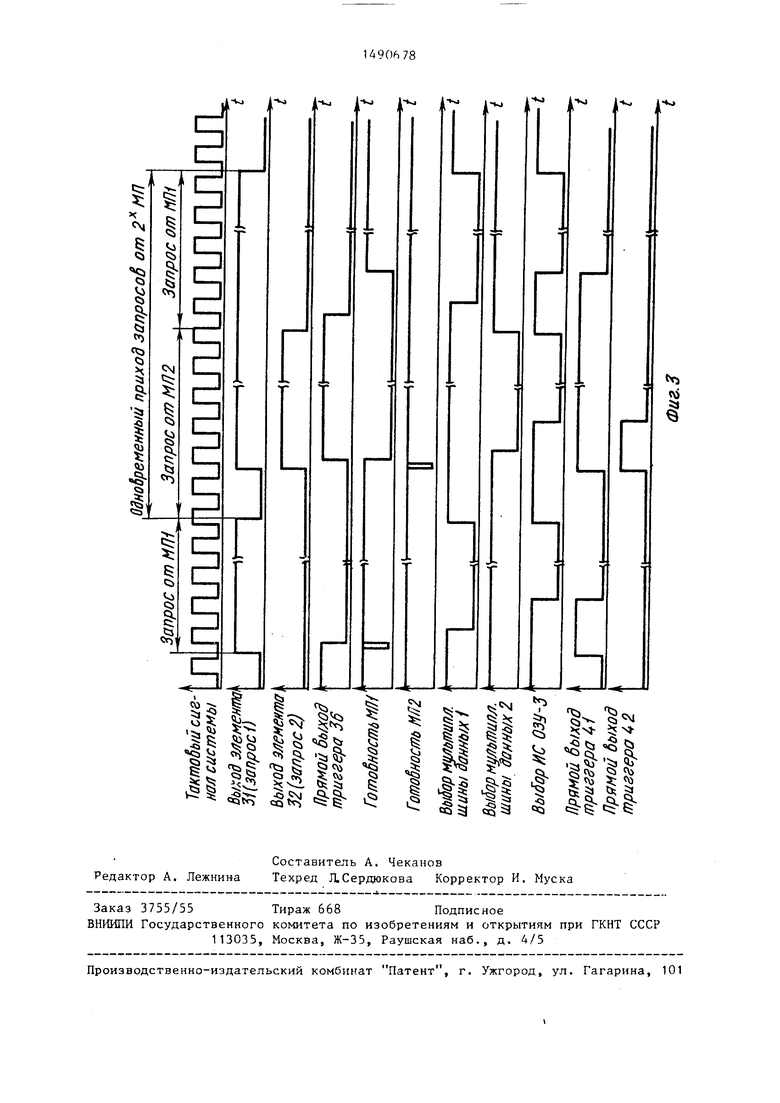

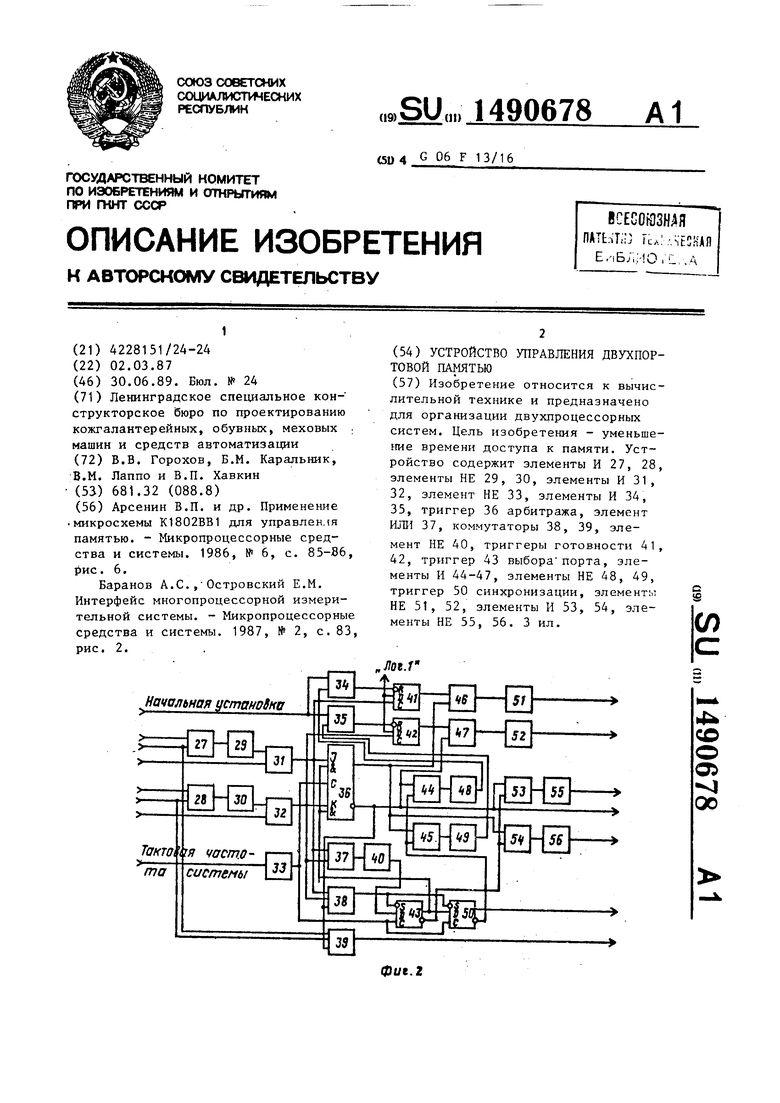

На фиг.1 приведена структурная схема двухпроцессорной системы с двухпортовой памятью; на фиг,2 - структурная схема устройства управления двухпортовой памятью;на фиг.З временные диаграммы работы устройства управления.

Система содержит первое запоминающее устройство 1, первое оперативное запоминающее устройство 2, программируемый таймер 3, программируемый контроллер 4 прерываний, клавиатуру 5, программируемый контроллер 6 дисплея и клавиатуры, формирователь 7 адреса, первый дешифратор 8 адреса, первое программируемое устройство 9 ввода-вывода, второе программируемое устройство 10 ввода-вывода, дисплей 11, первый микропроцессор 12, первый системный контроллер 13, первый мультиплексор 14 шины данных, устройство 15 синхронизации, регистр 16 готовности, устройство 17 управления двухпортовой памятью, третье оперативное запоминающее устройство 18, мультиплексор 19 шины адреса, второй микропроцессор 20, второй системный контроллер 21, второй мультиплексор 22 шины данных, второй дешифратор 23 адреса второе запоминающее устройство 25 и устройство 26 последовательного ввода-вывода.

Устройство управления двухпортовой памятью (фиг.2) содержит первый и второй элементы И 27 и 28,первый и второй элементы НЕ 29 и 30 , третий и четвертьй элементы И 31 и 32, третий элемент НЕ 33, пятый и шестой элементы И 34 и 35, триггер 36 арбитража, элемент ИЛИ 37, первый и второй коммутаторы 38 и 39, элемент НЕ 40, первый и второй триггеры 4 1 и 42 готовности, триггер 43 выбора порта, седьмой-десятый элементы И 44-47, пятый и шестой элементы НЕ 48 и 49, триггер 50 синхронизации, седьмой и восьмой элементы НЕ 51 и 52, одиннадцатый и двенадцатый элементы И 53 и 54, девятый и десятый элементы НЕ 55 и 56.

Устройство работает следующим образом.

При включении системы сигнал на- чальной установки от устройства синхронизации через элементы И 34 и 35 поступает на R-входы триггеров 41 и

42и устанавливает их в нулевое состояние. На выходах элементов НЕ 51

O и 52 формируются сигналы готовности высокого логического уровня, разрешающие работу микропроцессоров системы.

При отсутствии запросов на обраще5 ние к памяти D-триггеры 43 и 50 устанавливаются в единичное состояние по S-входу сигналом с выхода коммутатора 38, сигнал с прямого выхода D-триггера 43 разрешает прием запро0 сов по 1- и К-входам в 1К-триг- гер 36.

При поступлении одного из запросов на обращение к памяти на выходе элемента И 31 или 32 (фиг.З) форми5 руется высокий логический уровень, который устанавливает в единичное состояние соответствующей D-триггер 41 или 42.

Передним фронтом тактового сигна0 ла системы 1К-триггер 36 устанавливается в исходное состояние,соответствующее направлению обслуживания микропроцессора, вьщавшего запрос .

J Выходными сигналами триггера 36 переключаются коммутаторы 38 и 39, а также мультиплексор шины адресов системы сигналом Направление. Высокий логический уровень с элемен0 та И 31 или 32 поступает через коммутатор 38 на S-входы D-триггеров

43и 50-, разрешая их переключение. Одновременно при приходе запроса на выходе элемента ИЛИ 37 формируется

5 низкий логический уровень, поступающий на D-вход триггера 43. Задним фронтом сигнала тактовой частоты системы D-триггер 43 устанавливается в нулевое состояние, сигнал с его прямого выхода запрещает дальнейшие переключения 1К-триггера 36. Высокий логический уровень с инверсного выхода триггера 43 поступает на элементы И 53 и 54, на выходе одного из

, них в зависимости от направления

обслуживания формируется высокий логический уровень, через элемент 55 или 56 разрешающий работу соответствующего мультиплексора шины данных..

0

JTOT же сигнал, ;)адержа1111(,111 D-триг- гером 50 на 1 период тактовой частоты, разрешает выборку микросхемы памяти сигналом Выбор ИС ЗУ,

При наличии на выходе коммутатора 39 низкого логического уровня происходит цикл записи, при его отсутствии - Щ1КЛ чтения. При этом с инверсного выхода D-триггера 50 высокий логический уровень поступает на входы элементов И 44 и 45 и на выходе одного из них в зависимости от направления обслуживания формируется высокий логических уровень, поступающий через элемент 48 или 49 и элемент 34 или 35 на вход D-триггера 41 или 42 и переключающий соответствующий D-триггер в нулевое состояние,

При выполнении запроса низкий логический уровень на выходах элементов НЕ 51 и 52 не формируется, так как триггер 36 установлен в необходимое для обслуживания запроса состояние и работа микропроцессора, выдавшего запрос, не приостанавливается ,

После выполнения процессором в соответствии с внутренним алгоритмом цикла записи или чтения запрос снимается и на соответствующем вькоде элемента И 31 или 32 устанавливается низкий логический уровень, поступающий через коммутатор 38 на S-входы D-триггеров 43 и 50, переключая их в единичное состояние, что приводит к снятию всех выходных сигналов разрешения, 1К-триггер 36 остается в

состоянии, соответствующем направлению обслуженного запроса.

При одновременном поступлении запросов от двух процессоров (фиг,3) на выходах элементов И 31 и 32 устанавливаются высокие логические уровни, подготавливая тем самым 1К-триг- гер 36 к работе в счетном режиме. Передним фронтом тактового сигнала системы 1К-триггер 36 переключается, после чего работа всох узлов аналогична описанной для любого из направлений обслуживания. При этом на выходе одного из элементов НЕ 51 или 52 формируется низкий гюгический уровень, приостанавливая по входу готовность микропроцессор, который не может быть обслужен в этом цикле обращения.

0

5

0

5

0

5

0

5

0

5

После выполнения цикла обращения к памяти в выбранном направлении 1К-триггер 36 переключается тактовым сигналом системы в направление соответствующее ожидающему процессору, на выходах инверторов 51 и 52 формируется высокий логических уровень, разрешая приостановленному процессору произвести запись или чтение ОЗУ-3 в соответствии с внутренним алгоритмом.

Формула изoбpeteния

Устройство управления двухпортовой памятью, содержащее триггер арбитража, отличающееся тем, что, с целью уменьшения времени доступа к памяти, в него введены двенадцать элементов И, десять элементов НЕ, элемент ИЛИ, дна коммутатора, два триггера готовности, триггер выбора порта и триггер синхронизации, причем первые входы записи и чтения устройства подключены соответственно к первому и второму входам первого элемента И, вторые входы чтения и записи устройства подключены соответственно к первому и второму входам второго элемента И, выход первого элемента И через первый элемент НЕ соединен с первым входом третьего элемента И, вьгход второго элемента И через второй элемент НЕ соединен с первым входом четвертого элемента И, выход третьего элемента И соединен с входом синхронизации первого триггера готовности, первым 1-входом триггера арбитража, первым входом элемента ИЛИ и первым информационным входом первого коммутатора, выход четвертого элемента И соединен с входом синхронизации второго триггера готовности, первым К-входом триггера арбитража, вторым входом элемента ИЛИ и вторым информационным входом первого коммутатора, выход которого соединен с входами установки в 1 триггеров выбора порта и син- хронизаци, тактопый вход устройства соединен через третий элемент НЕ с входами си({хронизации триггеров арбитража, выбора порта синхронизации, вход начальной установки устройства подключен к первым входам пятого и щестого элементов И, выходы которых соединены соответственно с входами сброса первого и второго триггеров готовности, выход элемента ИЛИ через

четвертый элемент НЕ соединен с D-входом триггера выбора порта, прямой выход которого соединен с вторыми I- и К-входами триггера арбитража и D-входом триггера синхронизации, прямой выход которого соединен с выходом синхронизации памяти устройства, а инверсный подключён к первым входам седьмого и восьмого элрмен- тов И, выходы которых через пятый и шестой элементы НЕ соединены с вторыми входами пятого и шестого элементов И соответственно, шина логической единицы устройства подключена к D-входам первого и второго триггеров готовности, выходы которых соединены соответственно с первыми входами девятого и десятого элементов И, выходы которых через седьмой и восьмой элементы НЕ соответственно соединены с первым и вторым выходами готовности устройства, инверсный выход триггера выбора порта соединен

У

с первыми входами одиннадцатого и двенадцатого элементов И, выходы которых через девятый и десятый элементы НЕ соответственно соединены с первым и вторым выходами выбора порта устройства, прямой выход триггера арбитража соединен с вторыми входами восьмого, девятого и двенадцатого

0 элементов И, инверсный выход триггера арбитража соединен с вторыми входами седьмого, десятого и одиннадцатого элементов И, выходом задания направления приема адреса устройства

5 и управляющими входами первого и второго коммутаторов, первый и второй входы записи устройства соединены с первым и вторым информационными входами второго коммутатора, выход кото0 рого соединен с выходом записи устройства, первый и второй входы выбора памяти устройства соединены с вторыми входами третьего и четвертого элементов И соответственно.

gju.i

| Арсенин В.П | |||

| и др | |||

| Гальванический газовый элемент | 1924 |

|

SU1802A1 |

| - Микропроцессорные средства и системы | |||

| Пневматический водоподъемный аппарат-двигатель | 1917 |

|

SU1986A1 |

| Устройство для выпрямления опрокинувшихся на бок и затонувших у берега судов | 1922 |

|

SU85A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Баранов А.С., Островский Е.М | |||

| Интерфейс многопроцессорной измерительной системы | |||

| - Микропроцессорные средства и системы | |||

| Кузнечная нефтяная печь с форсункой | 1917 |

|

SU1987A1 |

| Пуговица | 0 |

|

SU83A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1989-06-30—Публикация

1987-03-02—Подача