1зобретение относится к вычислительной технике и может быть использовано для создания многопроцессорных вьнислитеяьных систем.

Целью изобретения является повышение производительности за счет сокращения времени ожидания общей И ины при доступе к одним и тем же элементам памяти.

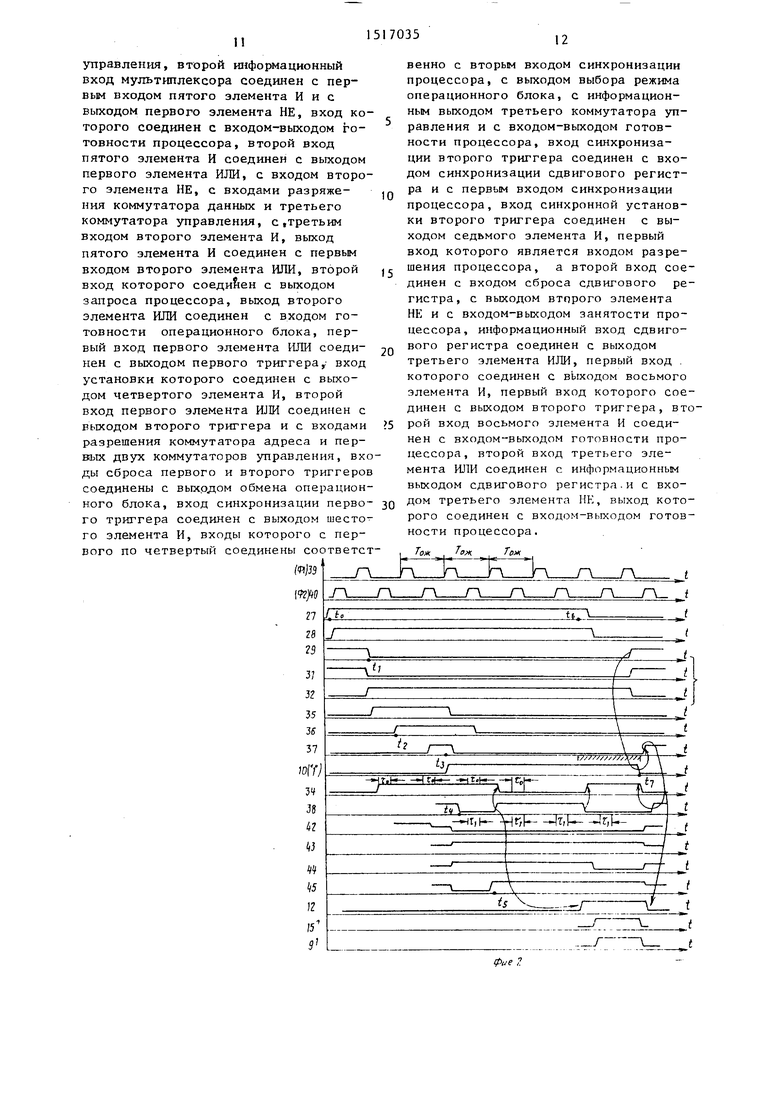

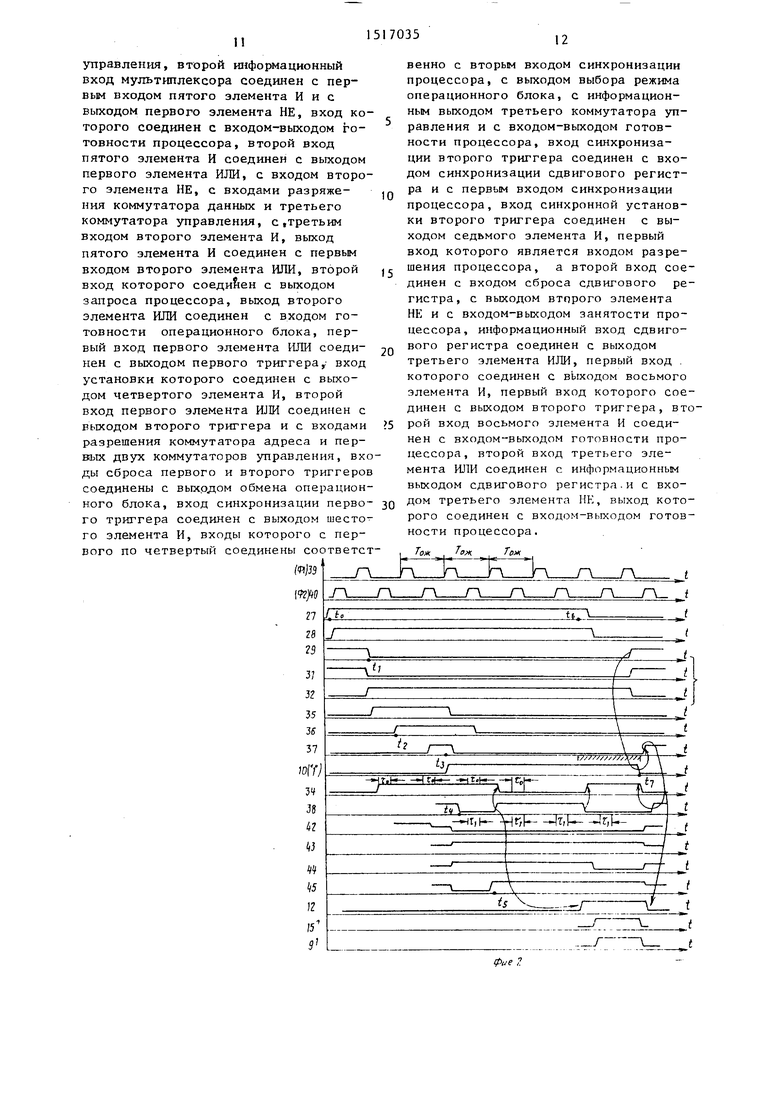

На фиг.1 представлена функциональная схема процессора; на фиг.2- временная диаграмма активного чтения памяти; на фиг.3 - временная диаграмма пассивного чтения памя-

ти во время актршного чтения другим процессором; на фиг,4 - временная диаграмма пассьшного чтения по врем активной записи другим процессором; на фиг.5 - временная диаграмма пас- сивпой записи во время активного чтения памяти другим процессором.

Процессор содержит операционный блок - микронроцессор 1, коммутатор 2 гздреса, коммутатор 3 данных, ком- мутаторы 4-6 управления, мультиплексор 7, формирователь 8 импульсов, схему 9 сравнения, триггеры 10 и 11, сдвиговый регистр 12, элементы И 13 - 20, элементы ШШ 21-23, элементы НЕ 24 - 26, адресные выходы 27 микропроцессора, выход 28 элемента И 13, выход 29 сигнала Обмен микропроцессора, выход 30 сигнала Выбор внешнего устройства процессора, выход 31 сигнала Выбор памяти микропроцессора, выход 32 сигнала Чтение/запись микропроцес сора, входы-выходы 33 данных микропроцессора, вход 34 сигнала Готов- ность микропроцессора, выход 35 сигнала Запуск шины, вход 36 сигнла Разрешение доступа к шине, вход-выход 37 сигнала Шина занята 5зход-выход 38 сигнала Готовность входы 39 и 40 синхронизации, выход сигнала Выбор внешнего устрор1ства )зход-выход 42 сигнала Выбор памяти вход-выход 43 сигнала Чтение/запис }зходы-выходы 44 адреса и входы-выхо ды 45 данных.

Процессор работает следующим образом .

Для обращения микропроцессор 1 задает на адресных выходах 27 код, на управляющем выходе 30 либо 31 - низкого уровня, интерпретиру код адреса в качестве номера усройства ввода-вывода или ячейки памти, а на управляющем выходе 32 - сигнал направления передачи слова информационными входами-выходами 33 (Чтение - при уровне логической 1 и Запись - при уро-вне логического О сигнала).

Определение группы выставляемых на адресных выходах 27 кодовых комбинаций, воздействуя значениями старших позиций адресного слова на элемент И 13, вызьшают установленные на выходе 28 потенциала низкого либо высокого уровня. Первый из них связывается с доступом к приемнику-источнику информации, коммутированному непосредственно на информационные входы-выходы 33, т.е. к личному ресурсу второй - с доступом к внешним ресурсам.

В отсутствие цикла обращения пассивный сигнал (логическая 1) с управляющего выхода 29 микропроцессора блокирует элемент. И 14 от срабатывания и удерживает триггеры 10 и 11 в нулевом состоянии. Формируемый элементом ИЛИ 23 уровень логического О через элемент НЕ 24 допускает установление произвольного уровня сигнала на внешнем входе-выходе 37 режима и устанавливает копию состояния внешнего входа-выхода 43 на входе элемента И 17, копии состояний внешних адресных входов-выходов 44 - на входах схемы 9 сравнения и копию состояния внешего входа-выхода 42 - на первом информационном входе мультиплексора 7 и инверсном входе элемента И 15.

Одновременное присутствие низкого уровня на обоих инверсных входах элемента И 15 обуславливает его срабатывание и разрешение схемы 9 сравнения Результат сравнения поступает на информационный вход триггера 11 и вход элемента И 16. Уровнем сигнала с управляющего выхода 32 микропроцессора устанавливается передача на вход формирователя 8 импульсов состояния первого информационного входа мультиплексора 7 (при логическом О на управляющем входе) либо состояния второго информационного входа - обратного кода внешнего входа-выхода 38 готовности.

Вхождение в цикл обращения сопровождается установлением низкого уровня на управляющем выходе 29 микропроцессора 1 и вызьгоает совместно с сигналом того же уровня на выходе элемента ИЛИ 23 при налнчии потенциала высокого уровня на сигнальной линии (выход 28) формирование элементом И 14 логической 1 на первом входе элемента ИЛИ 21 и на внешнем выходе 35 запроса,

В случае поступления логической 1, например, от арбитра общей информационной шины на внешеий вход 36 разрешения и при установлении высокого потенциала (соответствует ситуации Общая информационная шина свободна) на внешнем входе-выходе 37 режима элементом И 19 задается сигнал логической 1 на информационном входе триггера 10. Нарастание фронта сигнала Ф1 на синхронизирующем входе указьшает триггеру 10 переход в единичное состояние. Появление высокого потенциала на внешнем входе-выходе 37 режима также вызывает сброс регистра 12. Уровень логического О с выходе регистра 12 через элемент НЕ 26 обуславливает из-вне произвольное состояние внешнего входа-выхода 38 готовности.

Логическая 1 на выходе триггера 10, воздействуя непосредственно на управляющие входы коммутаторов 4 и и 5 управления и коммутатора 2 адреса, а через элемент ИЛИ 23 - на управляющий вход коммутатора 6 управления и второй управляющий вход коммутатора 3 данных, инициализирует первый и последний из указанных коммутаторов, а в других вызьшает переключение направления передачи информации, вследствие чего задающие потенциалы управляющих выходов 30 и 31 и адресных выходов 27 микропроцессора 1 повторяются соответственно на внешнем управляющем выходе 41, на внешнем входе-выходе 42 и на внешних йдресных входах-выходах 44, а уровень сигнала на управляющем выходе 32 микропроцессора является одним из опре- деляющих для текущего состояния внешнего входа-выхода 43: низкий потенциал удерживается безусловно, высокий - при отсутствии выставленного из-вне сигнала логического О. Время сохранения заданных состояний регулируется интервалом наличия низкого уровня сигнала на внешнем входе-выходе 38 готовности.

Высокий уровень сигнала на первом входе элемента ИЛИ 21, как и воздействие низкого уровня - указателя источника (приемника) о своей неспособности в заданных тактах вьтолнить выдачу (прием) информационного слова на внешний вход-выход 38 готовности при наличии логической 1 на выходе элемента ИЛИ 23, устанавливает активное состояние входа 34 готовности, которое запрещает изменение внутреннего состояния микропроцессора I и продливает на соответствующее число тактов присутствие указанных уровней сигналов на , адресных выходах

27 и на управляющих выходах 29 - 32.

Восстановление высокого уровня сигнала на внешнем входе-выходе 38 готовности с учетом единичного состояния триггера 10 вызьшает срабатьшание элемента И 20, далее по первому входу элемента ИЛИ 22, и логическая 1, спустя определенное число тактов, по нарастающему фронту сигнала синхрон изации Ф1 передается на выход

регистра 12, ответно переводя через элемент НЕ 26 состояние внешнего входа-выхода 38 готовности в низкое для предотврапгения срабатьшания элементов И }7 других процессоров при переключении адреса. Длительность вводимой регистром 12 задержки выбирается, исходя из продолжительности минимального из двух временных отрезков, началом для которых служит точка вас- приятия пассивного состояния тактового входа 34, а завершениями - точка изменения состояния адресных выходов 27 и точка снятия активного состояния на управляющем выходе 29

при реализации микропроцессором 1 обменов типа Чтение. Логическая 1 с выхода регистра 12, поддерживая активное состояние второго входа элемента ИЛИ 22, самостоятельно сохраняет высокий уровень

сигнала на информационном входе вплоть до установления высокого потенциала на внешнем входе-выходе 37 режима.

Возможность установления единичного состояния в триггере 11 пассивного доступа отражает существующие ситуации, для которых при наличии логического О на внешнем входе 36 разрешения допустима разблокировка микропроцессора 1 по входу 34 готовности для реализации циклов Чтение или Запись во время обращения к общедоступной памяти.

Первая ситуация. Пассивное чтение по время активного чтения памяти другим процессором (фиг.З).

Микропроцессор выставляет на адресном выходе 27 код адреса внешней памяти, а на управляющих выходах 29, 31 , и 32 - соответственно сигналы логического О, логического О и логической 1, что приводит к появлению сигнала логической 1 на выходе 35 (Запрос шины). В то же время другой процессор производит активное чтение содержимого ячейки памяти, обращения к которой требует и пассивный процессор. При появлении сигнала готовности на входе 38 устройства в пассивном процессоре срабатьшает формирователь 8 импульсов, который через элемент И 16 устанавливает в 1 триггер пассивного доступа, поскольку на второй вход элемента И 16 поступает сигнал логической 1 с выхода схемы 9 сравнения, указьшающий что адреса памяти совпадают. Сигнал логической 1 с выхода триггера 11 через элемент ИЛИ 23 производит сброс сигнала запроса шины 35, разрешения коммутатора 3 данных и разблокировку микропроцессора 1 по входу 34, что позволяет микропроцессору 1 произвести считывание информации с входов-выходов 45 данных. Если пассивный процессор начнет свой цикл обращения уже после появления сигнала готовности от памяти, то триггер 11 устанавливается импульсом с выхода элемента И 17, который срабатьшает при наличии высоких уровней сигналов Чтение/запись и сигнала готовности имеете с синхроимпульсом Ф2 по входу 40 устройства.

Вторая ситуация. Пассивное чтение во время активной записи в память, производимой другим процессором (фиг.4)

Пассивный процессор осуществляет чтение информации, которая в это время записьшается другим, активным процессором. Данная ситуация аналогична первой ситуации, за исключением того, что если пассивный процессор начнет свой цикл обращения после того, как память выставит сигнал готовности, то триггер I1 не ус тановится и пассивного чтения не происходит.

Третья ситуация. Пассивная запись во время активного чтения памяти, производимой другим процессором (фиг.З),

Микропроцессор 1 выставляет на адресном выходе 27 код адреса внешней памяти, а на управляюш,их выходах 29,31 и 32 - сигналы логического О, что приводит к появлению сигнала зап. роса шины на выходе 35 устройства и блокировке самого микропроцессора 1 по входу 34. Б то же время активный процессор выставляет на шине сигналы Чтение и Выбор памяти,

г последний из которых вызьшает сраба- тьшание формирователя 8 импульсов пассивного процессора и установку его триггера 11. Сигнал логической 1 с выхода триггера 11 вызьтает снятие

„ запроса шины 35, разрешение коммутатора 3 данных и коммутатора 6 управления, что приводит к появлени о на выходе 43 сигнала логического О (Запись). Информация передается с

5 входов-выходов 33 данных микропроцессора 1 на входы-выходы 45 данных устройства и далее записывается в память и одновременно считывается активным процессором. При появлении

Q сигнала готовности от памяти все процессоры завершают свои циклы.

Таким образом, приступив вследствие фиксации пассивного состояr ния входа 34 готовности к реализации заданной операции обмена, микропроцессор 1 организует передачу слова между своим внутренним узлом и информационными входами-выходами 33,

д вьлолняя при Этом в обращении к общедоступной памяти такт Чтение в условиях, характерных для первой ситуации, синхронно и с допустимым в пределах интервала удержания от

5 сброса высокого потенциала на внешнем входе-выходе 38 готовности смещением и такт Чтение или такт Запись в условиях второй и третьей ситуа ций установления триггера 1 1

Q только синхронно с рассмотренными тактами в других из группы процессоров, а, завершив обмен, снимает логический О на первом управляющем выходе 29.

Поскольку в проводимом цикле обращения к общедоступной памяти процессор не разграничивает, являются ли данные, присутствующие в такте Чтение на внешних информационных

входах-выходах 45, ранее установленным содержимым указанной ячейки либо загружаемым другим процессором в j- сеансе обмена информационным словом, возможное для отдельных вычислений по задаче требование разделения порождаемых и уничтоженных локальными процессами значений может быть обеспечено вьщелением в слове одной, например, старшей (свободной) позиции для фиксации событий. Тогда информационное слово принимается на внутренний регистр микропроцессора 1 с

1517035

10

выход которого является входом-выходом данных процессора, Hf(l)opMauHon- ный вход-выход коммутатора адреса является адресным входом-выходом процессора, выходы выборл внешнего устройства выбора памяти и выбора режима операционного блока соединены С информационными входами соответственно первого, второго и третьего коммутаторов управления, выход обмена операционного блока соединен с вторым входом второго элемента И, вход управления режимом коммутатора

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

| Устройство управления доступом к памяти для обмена массивами данных в многопроцессорной системе | 1989 |

|

SU1633418A1 |

| Устройство для обмена информацией | 1982 |

|

SU1118992A1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| Мультипроцессорная система | 1983 |

|

SU1156088A1 |

| РЕЗЕРВИРОВАННАЯ СИСТЕМА | 1991 |

|

RU2010315C1 |

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

| Многопроцессорная система | 1989 |

|

SU1647597A1 |

| Процессор | 1984 |

|

SU1200294A1 |

| Устройство для обмена информацией между ЭВМ и периферийными устройствами | 1989 |

|

SU1777145A2 |

Изобретение относится к вычислительной технике и может быть использовано для создания многопроцессорных вычислительных систем. Целью изобретения является повышение производительности за счет сокращения времени ожидания общей шины при доступе к одним и тем же элементам памяти. Цель достигается тем, что процессор дополнительно содержит формирователь импульсов 8, сдвиговый регистр 12, мультиплексор 7, элементы И 17, 19 и 20, элементы ИЛИ 21-23, элементы НЕ 24-26, что позволяет процессору осуществлять пассивный доступ к памяти в том случае, если другой, активный, процессор обращается по тому же адресу. 5 ил.

одновременным тестированием кода сво- ts данных соединен с выходом выбора ребодной позиции, и выполняется для завершения комнады одна из ветвей предусмотренной реакции.

Возвращение триггера 10 или 11

жима операционного блока, информацион ный выход первого, информационные входы-выходы второго и третьего коммутаторов управления являются соотв исходное состояние обеспечивает пе- 20 ветственно выходом выбора внешнего

редачу через элемент ИЛИ 23 логического О на вход элемента НЕ 24, что способствует созданию условия для установления другим (последним из группы) процессором из-вне высокого потенциала или собственно устанавливает высокий потенциал на внешнем входе-выходе 37 режима.

В случае установления триггера 10 в текущем цикле обращения после восстановления на внешнем входе-выходе 37 режима высокого потенциала с задержкой на сброс по управляющему входу регистра 12 сдвига и последующего переключения элемента НЕ 25 логическим О на входе последнего задает условие для указания в последующем сеансе обмена произвольного уровня сигнала на внешнем входе-выходе 38 готовности.

Формула изобретения

Процессор для мультипроцессорной системы, содержащий операционный блок, коммутатор адреса, коммутатор данных, три коммутатора управления, два триггера, схему сравнения и пять элементов И, причем адресный выход операционного блока соединен с информационным входом коммутатора адреса и с входом первого элемента И, выход которого соединен с первым входом второго элемента И, выход-ко- торого является выходом запроса процессора, вход-выход данных операционного блока соединен с первым информационные входом-выходом коммутатора данных, второй информационный вход25

30

устройства, входами-выходами выбора памяти и выбора режима процессора, первый и второй входы синхронизации операционного блока являются соотве ственно первым и вторым входами син ронизации процессора, о т л и ч а ю щ и и с я тем, что, с целью повыше ния производительности за счет сокращения времени ожидания обп;ей шины при доступе к одним и тем же элемен там памяти, в него введены мультиплексор, формирователь импульсов, сдвиговый регистр, шестой, седьмой и восьмой элементы И, три элемента 35 ИЛИ и три элемента 1Е, причем пер- вьй информационный вход схемы сравнения соединен с адресным выходом операционного блока, второй информа ционный вход схемы сравнения соединен с информационным выходом коммутатора адреса, вход разрешения схем сравнения соединен с выходом третье го элемента И, первый и второй вход которого соединены соответственно с выходом выбора памяти операционного блока и с информационным выходом второго коммутатора управления, выход результата схемы сравнения сое динен с информационным входом перво го триггера и с первым входом четвертого элемента И, второй вход Ко торого соединен с выходом формирова теля импульсов, вход которого соеди нен с выходом мультиплексора, вход управления которого соединен с выходом выбора режима операционного блока, первый информационный вход мультиплексора соединен с информационным выходом второго коммутатора

40

45

50

55

жима операционного блока, информационный выход первого, информационные входы-выходы второго и третьего коммутаторов управления являются соот5

0

устройства, входами-выходами выбора памяти и выбора режима процессора, первый и второй входы синхронизации операционного блока являются соответственно первым и вторым входами синхронизации процессора, о т л и ч а ю- щ и и с я тем, что, с целью повышения производительности за счет сокращения времени ожидания обп;ей шины при доступе к одним и тем же элементам памяти, в него введены мультиплексор, формирователь импульсов, сдвиговый регистр, шестой, седьмой и восьмой элементы И, три элемента 5 ИЛИ и три элемента 1Е, причем пер- вьй информационный вход схемы сравнения соединен с адресным выходом операционного блока, второй информационный вход схемы сравнения соединен с информационным выходом коммутатора адреса, вход разрешения схемы сравнения соединен с выходом третьего элемента И, первый и второй входы которого соединены соответственно с выходом выбора памяти операционного блока и с информационным выходом второго коммутатора управления, выход результата схемы сравнения соединен с информационным входом первого триггера и с первым входом четвертого элемента И, второй вход Которого соединен с выходом формирователя импульсов, вход которого соединен с выходом мультиплексора, вход управления которого соединен с выходом выбора режима операционного блока, первый информационный вход мультиплексора соединен с информационным выходом второго коммутатора

0

5

0

5

управления, второй информационный вход мультиплексора соединен с первым входом пятого элемента И и с выходом первого элемента НЕ, вход которого соединен с входом-выходом готовности процессора, второй вход пятого элемента И соединен с выходом первого элемента ИЛИ, с входом второго элемента НЕ, с входами разряжения коммутатора данных и третьего коммутатора управления, с,третьим входом второго элемента И, выход пятого элемента И соединен с первым входом второго элемента ИЛИ, второй вход которого соеди&ен с выходом запроса процессора, выход второго элемента ИЛИ соединен с входом готовности операционного блока, первый вход первого элемента ИЛИ соединен с выходом первого триггера, вход установки которого соединен с выходом четвертого элемента И, второй вход первого элемента ШШ соединен с вЫходом второго триггера и с входами разрешения коммутатора адреса и пер- Еътх двух коммутаторов управления, входы сброса первого и второго триггеров соединены с выходом обмена операцион10

15

20

5

венно с вторым входом синхронизации процессора, с выходом выбора режима операционного блока, с информационным выходом третьего коммутатора управления и с входом-выходом готовности процессора, вход синхронизации второго триггера соединен с входом синхронизации сдвигового регистра и с первым входом синхронизации процессора, вход синхронной установки второго триггера соединен с выходом седьмого элемента И, первый вход которого является входом разрешения процессора, а второй вход соединен с входом сброса сдвигового регистра, с выходом второго элемента НЕ и с входом-выходом занятости процессора, информационный вход сдвигового регистра соединен с выходом третьего элемента ИЛИ, первый вход . которого соединен с вЬгходом восьмого элемента И, первый вход которого соединен с выходом второго триггера, второй вход восьмого элемента И соединен с входом-выходом готовности процессора, второй вход третьего элемента ИЛИ соединен с информационным выходом сдвигового регистра.и с вхоного блока, вход синхронизации перво- ЗО третьего элемента НЕ, выход кото

5

0

5

венно с вторым входом синхронизации процессора, с выходом выбора режима операционного блока, с информационным выходом третьего коммутатора управления и с входом-выходом готовности процессора, вход синхронизации второго триггера соединен с входом синхронизации сдвигового регистра и с первым входом синхронизации процессора, вход синхронной установки второго триггера соединен с выходом седьмого элемента И, первый вход которого является входом разрешения процессора, а второй вход соединен с входом сброса сдвигового регистра, с выходом второго элемента НЕ и с входом-выходом занятости процессора, информационный вход сдвигового регистра соединен с выходом третьего элемента ИЛИ, первый вход . которого соединен с вЬгходом восьмого элемента И, первый вход которого соединен с выходом второго триггера, второй вход восьмого элемента И соединен с входом-выходом готовности процессора, второй вход третьего элемента ИЛИ соединен с информационным выходом сдвигового регистра.и с , TOX л

| Устройство для крепления плоской подушки в платформенных весах | 1928 |

|

SU32182A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для избирательного управления с одного конца однопроводной линии несколькими реле | 1918 |

|

SU981A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-10-23—Публикация

1987-10-30—Подача