14

12

16

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивный корректор межсимвольной интерференции | 1987 |

|

SU1540009A1 |

| Частотный дискриминатор | 1988 |

|

SU1676078A2 |

| Устройство для оценки контура изображения | 1981 |

|

SU1076002A3 |

| Устройство для приема фазоманипулированных сигналов с одной боковой полосой | 1983 |

|

SU1164903A1 |

| Частотный дискриминатор | 1986 |

|

SU1359899A1 |

| Демодулятор сигналов с фазоразностной модуляцией | 1984 |

|

SU1216834A1 |

| Устройство для детектирования фазоманипулированных сигналов | 1982 |

|

SU1051737A1 |

| Устройство передачи сигналов | 1988 |

|

SU1552385A1 |

| Устройство для приема и обработки избыточных сигналов | 1984 |

|

SU1193713A1 |

| Приемник дискретной информации | 1982 |

|

SU1104684A1 |

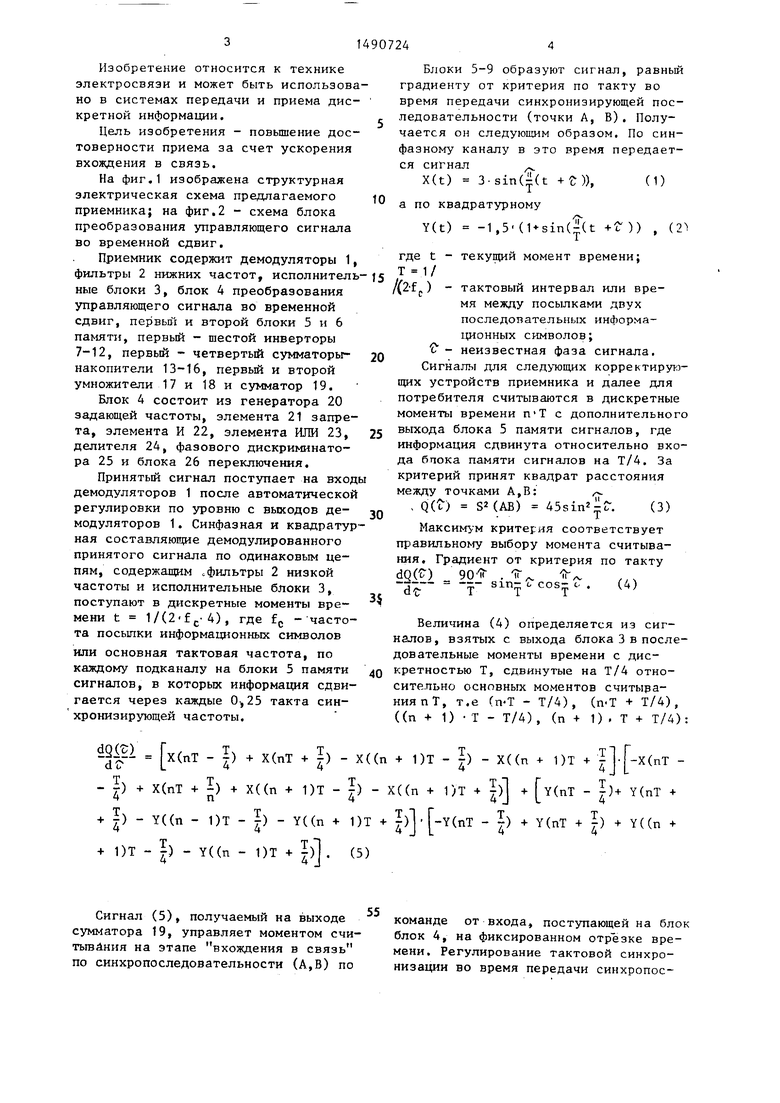

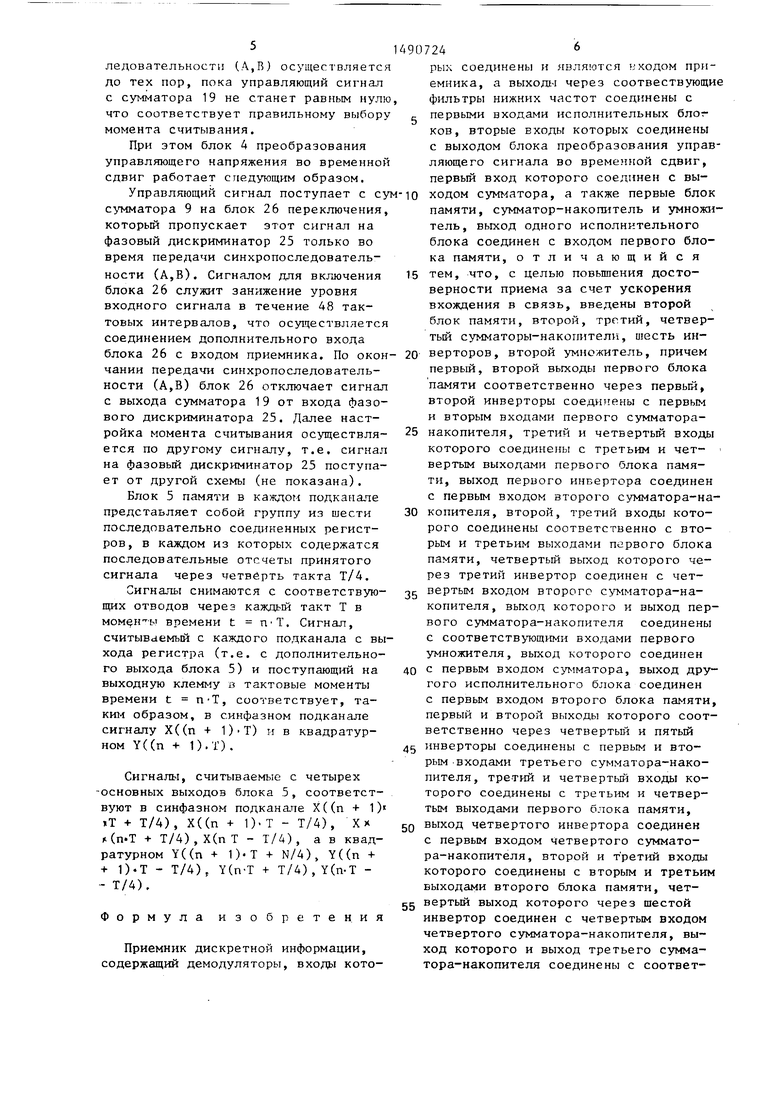

Изобретение относится к электросвязи. Цель изобретения - повышение достоверности приема. Приемник дискретной информации содержит демодуляторы 1, фильтры 2 нижних частот, исполнительные блоки 3, блок 4 преобразования управляющего сигнала во временной сдвиг, блоки памяти 5 и 6, инверторы 7-12, сумматоры-накопители 13-16, умножители 17 и 18 и сумматор 19. Цель достигается за счет обеспечения ускорения вхождения в связь, с помощью введенных блока 6 памяти, инверторов 7-12, сумматоров-накопителей 14-16 и умножителя 18. 2 ил.

Фиг.1

Изобретение относится к технике электросвязи и может быть использовано в системах передачи и приема дне- кретной информации.

Цель изобретения - повышение достоверности приема за счет ускорения вхождения в связь.

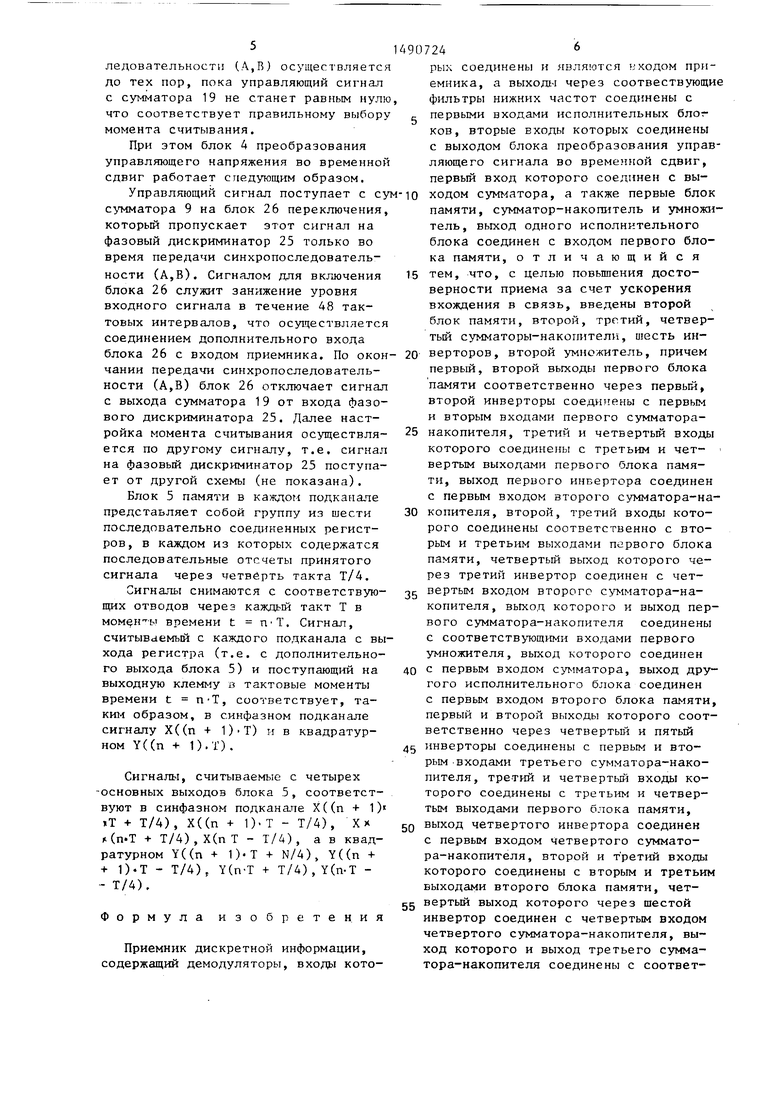

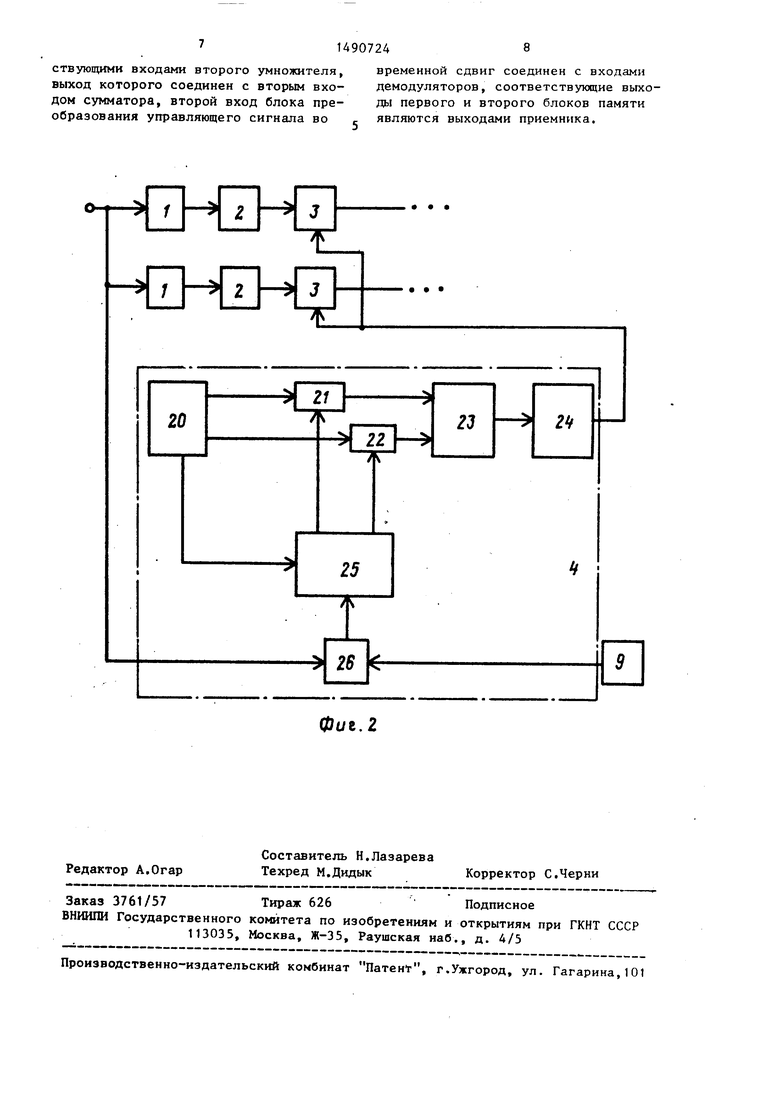

На фиг,1 изображена структурная электрическая схема предлагаемого приемника; на фиг.2 - схема блока преобразования управляющего сигнала во временной сдвиг.

Приемник содержит демодуляторы 1, фильтры 2 нижних частот, исполнитель ные блоки 3, блок 4 преобразования управляющего сигнала во временной сдвиг, nepBbtti и второй блоки 5 и 6 памяти, первый - шестой инверторы 7-12, первый - четвертый сумматоры- накопители 13-16, первый и второй умножители 17 и 18 и сумматор 19.

Блок 4 состоит из генератора 20 задающей частоты, элемента 21 запрета, элемента И 22, элемента ИЛИ 23, делителя 24, фазового дискриминатора 25 и блока 26 переключения.

Принятый сигнал поступает на вход демодуляторов 1 после автоматической регулировки по уровню с выходов де- модуляторов 1. Синфазная и квадратурная составляющие демодулированного принятого сигнала по одинаковым цепям, содержащим «фильтры 2 низкой частоты и исполнительные блоки 3, поступают в дискретные моменты вре

мени

t 1/(2 f...4), где

fp - частота посылки информационных символов или основная тактовая частота, по каждому подканалу на блоки 5 памяти сигналов, в которых информация сдвигается через каждые такта синхронизирующей частоты.

di 1 1 - Х((п + ОТ - |) - Х((п - 1)Т -ь (пТ - Ъ + Х(пТ +I) + Х((п + 1)Т - 7) - Х((п + 1)Т + |)1 -ь Гу(пТ - 7)+ Y(nT +

чП4ч J L ч

+ 7) - Y((n -1)Т -Ь - Y((n + 1)Т + |)(nT - J) + Y(nT + J) + Y((n +

+ 1)Т - 2) - Y((n - 1)Т +

(5)

Сигнал (5), получаемый на выходе сумматора 19, управляет моментом СЧИТЫВАНИЯ на этапе вхождения в связь по синхропоследовательности (А,В) по

Блоки 5-9 образуют сигнал, равный градиенту от критерия по такту во время передачи синхронизирующей последовательности (точки А, В). Получается он следующим образом. По синфазному каналу в это время передается сигнал

X(t) 3-sin(|(t +С)), (1)

а по квадратурному

Y(t) -1,5-((|(t +t}) , (2)

где t Т 1/

/(2-f с)

- текущий момент времени;

тактовый интервал или время между посылками двух последопательных информационных символов; € - неизвестная фаза сигнала. Сигналы для следующих корректирующих устройств приемника и далее для потребителя считываются в дискретные моменты времени п Т с дополнительног выхода блока 5 памяти сигналов, где информация сдвинута относительно входа бгтока памяти сигналов на Т/4. За критерий принят квадрат расстояния между точками А,В:

, Q() S4AB) 45sin -Jr.

(3)

Максимз- М критерия соответствует правильному выбору момента считывания. Градиент от критерия по такту

dg()

dt

90

м

/ sin- t cos- с(4)

Величина (4) определяется из сигналов, взятых с выхода блока 3 в последовательные моменты времени с дискретностью Т, сдвинутые на Т/4 относительно основных моментов считыра- нияпТ, т.е (п Т - Т/4), (п-Т - Т/4), ((п + 1) Т - Т/4), (п + 1) . Т + Т/4):

(5)

команде от входа, поступающей на блок блок 4, на фиксированном отрезке времени. Регулирование тактовой синхронизации во время передачи синхропоследовательности (Л,В) осуществляется до тех пор, пока управляющий сигнал с сумматора 19 не станет равным нулю, что соответствует правильному выбору момента считывания.

При этом блок 4 преобразования управляющего напряжения во временной сдвиг работает спедующим образом.

Управляющий сигнал поступает с сум-ю ходом су№-1атора, а также первые блок

сумматора 9 на блок 26 переключения, который пропускает этот сигнал на фазовый дискриминатор 25 только во время передачи синхропоследователь- ности (А,в). Сигналом для включения блока 26 служит занижение уровня входного сигнала в течение 48 тактовых интервалов, что осуществляется соединением дополнительного входа блока 26 с входом приемника. По окончании передачи синхропоследователь- ности (А,В) блок 26 отключает сигнал с выхода сумматора 19 от входа фазового дискриминатора 25. Далее настройка момента считывания осуществляется по другому сигналу, т.е. сигнал на фазовый дискриминатор 25 поступает от другой схемы (не показана).

Блок 5 памяти в каждом подканале представляет собой группу из шести последовательно соединенных регистров, в каждом из которых содержатся последовательные отсчеты принятого сигнала через четверть такта Т/4.

Сигналы снимаются с соответствующих отводов через каждый такт Т в момен- ы времени t П Т. Сигнал, считываемый с каждого подканала с выхода регистра (т.е. с дополнительного выхода блока 5) и поступающий на выходную клемму в тактовые моменты времени t п-Т, соответствует, таким образом, в синфазном подканале сигналу Х((п + 1)-Т) и в квадратурном Y((n + 1).Т).

Сигналы, считываемые с четырех -основных выходов блока 5, соответствуют в синфазном подканале Х((п + 1)« иТ + Т/4), Х((п + 1) Т - Т/4), XX ti(n.T -t- Т/4),Х(пТ - Т/4), а в квадратурном Y((n + О Т + N/4), Y((n + + 1) Т - Т/4), Y(n-T + T/4),Y(n.T - - Т/4).

Формула изобретения

Приемник дискретной информации, содержащий демодуляторы, входы которык соединены и являются «ходом приемника, а ВЫХОД1-1 через соотвествующие фильтры нижних частот соединены с первыми входами исполнительных блог ков, вторые входы которых соединены с выходом блока преобразования управляющего сигнала во временной сдвиг, первый вход которого соединен с выпамяти, сумматор-накопитель и умножитель, выход одного исполнительного блока соединен с входом первого блока памяти, отличающийся

тем, что, с целью повышения достоверности приема за счет ускорения вхождения в связь, введены второй блок памяти, второй, третий, четвертый сумматоры-накопители, шесть инверторов, второй умножитель, причем первый, второй выходы первого блока памяти соответственно через первый, второй инверторы соединены с первым и вторым входами первого сумматоранакопителя, третий и четвертый входы которого соединены с третьим и четвертым выходами первого блока памяти, выход первого инвертора соединен с первым входом второго сумматора-накопителя, второй, третий входы которого соединены соответственно с вторым и третьим выходами первого блока памяти, четвертый выход которого через третий инвертор соединен с четвертым входом второго сумматора-накопителя, выход которого и выход первого сумматора-накопителя соединены с соответствующими входами первого умножителя, выход которого соединен

с первым входом с тчматора, выход другого исполнительного блока соединен с первым входом второго блока памяти, первый и второй выходы которого соответственно через четвертый и пятый

инверторы соединены с первым и вторым -входами третьего сумматора-накопителя, третий и четвертый входы которого соединены с третьим и четвертым выходами первого блока памяти,

выход четвертого инвертора соединен с первым входом четвертого сумматора-накопителя, второй и т ретий входы которого соединены с вторым и третьим выходами второго блока памяти, четвертый выход которого через шестой инвертор соединен с четвертым входом четвертого сумматора-накопителя, выход которого и выход третьего сумматора-накопителя соединены с соответствующими входами второго умножителя, выход которого соединен с вторым входом сумматора, второй вход блока преобразования управляющего сигнала во

Фиг.2

временной сдвиг соединен с входами демодуляторов, соответствующие выходы первого и второго блоков памяти являются выходами приемника.

| Приемник дискретной информации | 1982 |

|

SU1104684A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1989-06-30—Публикация

1987-05-06—Подача