(Л

о to

sj

00

- 14ч; 47

Изобретение отиосичтя к импульсной технике и может 6i,iTii испо. и.чонан п аппаратуре обработки цифроно информации .

Цель изобретения - понмшение надежности устройств; путем его упрощения .

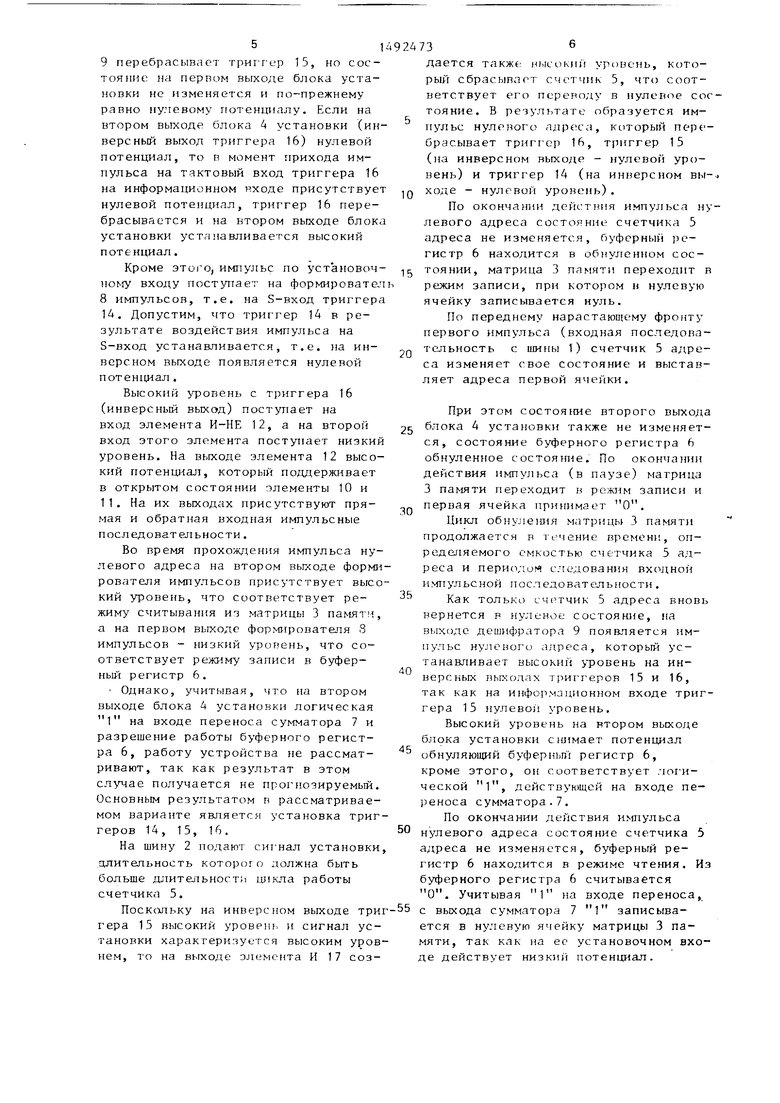

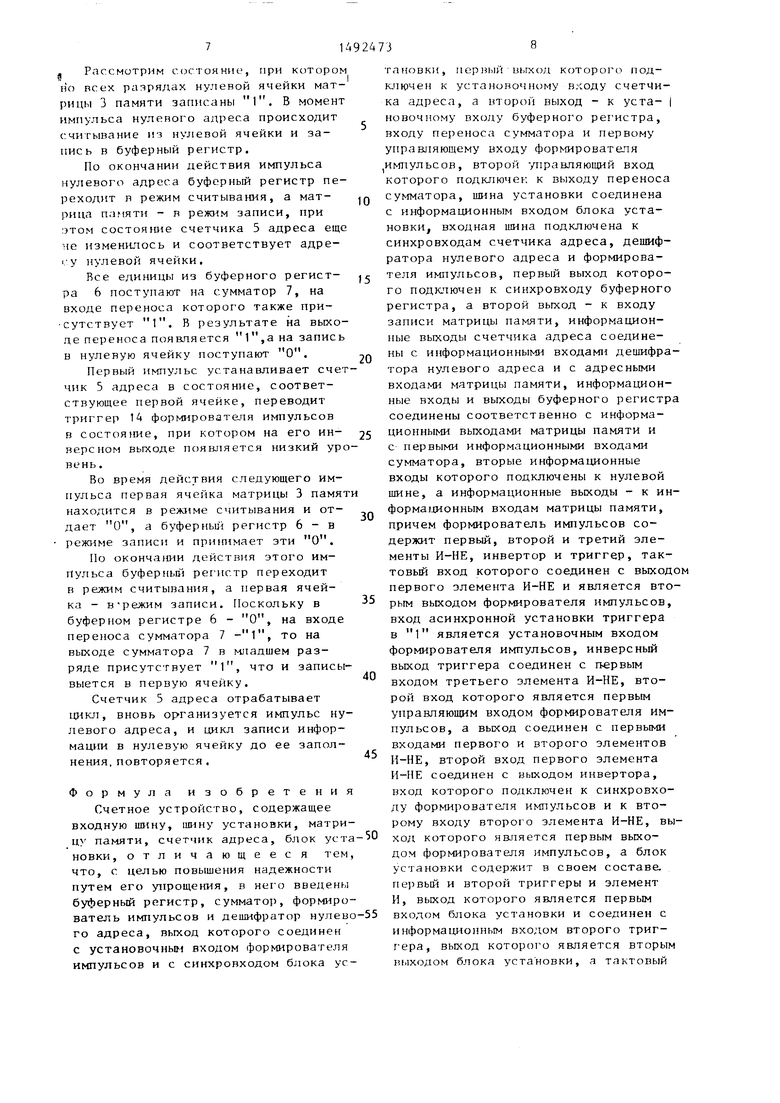

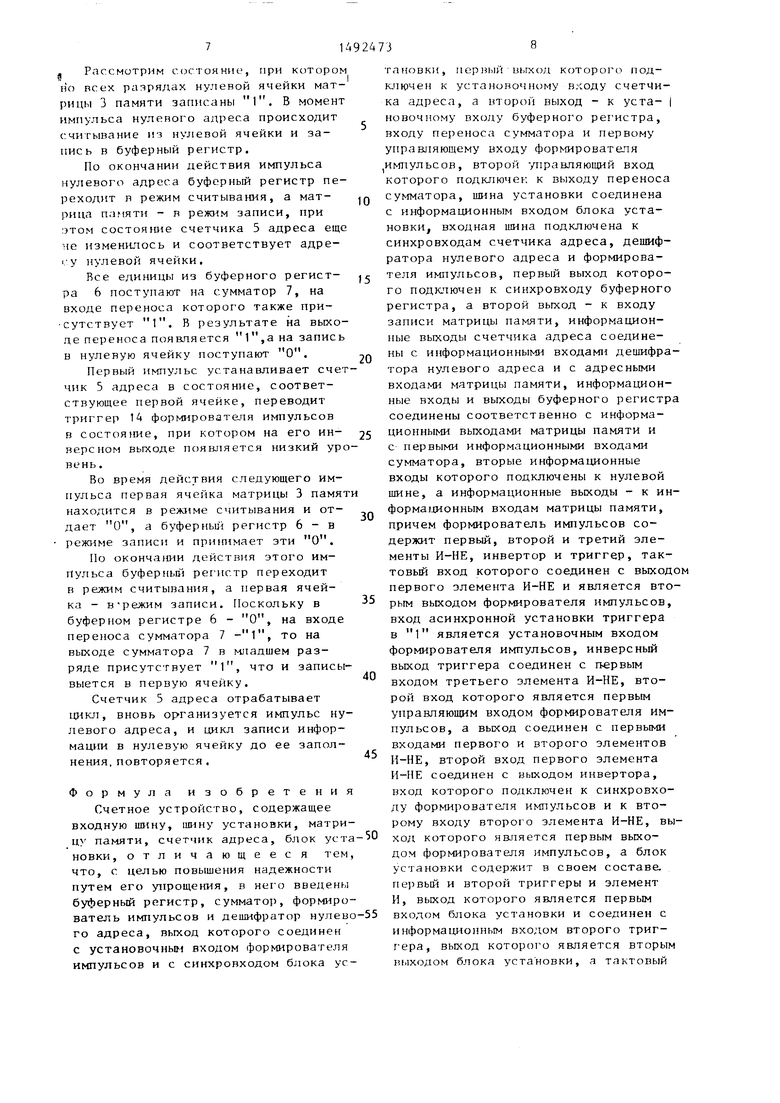

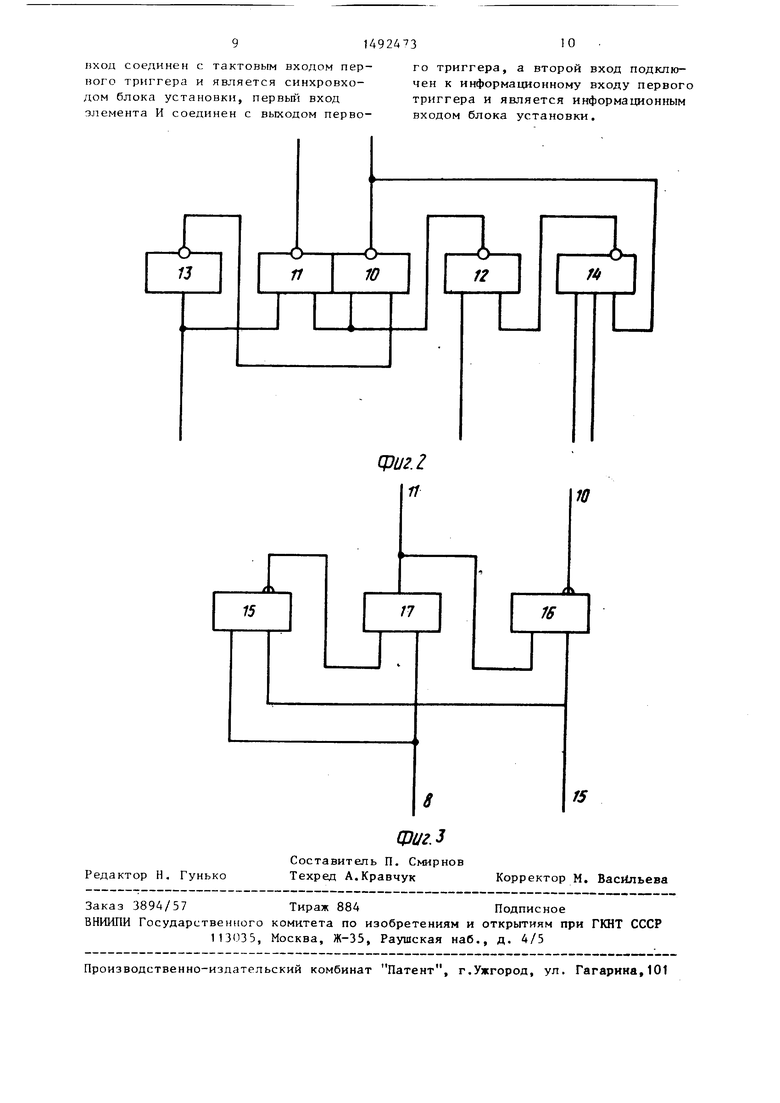

На фиг. 1 показана функциональная схема преллаг яемого устройства; на фиг. 2 - фop п poвaтeль импульсов; на фиг. 3 - блок установки.

Устройство (фиг. 1) содержит входную игину 1, шипу 2 установки, матрицу 3 гтамятИу блок А установки, счетчик 5 адреса, буферный регистр 6, сумматор 7, формирователь 8 импульсов и де1Ш1фратор 9 нулевого ад- jieca, выход которого соединен с установочным входом фop иpoвaтeля импул. сов и синхровходом блока установки, первый выход последнего подключен к установочному входу счетчика адреса, а второй выход к установочному входу буферного регистра, к входу переноса сумматора и к первому управляющему входу формирователя импульсов, второй управляющий вход которого подключен к выходу переноса сумматора, ши}1а 2 установки соединена с информационным входом блока установки, входная шина 1 подключена к синхровходам счетчика 5 адреса, де- 1Ш1фратора 9 нулевого адреса и формирователя импульсов, первый выход последнего подключен к синхровходу буферного регистра, а второй выход к входу записи матрицы памяти, информационные выходы счетчика 5 ад- I реса соединены с информационными

входами дешифратора 9 нулевого адреса и с адрес}1ыми входами матрицы памяти. Информационные входы и выходы буферного регистра соединены соответственно с информационными выходами матрицы памяти и с первыми ин формацдюнными входам сумматора, вторые информащшнные входы которого подключены к нулевой шине, а инфор- ма1р1онные выходы - к информационным входам матригда памяти.

Формирователь 8 импульсов (фиг. 2 содержит первый 10, второй 11 и третий 12 элементы И-НЕ, инвертор 13 и триггер 1А, тактовый вход которого соединен с выходом первого элемента И-НЕ и является вторым выходом формирователя импульсов, вход асинхронной установки триггера 14 в 1 яв

0

5

0

5

0

5

0

5

ляется ус 1 ан()1К)чным входом формирователя импульсов, инверсный выход триг- ера соединен с перв(,гм входом третьего элемента И-НЕ 12,второй вход ко- тсфого является первым управляющим входом формирователя импульсов, а выход соединен с первыми входами первого 10 и второго 11 элементов И- ПЕ, второй вход первого элемента И-НЕ соединен с выходом инвертора 13, вход которого подключен к синхровходу формирователя импульсов и к второму входу второго элемента И-НЕ, выход которого является первым выходом формирователя импульсов.

Блок 4 установки (фиг. 3) содержит первый 15 и второй 16 триггеры и элемент И 17, выход которого является первым входом блока установки и соединен с информационным входом второго триггера, выход которого является вторым выходом блока установки, а тактовый вход соединен с тактовым входом первого триггера и является синхровходом блока уста- )1овки, первый вход элемента И соединен с выходом первого триггера, а второй вход подключен к информационному входу первого триггера и является информационным входом блока установки.

После включения напряжения питания состояния триггеров 14 и 16, счетчика 5 адреса и матрицы 3 памяти неопределенны.

Состоянием триггера 15 можно пренебречь, так как на шине 2 установки присутствует логический О. Поэтому на первом выходе блока 4 установки создается нулевой уровень, который не мешает работе счетчика 5 адреса.

При подаче на входную шину 1 импульсной последовательности после некоторой серии счетчик 5 адреса становится в положение, соответствующее нулевому состоянию.

Дешифратор 9 выдает импульс нулевого адреса, которьй поступает на тактовый вход триггера 14 формирователя импульсов и тактовый вход триггеров 15 и 16 блока установки.

Допустим, что на инверсном выходе триггера 15 нулевой потенциал. Тогда, учитывая, что на шине 2 уста- })овки, соединенной с информационным D-входом триггера 16, присутствует нулевой потенциал (сигнал установки отсутствует), импульс с дешифратора

51

9 перебрасывает тригт ер 15, но состояние на первом выходе блока установки не изменяется и по-прежнему равно нулевому потенциалу. Если на втором выходе блока А установки (инверсный выход триггера 16) нулевой потенциал, то в момент прихода импульса на тактовый вход триггера 16 на информационном нходе присутствует нулевой потенциал, триггер 16 перебрасывается и на втором выходе блока установки устанавливается высокий потенциал.

Кроме , импульс по установоч- ioNry входу постуттает на формировател 8 импульсов, т.е. на S-вход триггера 1А. Допустим, что триггер 14 в результате воздействия импульса на S-вход устанавливается, т.е. на инверсном выходе появляется нулевой пoтeнн aл.

Высокий уровень с триггера 16 (инверсный выход) поступает на вход элемента И-НЕ 12, а на второй вход этого элемента поступает низкий уровень. На выходе элемента 12 высокий потенциал, который поддерживает в открытом состоянии элементы 10 и 11. На их выходах присутствуют прямая и обратная входная импульсные последовательности.

Во время прохождения импульса нулевого адреса на втором выходе формирователя импульсов присутствует высо

кий уровень, что соответствует режиму считывания из матрицы 3 памят:;, а на первом выходе формирователя S импульсов - низкий ypoFteHb, что соответствует режиму записи в буфер,

ныи регистр 6.

Однако, учитывая, что на втором выходе блока 4 установки логическая 1 на входе переноса сумматора 7 и разрешение работы буферного регистра 6, работу устройства не рассмат- ривают, так как результат в этом случае получается не прогнозируемый. Основным результатом п рассматриваемом варианте является установка триггеров 14, 15, 16,

На шину 2 подают сигнал установки, длительность которого должна быть больше длительности работы счетчика 5.

Поскстльку на инверсном выходе триг гера 15 высокий уровень и сигнал установки характеризуется высоким уровнем, то на выходе элемента И 17 соз

Q

5

0

0

5

0

0

5

736

дается также: нысокиГ) уровень, который сбрасывает счетчик 5, что соответствует его перероду в нулевое состояние. В результате образуется импульс нулевого адреса, который перебрасывает тригг ер 16, триггер 15 (на инверсном выходе - нулевой уровень) и триггер 14 (на инверсном вы- ходе - нулевой уровень).

По окончании дейстния импульса нулевого адреса состояние счетчика 5 адреса не изменяется, буферный регистр 6 находится в обнуленном состоянии, матрица 3 памяти переходит в режим записи, при котором и нулевую ячейку записывается нуль.

По переднему нарастающему фронту первого импульса (входная последовательность с шины 1) счетчик 5 адреса изменяет свое состояние и выставляет адреса первой ячейки.

При этом состояние второго выхода блока 4 установки также не изменяется, состояние буферного регистра 6 обнуленное состояш1е. По окончании действия импульса (в паузе) матрица 3 памяти переходит в режим записи и первая ячейка пpи имaeт О.

Цикл обнуле1шя матриць 3 памяти продолжается в течение времени, определяемого емкостью счетчика 5 адреса и перио;1о« следования входной импульсной последовательности.

Как только счетчик 5 адреса вновь вернется в нулевое состояние, на выходе дешифратора 9 появляется импульс нулевого адреса, который устанавливает высокий уфовень на инверсных нькодах триггеров 15 и 16, так как на информационном входе триггера 15 нулевой уровень.

Высокий уровень на втором вьсходе блока установки снимает потенциал обнуляющий буферньп регистр 6, кроме этого, он соответствует .чог И- ческой 1, действующей на входе переноса сумматора.7.

По окончании действия имнульса нулевого адреса состояние счетчика 5 адреса не изменяется, буферный регистр 6 находится в режиме чтения. Из буферного регистра 6 считывается О. Учитывая 1 на входе переноса, с выхода сумматора 7 1 записывается в ну.чевую ячейку матрицы 3 памяти, так как на ее установочном входе действует низкий потенциал.

,, Рассмотрим состояние, при котором н о Rcex разрядах нулевой ячейки матрицы 3 памяти записаны 1. В момент импульса нуленого адреса происходит считывание из нулевой ячейки и запись в буферный регистр.

По окончании действия импульса нулевого адреса буферный регистр переходит л режим считывания, а матрица п 1мяти - в режим записи, при этом состоят1е счетчика 5 адреса еще не изменилось и соответствует адре- I,-у нулевой ячейки.

Все единицы из буферного регистра 6 поступают на сумматор 7, на входе переноса которого также при- сутствует 1. В результате на выходе переноса появляется 1,а на запись в нулевую ячейку поступают О.

Первый импульс устанавливает счетчик 5 адреса в состояние, соответствующее первой ячейке, переводит триггер 14 формирователя импульсов в состояние, при котором на его инверсном выходе появляется низкий уровень.

Во время действия следующего импульса первая ячейка матрицы 3 памят находится в режиме считывания и отдает О, а буферньш регистр 6 - в режиме записи и пршпчмает эти О.

По окончании действия этого импульса буферный рег истр переходит в режим считывания, а первая ячейка - в-режим записи. Поскольку в буферном регистре 6 - О, на входе переноса сумматора 7 , то на выходе сумматора 7 в М1тадшем разряде присутствует 1, что и записы- выется в первую ячейку.

Счетчик 5 адреса отрабатывает цикл, вновь организуется импульс нулевого адреса, и цикл записи информации в нулевую ячейку до ее заполнения, повторяется.

Формула изобретения

Счетное устройство, содержащее входную шину, 1Ш1ну установки, матри- памяти, счетчик адреса, блок установки, отличающееся тем, что, с целью повышения надежности путем его упрощения, в него введены буферный регистр, сумматор, формирователь импульсов и дешифратор нулевого адреса, выход которого соединен с установочныи входом формирователя импульсов и с синхровходом блока ус

5

0

5

0

5

0

5

0 5

тановки, первый выход которого под- юирчен к установочному входу счетчика адреса, а второй выход - к уста- | новочному входу буферного регистра, входу переноса сумматора и первому управляющему входу формироватапя импульсов, второй управляющий вход которого подключен, к выходу переноса сумматора, щина установки соединена с информационным входом блока установки, входная шина подключена к синхровходам счетчика адреса, дешифратора нулевого адреса и формирователя импульсов, первый выход которого подключен к синхровходу буферного регистра, а второй выход - к входу записи матрицы памяти, информационные выходы счетчика адреса соединены с информационными входами дешифратора нулевого адреса и с адресными входами матрицы памяти, информационные входы и выходы буферного регистра соединены соответственно с информационными выходами матрицы памяти и с первыми информационными входами сумматора, вторые информационные входы которого подключены к нулевой шине, а информационные выходы - к ин- формаи 1онным входам матрицы памяти, причем формирователь импульсов содержит первый, второй и третий элементы И-НЕ, инвертор и триггер, тактовый вход которого соединен с выходом первого элемента И-НЕ и является вторым выходом формирователя импульсов, вход асинхронной установки триггера в 1 является установочным входом формирователя импульсов, инверсный выход триггера соединен с первым входом третьего элемента И-НЕ, второй вход которого является первым управляющим входом формирователя импульсов, а выход соединен с первыми входами первого и второго элементов И-НЕ, второй вход первого элемента И-НЕ соединен с выходом инвертора, вход которого подключен к синхровходу формирователя импульсов и к второму входу второго элемента И-НЕ, выход которого является первым выходом формирователя импульсов, а блок установки содержит в своем составе, первый и второй триггеры и элемент И, выход которого является первым входом блока установки и соединен с информационным входом второго триггера, выход которотю является вторым выходом блока установки, а тактовый

вход соединен с тактовым входом пер- ного триггера и является синхровхо- дом блока установки, первый вход элемента И соединен с выходом первого триггера, а второй вход подключен к информационному входу первого триггера и является информационным входом блока установки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с объектами управления | 1986 |

|

SU1401469A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ КАЧЕСТВА МАГНИТНОГО НОСИТЕЛЯ | 1992 |

|

RU2040050C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ КОРРЕЛЯЦИОННОЙ ФУНКЦИИ | 1992 |

|

RU2037198C1 |

| Станция локальной сети | 1987 |

|

SU1478221A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Формирователь страниц для голографического запоминающего устройства | 1986 |

|

SU1388948A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ МЕСТ ПОВРЕЖДЕНИЯ НАПОРНОГО ТРУБОПРОВОДА | 1992 |

|

RU2046251C1 |

Изобретение относится к импульсной технике и может быть использовано в устройствах обработки цифровой информации. Цель изобретения - повышение надежности устройства. Устройство содержит входную шину 1, шину 2 установки, матрицу 3 памяти, блок 4 установки, счетчик 5 адреса. Введение буферного регистра 6, сумматора 7, формирователя 8 импульсов и дешифратора 9 позволяет увеличить емкость счетного устройства без пропорционального увеличения количества использованных элементов. 3 ил.

I

о

13

и

15

Редактор Н. Гунько

Фиг.З

Составитель П. Смирнов Техред А.Кравчук

i

12

г

/«

Ц3и2.1 И

10

17

16

8

15

Корректор М. Васильева

| но в устройствах обработки цифровой информации | |||

| Цель изобретения - повышение надежности устройства | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-07-07—Публикация

1987-06-16—Подача