(Л

4 со кэ

4

с

О5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отображения векторных диаграмм на экране электронно-лучевой трубки | 1988 |

|

SU1541663A1 |

| Цифровой фазометр | 1986 |

|

SU1368807A1 |

| Устройство для сопряжения цифровой вычислительной машины с каналом связи | 1991 |

|

SU1837301A1 |

| Демодулятор фазоманипулированных сигналов | 1991 |

|

SU1817250A1 |

| Когерентный приемник частотномодулированных сигналов | 1986 |

|

SU1462510A1 |

| Генератор сигналов сложной формы | 1985 |

|

SU1280597A1 |

| Устройство синхронизации | 1988 |

|

SU1644398A1 |

| Цифровой фазометр | 1982 |

|

SU1092430A1 |

| Демодулятор фазоманипулированных сигналов | 1982 |

|

SU1058084A1 |

| Устройство тактовой синхронизации псевдослучайных последовательностей | 1983 |

|

SU1092744A1 |

Изобретение относится к электросвязи. Цель изобретения - повышение достоверности приема. Приемник сигналов трехкратной фазовой манипуляции содержит фазовые детекторы 1-6, логические блоки 7 и 16, дешифратор 8, опорный г-р 9, фазовращатели 10, фильтр 11, сумматоры 12 и 17, перемножители 13 и 14 и блок синхронизации 15. Цель достигается путем правильного определения начальной фазы принимаемого сигнала с помощью введенных блока синхронизации 15, логического блока 16 и сумматора 17. Приемник по пп.2 и 3 отличается выполнением блока синхронизации 15 и логического блока 16. 2 з.п.ф-лы, 3 ил.

ф1/г.

N)

Изобретение относится к технике электросвязи и может испольчоваться в системах радиосвячи, радиотелеметрии и передачи данных и является усовершенствованием изобретения по авт. св. М 632100.

Цель изобретения - повышение достоверности путем правильного определения начальной фазы принимаемого сигнала.

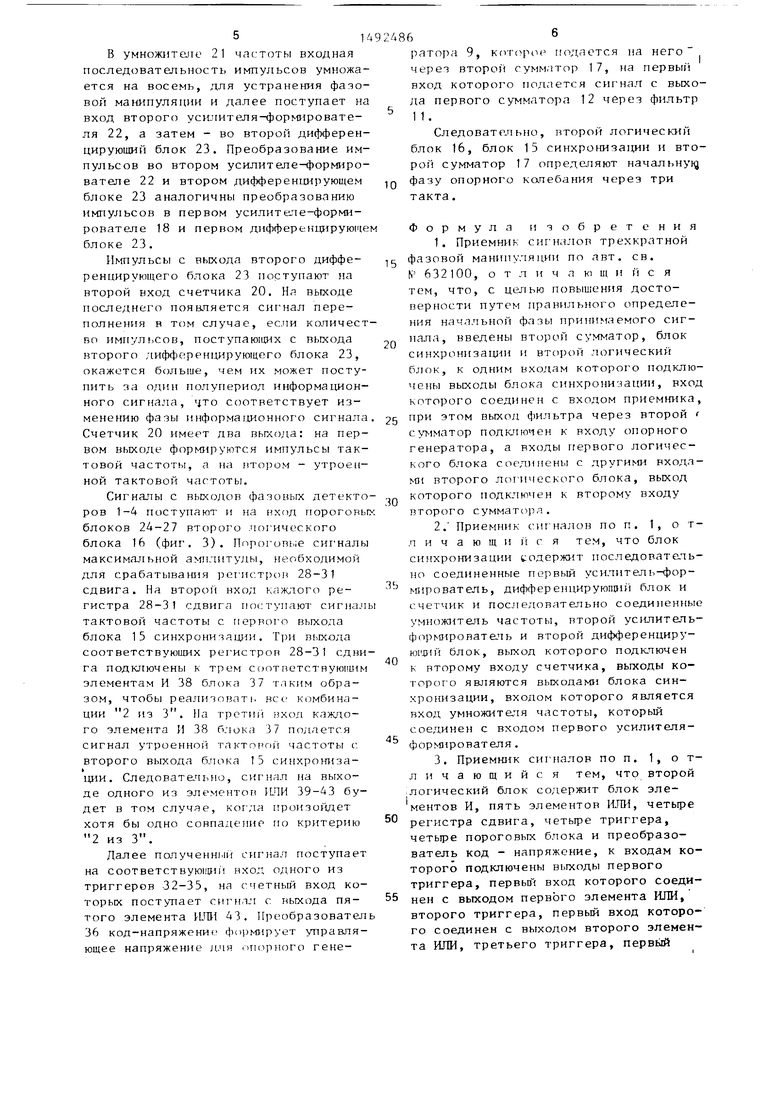

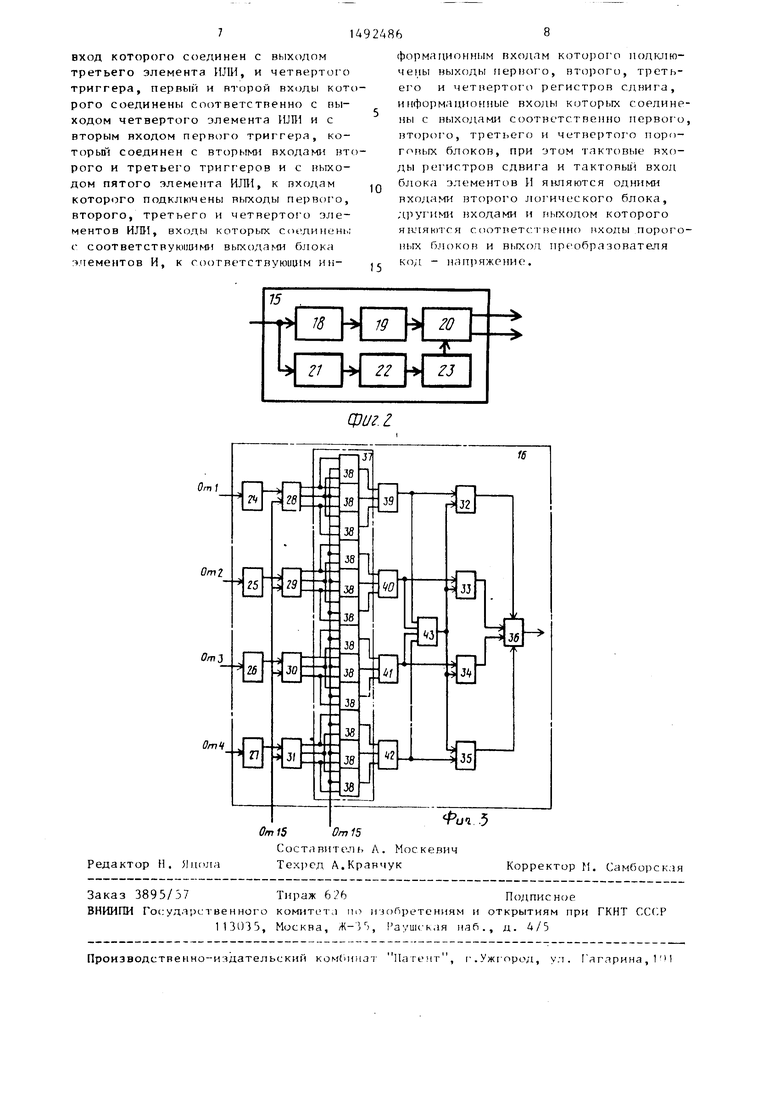

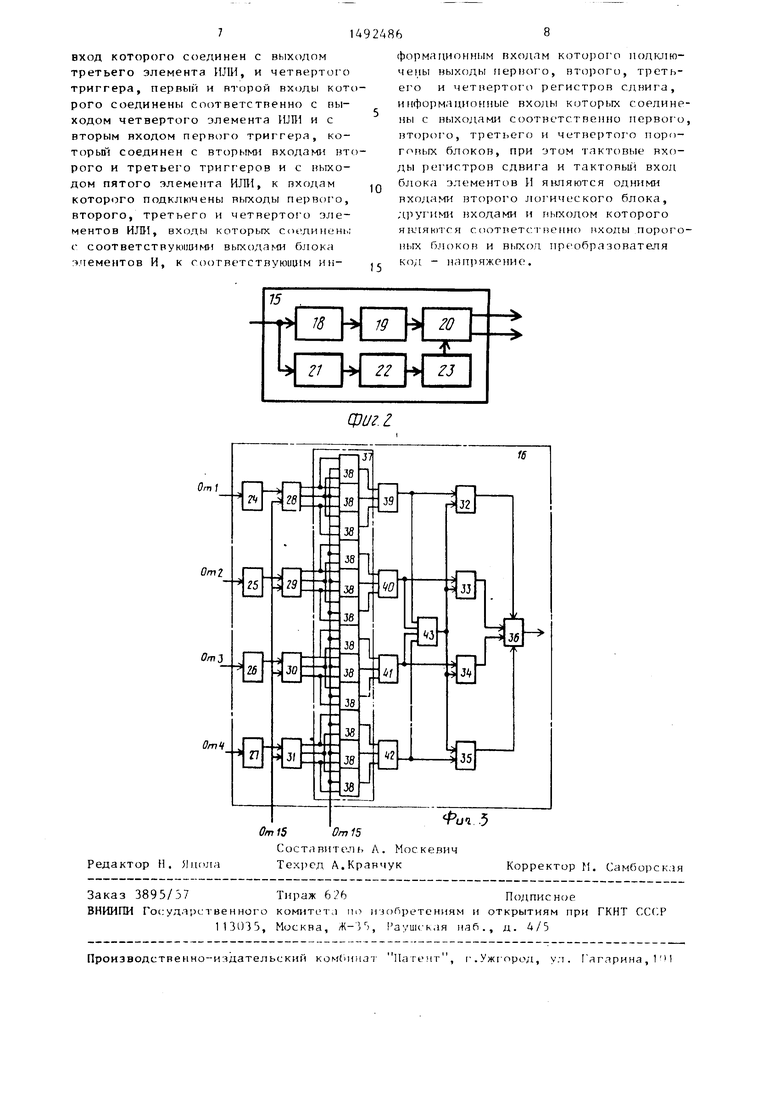

На фиг. 1 представлена структурная г лектрическая схема предлагаемого приемника; на фиг. 2 - блок синхронизации, вариант; на фиг. 3 - BTopofi логический блок, вариант.

Приемник сигналов трехкратно фазовой ма {ипуляции содержит (фиг. 1) шесть фазовых детектором 1-6, iicpEihui логический блок 7, деигиф11атор 8, опорHhoi генератор 9, фазовращатели 10, фильтр 11, первы сумматор 12, первый и BTopoii перемножители 13 и 14, блок 15 синхронизации, второй логический блок 16 и B lopoii сумматор 17.

Блок 15 синхр0101зации (фиг. 2) содержит уси.читель-(1)ор№1рователь 18, первый диф(|)еренш1рую1ции блок 19, счетчик 20, умн(.тжитель 21 частоты, второй yciuinTejiь-(})op п poнaтeль 22 и BTopoti дифферениирукп ЦИ блок 23.

Второй лог ический блок 16 (фиг. 3) содержит чет1-1ре порог овых блока 24- 27, четьфе регистра 28-31 сдвига, первый, второй, трети четвертый триггерь 32-35, 1реобразователь 36 напряжения, блок 37 И 38, первьп , второй, , четверть и пятый элеме Г ы 111111 39-43.

Прием шк рабо .-). с-.,{м образом.

Пусть на ПУ.ОД ( . 1)

поступают . 1 pexKpai Ьазонсм манипуля дии t.

S,(t)

SpCOS(u)t

,),

где S,

и U. - чочио 1звест11ые в ункте I р ема с ооч ветст и е но и час тота .ча;

,8 - СЛ учаЙ1 ЫЙ 1НфОрМа Д10ННЬ Й

параметр сигнала; Ifp- начальная фаза .. Эти сигналы йог (iT на норные входы фазовых дет екторов 1-6, па BTCI- рыс входы i(jI ()1И)1х ncicTynawT .1 с выхода е ератора 9 через фазовращатель 10, .коч орые обеспемиия

ют поворот фазы опориюго колебания на требуемую величину. На выходах фаэовых детекторов 1-4 образуется восемь различных комбинациГ сигналов в зависимости от того, какое значение имеет информационный параметр сигнала. В первом логическом блоке 7 входная комбинаш я сигналов преобразуется в сигнал на одном из его выходов. В дешифраторе 8 зтот сигнал преобразуется н два сигнала вида

cos

р - j sin

(ijiff);

(.).

Эти сигналы поступают на первые входь первого и второ о перемножителей 13 и 14, на вторые входы которых поступают сигналы с выходов фазовых детекторов 5 и 6.

На выходе первого и второго пере- множитедей 13 и 14 формируются сигналы вида

С2 т1-19

и,, cos(i--ff+ +ULf}

/ г- ч «cos(--- ff);

и,. - --cos()Kin(.

244

14

35

суммирования этих сигналс в в 1ервом сумматоре 12 образуется сигнал

и

sin 4 Ч,

5

0

5

где

величина фазы, на которую необходимо построить фазу опорного генератора 9.

Г1оследовате ьность 1м- 1ульсов поступает также на входы пер вого усш ителя-формирователя 18 i умножителя 21 частоть 21 (фиг. 2) блоке 15 синхронизации.

В ервом усил 1теле-формирова геле 18 формируются импульсы с четко вы1)а- женными фронтом и спадом, ными по амплитуде. Эти импульсы поступают на вход первого деффирен Ш15у- ющег о 19, который обеспечивает выпеленив переднего и заднего f фронтов импульсов. Короткие импульсы с выхода первого дифферен 1ирую цего блока 19 поступаю 1 на вход с счетчика 20.

51

В умножителе 21 частоты входная последовательность импульсов умножается на восемь, для устранения фазовой ман {пуляции и далее поступает на вход второго усилителя-формирователя 22, а затем - во второй дифференцирующий блок 23. Преобразование импульсов во втором усилителе-формирователе 22 и втором дифференцирующем блоке 23 аналогичны преобразованию импульсов в первом усилителе-формирователе 18 и первом дифференцирую це бл о к е 23.

И fflyльcы с выхода второго диффе- ренцирующего блока 23 поступают на второй вход счетчика 20. На выходе последнего появляется сигнал переполнения в том случае, если количество импульсов, поступающих с выхода второго дифференцирующего блока 23, окажется больше, чем их может поступить за один полупериод инфopмaп oн- ного сигнала, что соответствует изменению фазы информационного сигнала Счетчик 20 имеет два выхода: на первом выходе формируются импульсы тактовой частоты, а на нтором - утроев - ной тактовой частоты.

Сигналы с выходов фазовых детекторов 1-4 поступают и на ход пороговы блоков 24-27 второго логического блока 16 (фиг. 3). Ппрогопь;е сигналы максимальной амплитуды, необходимой для срабатываю1я рет пстрои 28-31 сдвига. На второй вход каж;1ого ре-

гистра 28-31 сдвига поступают сигнал тактовой частоты с первого выхода блока 15 синхронизации. Три выхода соответствующих регистров 28-31 сдвига подключены к трем соотпетствуюптм элементам И 38 блока 37 таким образом, чтобь реализовать все комбинации 2 из 3. На третиГ }зхол каж,то- го элемента И 38 б. юка 37 подается сигнал утроенной тактовой частоты с

второго выхода блока 15 синхрониза- 1

1ЩИ. Следоватачьно, сигнал на выходе одного из элементог 1ШИ 39-43 будет в том случае, ког да произоГщет хотя бы одно совпадение по критерию 2 из 3.

Далее полученн1.1й сигнал поступает на соответствуюпри ) вход одного из триггеров -32-35, на счетный вход которых поступает с выхода пя- того элемента ИПИ 43. Преобразователь 36 код-напряжение формирует управляющее напряжение для on tip ног о гене

0

2Д

д

i, 25

0

5

0

0

5

866

ратора 9, которое подается на него через BTopoif сумматор 17, на первьи) вход которого подается сигнал с выхода первого сумматора 12 через фильтр 1 1.

Следовательно, второй логический блок 16, блок 15 синхрониза1 д и и второй сумматор 17 определяют начальну фазу опорного колебания через три такта.

Формула изобретения

вход которого соединен с выходом третьего элемента ИЛИ, и четвертого триггера, первый и второй вх(шы KOTti- рого соединены соответственно с выходом четвертого элемента ИЛИ и с вторым входом первого триггера, ко- Topbtfi соединен с вторыми входами второго и третьего триггеров и с выходом пятого элемента ИЛИ, к входам которого подк:тк1чены выходы первого, второго, третьего и четвертого элементов ИЛИ, входы которых соединены с- соответствуюишми вьrxoдa и блока элементов И, к соответствуюицш имOmi

От 2

ОтЗ

От Ч

Редактор И. Япола

От 15От 15

Состав1ггель Л. Москевич

Техред А.КравчукКорректор П. Самборская

формационн1)1м входам которог о подкпю- чеиы выходы tiepnor o, второго, третьего и четвертого регистров сднига, информационные входы которых соединены с в,1ходами соответственно первого, второго, третьего и четвертого поро- гопых блоков, при этом тактовые входы регистров сдвига и тактовьй вход блока элементов И являются одними входами второго логического блока, дl1yги в входами и выходом которого янлянп ся соответственно иходы пороговых блоков и BiiKoJi преобразователя код - напряжение.

фиг.2.

| Приемник сигналов трехкратной фазовой манипуляции | 1976 |

|

SU632100A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1989-07-07—Публикация

1987-10-26—Подача