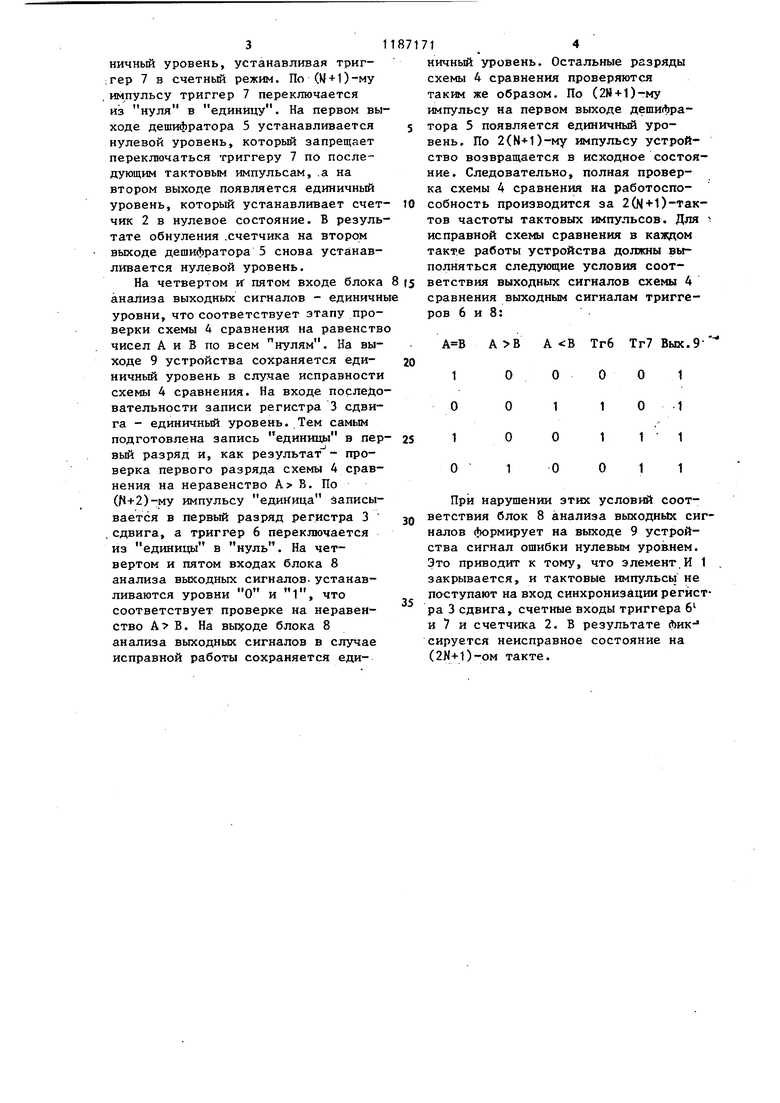

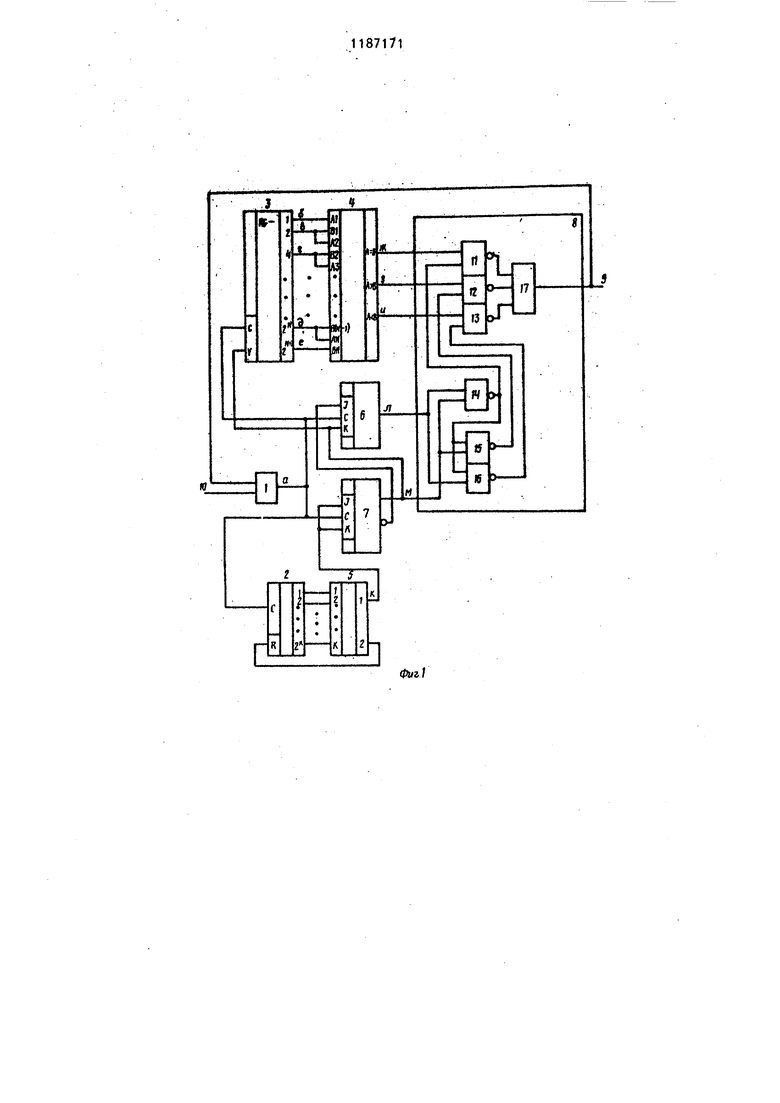

1 Изобретение относится к автомати ке и вычислительной технике и моясет быть использовано для входного конт роля интегральных микросхем, выполняющих функции сравнения чисел, а также при реализации технических средств контроля электронных блоков дискретной автоматики и вычислитель ной техники. Цель изобретения - повьшение про изводительности устройства для конт роля Ы -разрядных схем сравнения двоичных чисел. На Лиг. 1 приведена ф нкциональная схема; на фиг. 2 - временные диаграммы, поясняющие работу устройства. Устройство содержит элемент И 1, :счетчик 2, (N+1)-разрядный регистр сдвига, контролируемую схему 4 Ьрав нения, дешифратор 5, триггеры 6 и 7 блок 8 анализа выходных сигналов, выход 9 устройства и вход 10 тактовых импульсов, четыре элемента ИСКПЮЧА ОЩЕЕ ИЛИ-НЕ 11-14, два элемента И-НЕ 15 и 16 и элемент И 17. Элемент ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ 11-14 элементы И-НЕ 15 и 16 , элемент И 17.. входят в состав блока 8 анализа вУходных сигналов. Выходы 1,2, ..,, N регистра 3 сдвига подключены к первой группе входов контролируемой схемы 4 сравнения, а выходы 2, 3-, ...., (N+1) подключены к второй группе ее входов . Первые же три входа блока 8 анализа выходньпс сигналов подключен к выходам контролируемой схемы 4 сравнения, четвертый и пятьм входы соединены соответственно с прямыми выходами триггеров 6 и 7. Прямой выход триггера 7 подсоединен также к К -входу триггера 6 и входу последовательной записи регистра 3 сдвига. Инверсный вход триггера 7 соединен с 3 -входом триггера 6. Входы 3 и К триггера 7 соединены с первым выходом дешифратора 5. Второй выход дешифратора 5 соединен с R -входом счетчика 2, выходы которого соединены с входами дешифр тора 5. Выход блока В анализа выход ных сигналов подключен к первому входу элемента И 1, разрешая прохож дение тактовых импульсов с шины 10 тактовых импульсов на вход синхрони зации регистра 3 сдвига, счетный 12 вход счетчика 2 и счетные входы Триггеров 6 и 7. Число А поступает на первую группу входов контролируемой схемы 4 сравнения, число В на вторую группу входов. Счетчик 2, триггеры 6 и 7, регистр 3 сдвига изменяют свое состояние по заднему фронту тактового импульса. V ч. Устройство работает следующим образом. В исходном состоянии все разряды регистра 3 сдвига установлены в единичное состояние, а триггеры 6 и 7 и счетчик 2 - в нулевое состояние сигналом Установка (цепь сигнала Установка не показана). На четвертом и пятом входах блока 8 анализа выходных сигналов - нулевые , что соответствует равенству чисел А и В по единицам. На выходе 9 устройства - единичный уровень, сигнализирующий об исправности . контролируемой схемы 4 сравнения и разрешающий прохождение тактовых импульсов через элемент И -1 на счетные входы триггеров 6 и 7, счетчика 2 и вход синхронизации регистра 3 сдвига. На входе последовательной записи регистра 3 сдвига - нулевой уровень, что.является подготовкой записи нуля в первый разряд. По заднему фронту первого тактового импульса в первый разряд регистра записывается нуль, и триггер 6 переключается из нуля в единицу. На четвертом и пятом входе блока 8 анализа выходных сигналов устанавливаются соответственно уровни 1 и О, что соответствует проверке на неравенство . В случае исправности контролируемой схемы 4 сравнения на выходе блок-а 8 анализа В5 1ходных сигналов сохраняется единичный уровень. По заднему фронту второго тактового импульса нуль сдвигается во второй разряд и снова записывается в первый разряд регистра 3 сдвига. Неравенство сохраняется, состояние триггеров 6 и 7 также не изменяется. Таким образом, на каждом такте проверяется один разряд на неравенство А В при равенстве остальных разрядов. Счетчик 2 подсчитывает поступающие импульсы. При поступлении N-ro импульса на первом выходе дешифратора 5 появляется еди-. 3 ничньй уровень, устанавливая триггер 7 в счетньй режим. По (М + О-му импульсу триггер 7 переключается На первом вы из нуля в единицу ходе дешифратора 5 устанавливается нулевой уровень, который запрещает переключаться триггеру 7 по последующим тактовым импульсам, .а на втором выходе появляется единичный уровень, который устанавливает счет чик 2 в нулевое состояние, В резуль тате обнуления .счетчика на втором выходе дешифратора 5 снова устанавливается нулевой уровень. На четвертом к пятом входе блока анализа выходных сигналов - единичн уровни, что соответствует этапу проверки схемы 4 сравнения на равенств чисел А и В по всем нулям. На выходе 9 устройства сохраняется единичный уровень в случае исправности схемы 4 сравнения. На входе последо вательности записи регистра 3 сдвига - единичный уровень. Тем самьм подготовлена запись единиць в пер вьй разряд и, как результат- проверка первого разряда схемы 4 сравнения на неравенство А В. По (М+2)-му импульсу единица записывается в первый разряд регистра 3 сдвига, а триггер 6 переключается из единицы в нуль. На четвертом и пятом входах блока 8 анализа выходных сигналов- устанавливаются уровни О соответствует проверке на неравенство А В. На выводе блока 8 анализа выходных сигналов в случае исправной работы сохраняется еди1 4 ничный уровень. Остальные разряды схемы 4 сравнения проверяются таким же образом. По ()-му импульсу на первом выходе дешифратора 5 появляется единичный уровень. По 2(М+1)-му импульсу устройство возвращается в исходное состояние. Следовательно, полная проверка схемы 4 сравнения на работоспособность производится за 2 (N+1)-тактов частоты тактовых импульсов. Для исправной схемы сравнения в такте работы устройства должны выполняться следующие условия соответствия выходных сигналов схемы 4 сравнения выходным сигналам триггеров 6 и 8: А В Тгб Тг7 Вых.9При нарушении этих условий соответствия блок 8 анализа выходных сигналов формирует на выходе 9 устройства сигнал ошибки нулевым уровнем. Это приводит к тому, что элемент.И 1 закрывается, и тактовые импульсы не поступают на вход синхронизации регистра 3 сдвига, счетные входы триггера 6 и 7 и счетчика 2. В результате фик- сируется неисправное состояние на (2N+1)-oM такте.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления реконфигурацией резервированной вычислительной системы | 1991 |

|

SU1837296A1 |

| Устройство для контроля регистра сдвига | 1980 |

|

SU911530A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

| Устройство для задержки импульсов | 1982 |

|

SU1077046A1 |

| Устройство для задержки импульсов | 1986 |

|

SU1359896A1 |

| Устройство для контроля электронных устройств | 1984 |

|

SU1231505A1 |

| Устройство для возведения в квадрат и извлечения квадратного корня | 1982 |

|

SU1141406A1 |

| Устройство для контроля цифровых блоков | 1984 |

|

SU1238082A1 |

| Многоканальное устройство синхронизации | 1988 |

|

SU1642473A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ N-РАЗРЯДНЫХ СХЕМ СРАВНЕНИЯ, содержащее счетчик, элемент И, дешифратор, два триггера, блок анализа выходных сигналов, причем первый вход элемента И подключен к тактовой шине устройства, выход элемента И соединен со счетным входом счетчика, выход сравнения и два выхода несравнения контролируемой N -разрядной схемы сравнения соединены с первым, вторым, третьим информационными входами блока анализа выходных сигналов соответственно, прямые выходы триггеров соединены с четвертым, пятым информационными входами блока анализа выходных сигналов соответственно, выход которого является выходом ошибки, отличающееся тем, что, с целью повышения производительности путем устранения избыточности комбинаций входных переменных для N -разрядной схемы сравнения, в него введен ()-разрядный регистр сдвига, причем выход блока анализа выходных сигналов соединен с вторым входом элемента И, выход которого объединен с синхровходом (N-fl)-раз рядно го регистра сдвига, синхровходами первого и второго триггеров, информационные выходы счетчика соединены с соответству ющими информационными входами дешифратора, первый выход которого объединен с входами 3 и К первого триггера, второй выход дешифратора соединен с входом обнуления счетчика, прямой выход первого триггера объединен с входом К второго триггера и входом последовательной записи (N+1)-разряд00 ного регистра сдвига, инверсный выход -4 первого триггера соединен с входом второго триггера.

| Устройство для проверки схем сравнения | 1981 |

|

SU1012264A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля схем сравнения | 1981 |

|

SU970377A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-10-23—Публикация

1984-05-18—Подача