Изобретение относится к вычислительной технике и может быть использовано при проектировании мультипроцессорных систем с распределенной магистралью.

Целью изобретения является повышение надежности работы устройства за счет запрета на прохождение запросов .от отказавшего вычислительного блока путем введения режима маскирования запросов, устанавливаемого мажоритарным голосованием.

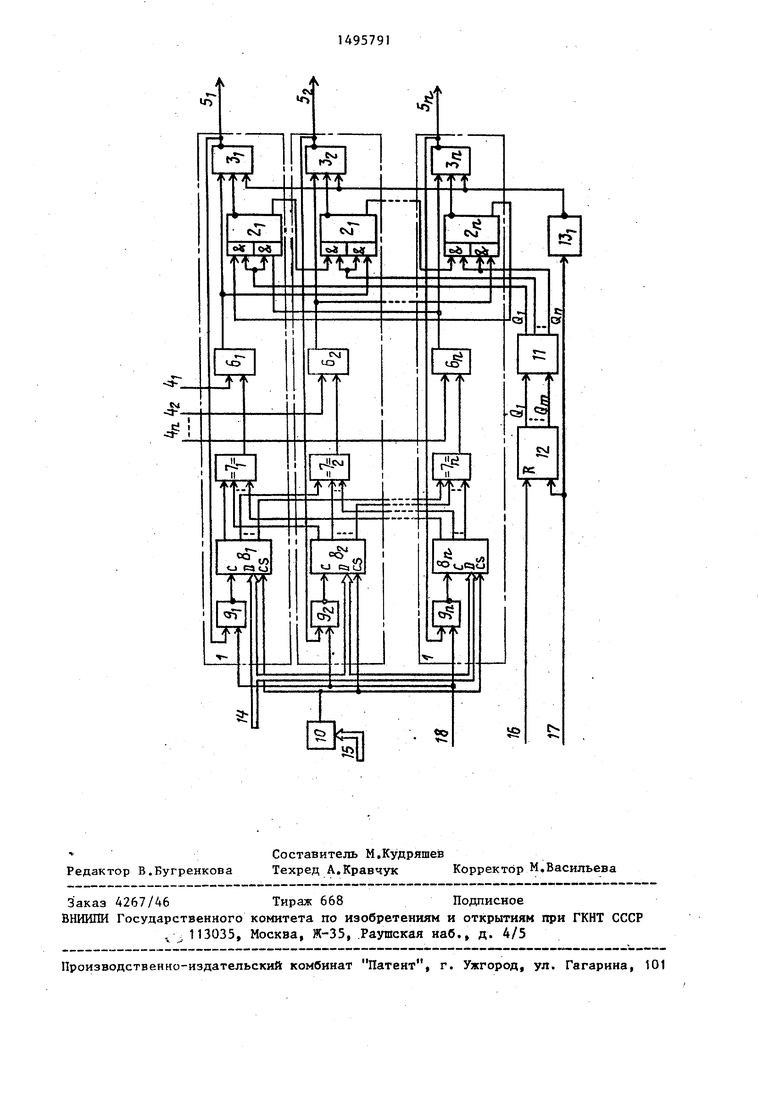

На чертеже представлена структурная схема устройства.

Устройство содержит каналы 1, каждый из которых включает в себя элемент И-ИЛИ 2, элемент И-НЕ 3, вход 4 запросов устройства, выход 5 разрешения устройства, элемент И 6, мажори- тарный элемент 7, регистр 8, элемент ИЛИ-НЕ 9. Устройство содержит также дешифраторы 10 и I Г, счетчик 12, элемент НЕ 13, группу информационных входов 14 устройства, группу адресных входов 15 устройства, вход-16 сброса устройства, вход 17 захвата системной магистрали устройства вход 18 записи устройства.

4

со

СП

Ssl

со

Устройство работает следующим образом.

Установка устройства в исходное состояние осуществляется с приходом сигнала на вход 16. При этом счетчик 12 устанавливается в нулевое состояние. Произвольная комбинация сигналов, присутствуняцих в исходном состоянии на входах мажоритарньтх эле- 10 противном случае

вается новая комбин водит к появлению н следующем по старши шифратора 11 . Если поступит запрос и о ван, то на выходе 5

низкий уровень и ос служивание запроса

запрос очередного п нала. В зависимости ходов дешифратора налов изменяется по

ментов 7 всех каналов, приводит к , формированию на их выходах сигналов высокого уровня, что разрешает про- хождение сигналов запроса на пользование распределенной системой магист-15 ралью через элементы И 6, Сигналы запроса, поступающие на входы 4,име- .ют активный высокий уровень. Формирование сигнала запроса осуществляется тем вычислительным блоком, которому необходимо обращение к распределенной системой магистрали.

Сигналы запроса через элементы И 6 поступают на входы комбинационной схемы, состоящей из элементов И-ИЛИ 2, и на выходы элементов И-НЕ 3. Кодовая комбинация,присутствующая на выходе счетчика 12 после установки.в исходное состояние,при20

25

обслуживается запрос очередного по старшинству ка нала. В зависимости от состояния вы ходов дешифратора 11 приоритет каналов изменяется по циклу.

При отсутствии сигналов запроса на вjtoдax 4 и наличии Низкого уровн на любом выходе дешифратора на инверсных выходах элементов И-ИЛИ 2 всех каналов и на всех выходах 5 ус тановятся высокие уровни, запрещающие доступ к распределенной системной магистрали всем процессорам. Если нав ды 4 одновременно поступят сигналы запроса и ранее данные запросы не были замаскированы, т.е. обеспечено их прохождение через элементы И 6, то на инверсном выходе элемента И-ИЛИ 2 канала 1, на которьгй поступает низкий уройень с дешифратора 1

водит к формированию на младшем выхо- О устанавливается высокий уровень, а де дешифратора П сигнала низкого уровня, который поступает на второй и третий входы элемента И-ИЛИ 2 канала 1 . Комбинационная схема органа инверсных выходах элементов И-ЙЛИ 2 остальных каналов - низкие уровни. При низком уровне на входе на выходе 5 разрешения данного кана ла сформируется сигнал с активным низким уровнем, разрешающим достзш к распределенной системной магистр ли вычислительному блоку, к котором подключен данный выход.разрешения,

низована таким образом, что после установки в исходное состояние на- ивысший приоритет присваивается каналу с наименьшим номером. Если на вход 4 запроса на пользование распределенной системной магистралью по- йтзшит сигнал высокого уровня и ранее данный запрос не бьт замаскиро- ван, т.е. обеспечено прохождение сигнала логической единицы через элемент И 6( на входы элемента И-НЕ 3 , то на инверсном выходе элемента И-ИПИ 2 устанавлива:ется уровень ло- гиче ской единицы, а на инверсных выходах элементов И-ШШ 2 остальных каналов - уровни логического нуля, При низком уровне на входе 17 на выходе 5;, сформируется сигнал с активным низким уровнем, разрешающим до- ступ к распределенной системной магистрали. Обслуживание данного запроса продолжается до проявления на входе 17 сигнала высокого уровня. С приходом этого сигнала на счетный вход счетчика 12 на его выходе устанавли0 противном случае

вается новая комбинация, которая приводит к появлению низкого уровня на следующем по старшинству выходе де- , шифратора 11 . Если теперь на вход 4 поступит запрос и он не замаскирован, то на выходе 5- устанавливается

5

0

5

низкий уровень и осуществляется обслуживание запроса данного канала.

обслуживается запрос очередного по старшинству канала. В зависимости от состояния выходов дешифратора 11 приоритет каналов изменяется по циклу.

При отсутствии сигналов запроса на вjtoдax 4 и наличии Низкого уровня на любом выходе дешифратора на инверсных выходах элементов И-ИЛИ 2 всех каналов и на всех выходах 5 установятся высокие уровни, запрещающие доступ к распределенной системной магистрали всем процессорам. Если ды 4 одновременно поступят сигналы запроса и ранее данные запросы не были замаскированы, т.е. обеспечено их прохождение через элементы И 6, то на инверсном выходе элемента И-ИЛИ 2 канала 1, на которьгй поступает низкий уройень с дешифратора 11,

устанавливается высокий уровень, а

на инверсных выходах элементов И-ЙЛИ 2 остальных каналов - низкие уровни. При низком уровне на входе 17 на выходе 5 разрешения данного канала сформируется сигнал с активным низким уровнем, разрешающим достзш к распределенной системной магистрали вычислительному блоку, к которому подключен данный выход.разрешения,

При необходимости маскирования запросов одного из вычислительных блоков на группе входов 15 устанавливается комбинация сигналов, по которой на выходе дешифратора 10 появляется сигнал низкого уровня, который поступает на входы управления записью регистров 8 Одновременно на группе блоков 14 появляется слово маски С высоким уровнем в разряде, равном Номеру отказавшего вычислительного блока, и низким уровнем в остальные разрядах (позиционный код). Данное слово маски захшсывается в тот регистр, на стробйруищий вход которого приходит сигнал высокого уровня. Ус-i ловием формирования стробйрующего сигнала является наличие низкого уровня на; соответствующем выходе 5. н

низкого уровня на входе 18. Для получения достоверного результата при голосовании посредством мажоритарного элемента достаточно совпадения

I

слов маски от вычислительных

блоков, выполнявших идентичные вычисления. При этом на выходе мажоритарного элемента 7 соответствующего канала формируется низкий уровень, запрещающий прохождение запросов от отказавшего вычислительного блока.

Формула изобретения

Устройство приоритета, содержащее элеме1 т НЕ, счетчик, первый дешифратор, каналы, каждый из которых содержит элемент И-ИЛИ, элемент И-НЕ причем в каждом канале первый вход элемента И-НЕ соединен с инверсным выходом элемента И-ИЛИ, прямой выход которого соединен с первым входом элемента И-ИЛИ следующего канала, прямой выход элемента И-ШШ последнего канала соединен с первьм входом элемента И-ИЛИ первого канала, вход захвата системной магистрали устройства подключен к входу элемента НЕ и к счетному входу счетчика, вход .сброса которого соединен с входом сброса устройства, группа выходов .счетчика соединена с группой входов дешифратора, каждый i-й (i ,...,п п - число запросов) выход которого соединен с вторьм и третьим входами элемента И-ИПИ i-ro канала, выход элемента НЕ соединен с вторым входом элемента И-НЕ каждого канала, выходы

которых являются соответствукшщми вы- 40 дом элемента И-НЕ своего канала,выходами разрешения устройства, о т - ход которого соединен с первым вхо- личающееся тем, что, с дом элемента ИЛИ-НЕ своего канала.

целью повьшения надежности работы устройства за счет запрета на прохождение запросов от отказавшего вычислительного блока путем введения режима маскирования запросов, устанавливаемого мажоритарным голосованием, в устройство введен второй дешифратор, а каждый канал содержит элемент

0 ИЛИ-НЕ, регистр, мажоритарный элем мент И, причем группа входов второго дешифратора соединена с группой адресных входов устройства, выход второго дешифратора соединен с входом

5 управления записью регистра каждого канала, группа входов которого подключена к группе информационных входов устройства, одноименные выходы. . регистров подключены к входам ритарных элементов одноименных каналов , выход мажоритарного элемента соединен с первьм входе элемента И своего канала, второй вход которого является входом запросов устройства,

5 выход элемента И каждого канала,кроме последнего, соединен с четвертые входом элемента И-ИЛИ следующего канала и с третьим входом элемента И-НЕ своего канала, выход которого

0 подключен к первому входу элемента ИЛИ-НЕ своего канала, вторые входы элементов ИЛИ-НЕ всех каналов объединены и соединены с входом записи устройства, выход элемента ИЛИ-НЕ

5 каждого канала подключен к тактовому входу регистра своего канала, вы ход элемента И последнего канала соединен с четвертым вход(4 элемента И-ИЛИ rfepBoro канала и с третьим вхо

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для арбитража запросов | 1988 |

|

SU1596329A1 |

| Устройство для обнаружения ошибок при передаче информации | 1988 |

|

SU1596333A1 |

| Устройство управления передачей информации в резервированной многопроцессорной вычислительной системе | 1988 |

|

SU1562923A1 |

| Многоканальное устройство приоритета | 1979 |

|

SU822185A1 |

| Процессор для мультипроцессорной системы | 1988 |

|

SU1541626A1 |

| ОТКАЗОУСТОЙЧИВАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА С АППАРАТНО-ПРОГРАММНОЙ РЕАЛИЗАЦИЕЙ ФУНКЦИЙ ОТКАЗОУСТОЙЧИВОСТИ И ДИНАМИЧЕСКОЙ РЕКОНФИГУРАЦИИ | 2010 |

|

RU2455681C1 |

| Устройство для управления режимамиОбМЕНА РЕзЕРВиРОВАННОй СиСТЕМы | 1979 |

|

SU849216A1 |

| Многоканальное устройство для распределения заданий процессорам | 1987 |

|

SU1471191A1 |

| Мажоритарно-резервированный интерфейс памяти | 1990 |

|

SU1751766A1 |

| Мажоритарно-резервированный интерфейс памяти | 1990 |

|

SU1702434A1 |

Изобретение относится к вычислительной технике и может быть использовано при проектировании мультипроцессорных систем с распределенной магистралью. Цель изобретения состоит в повышении надежности в работе устройства за счет запрета на прохождение запросов от отказавшего вычислительного блока путем введения режима маскирования запросов, устанавливаемого мажоритарным голосованием. Устройство приоритета содержит каналы, каждый из которых включает в себя элемент И-ИЛИ, элемент И-НЕ, элемент И, мажоритарный элемент, регистр, элемент ИЛИ-НЕ, два дешифратора, счетчик и элемент НЕ. При необходимости маскирования запросов одного из вычислительных блоков на распределенной системной магистрали адреса устанавливается комбинация сигналов, по которой на выходе дешифратора появляется сигнал низкого уровня, который поступает на C-входы разрешения регистров. Одновременно появляется на распределенной системной магистрали данных слово маски с высоким уровнем в разряде, равном номеру отказавшего вычислительного блока, и низким уровнем в остальных разрядах. 1 ил.

| Устройство управления магистралью | 1977 |

|

SU717770A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| ,(54) УСТРОЙСТВО ПРИОРИТЕТА | |||

Авторы

Даты

1989-07-23—Публикация

1987-09-22—Подача