со

о со

31А97709

Изобретение относится к радиотехнике и может быть использовано для формирования линейно-частотно-моду- лированных сигналов в системах радиосвязи, радионавигации и измерительной техники„

Цель изобретения - увеличение девиации частоты.

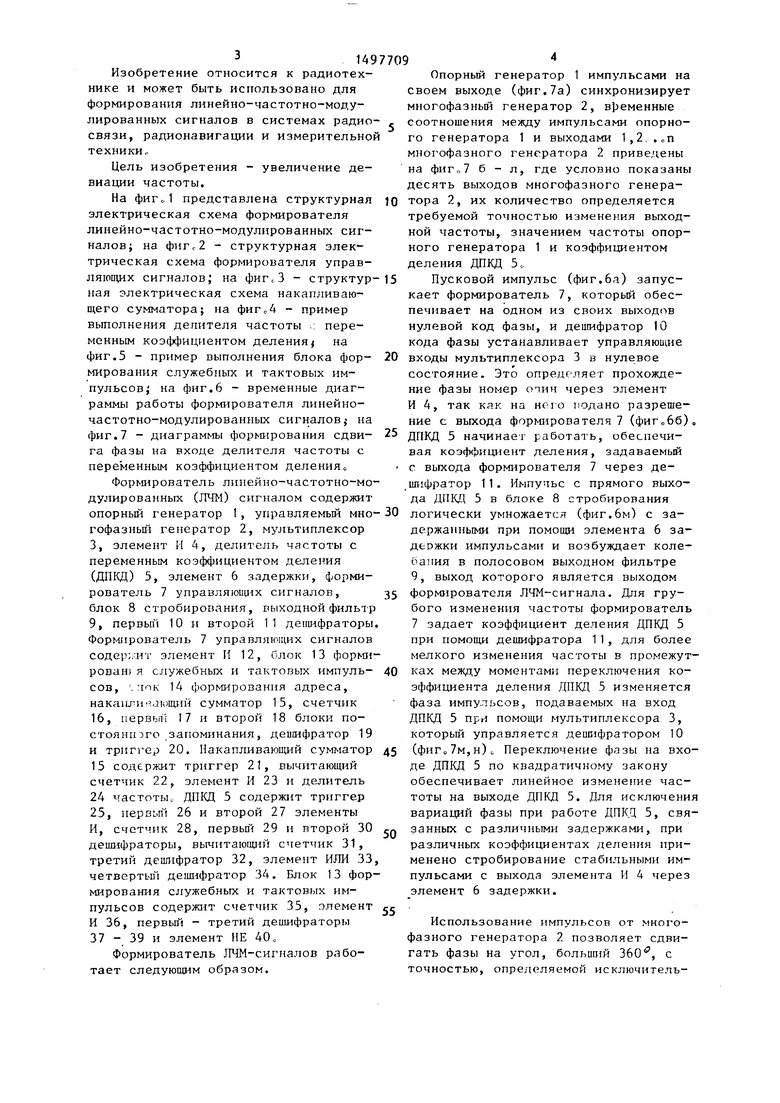

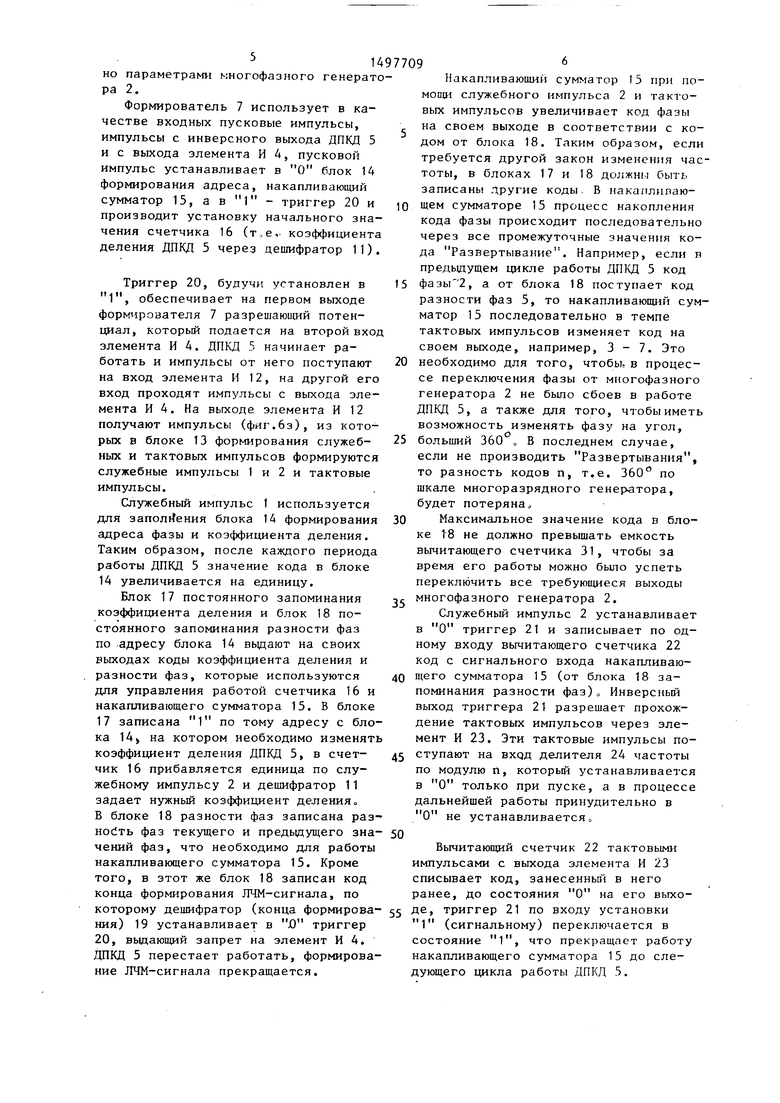

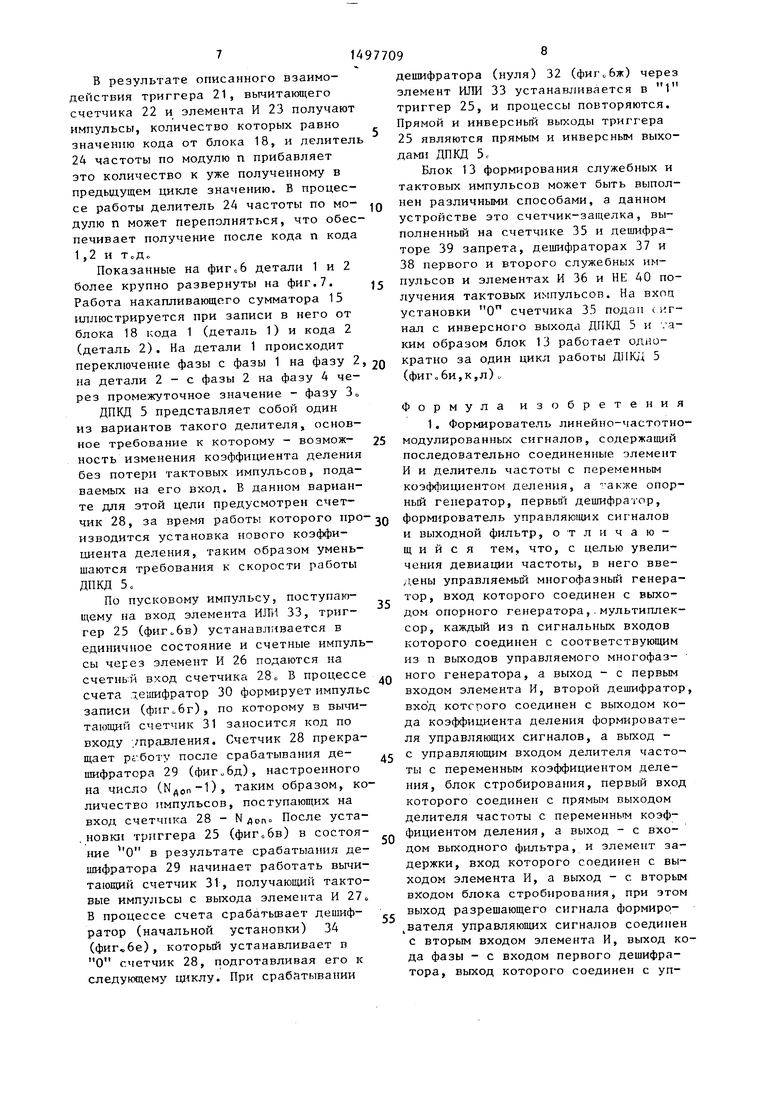

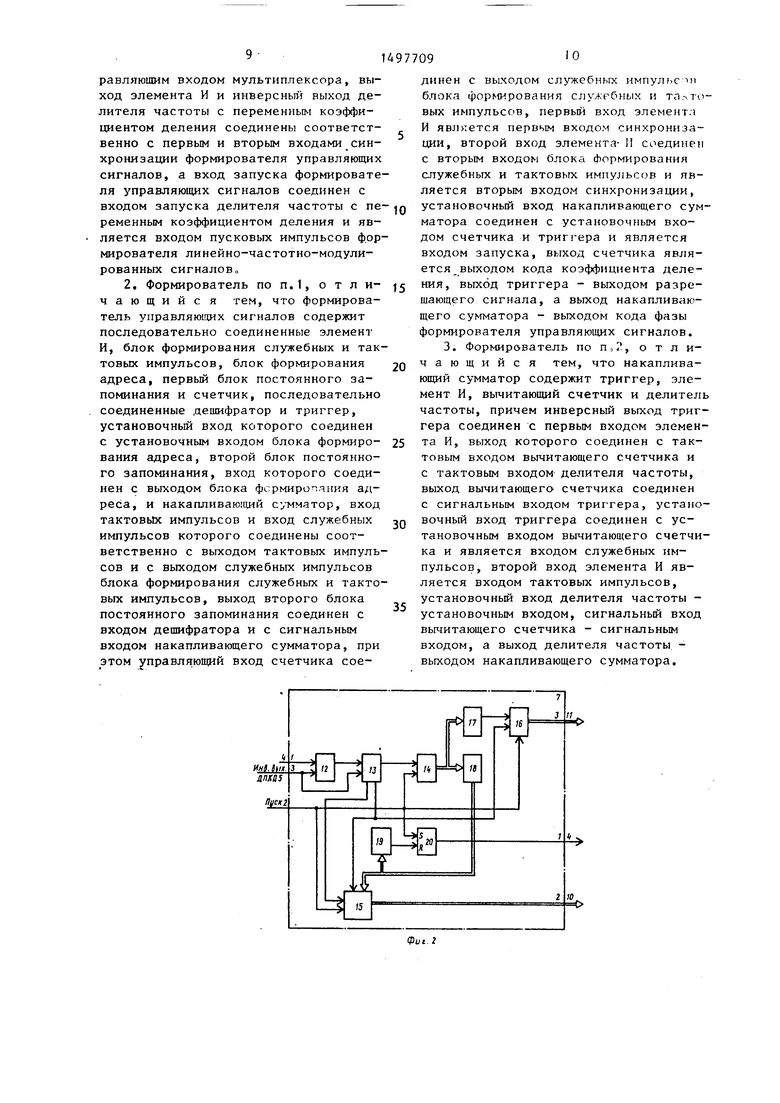

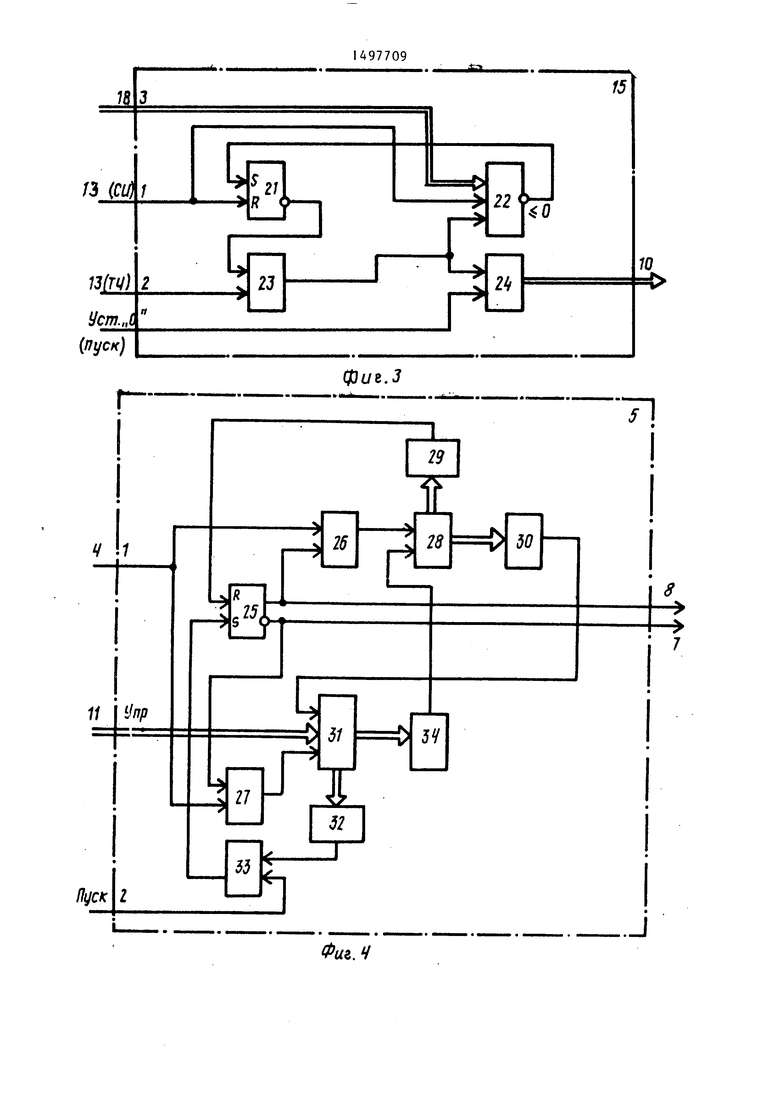

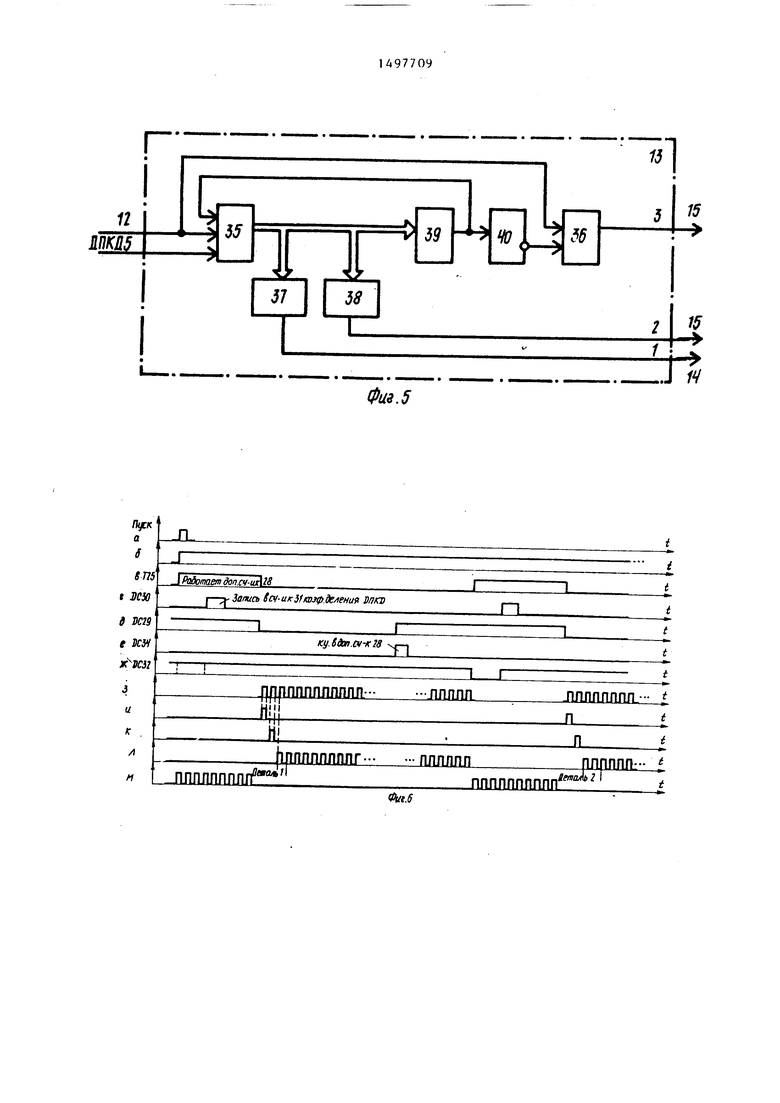

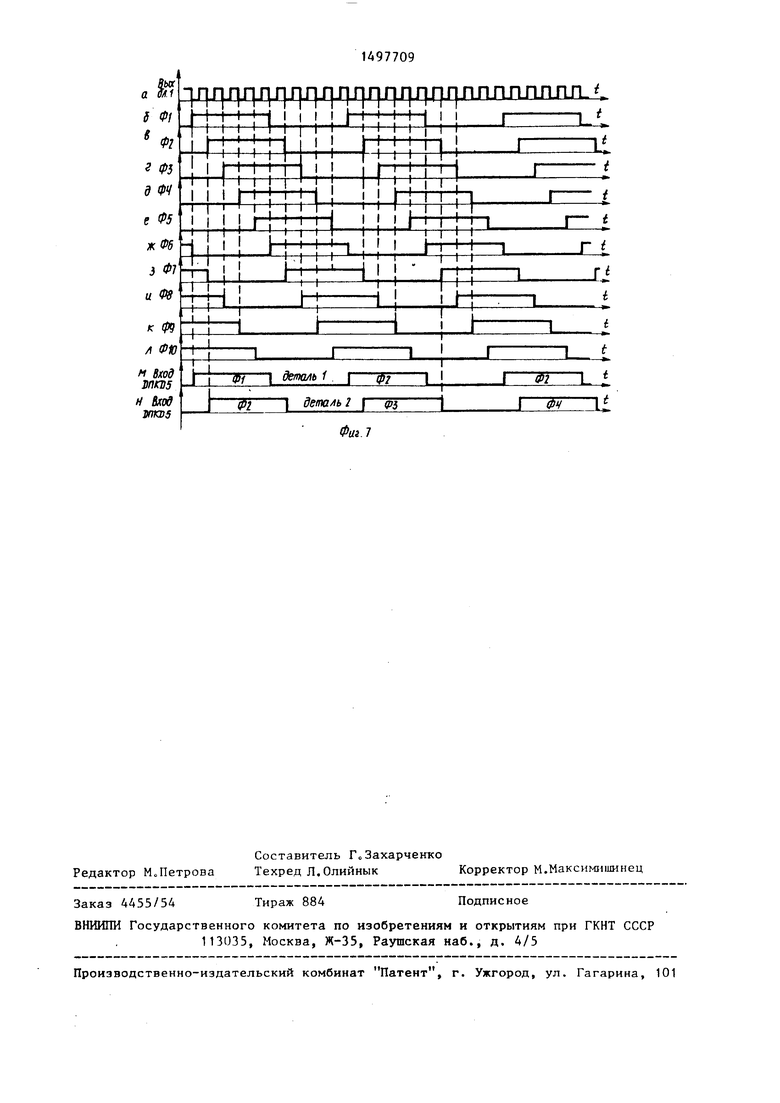

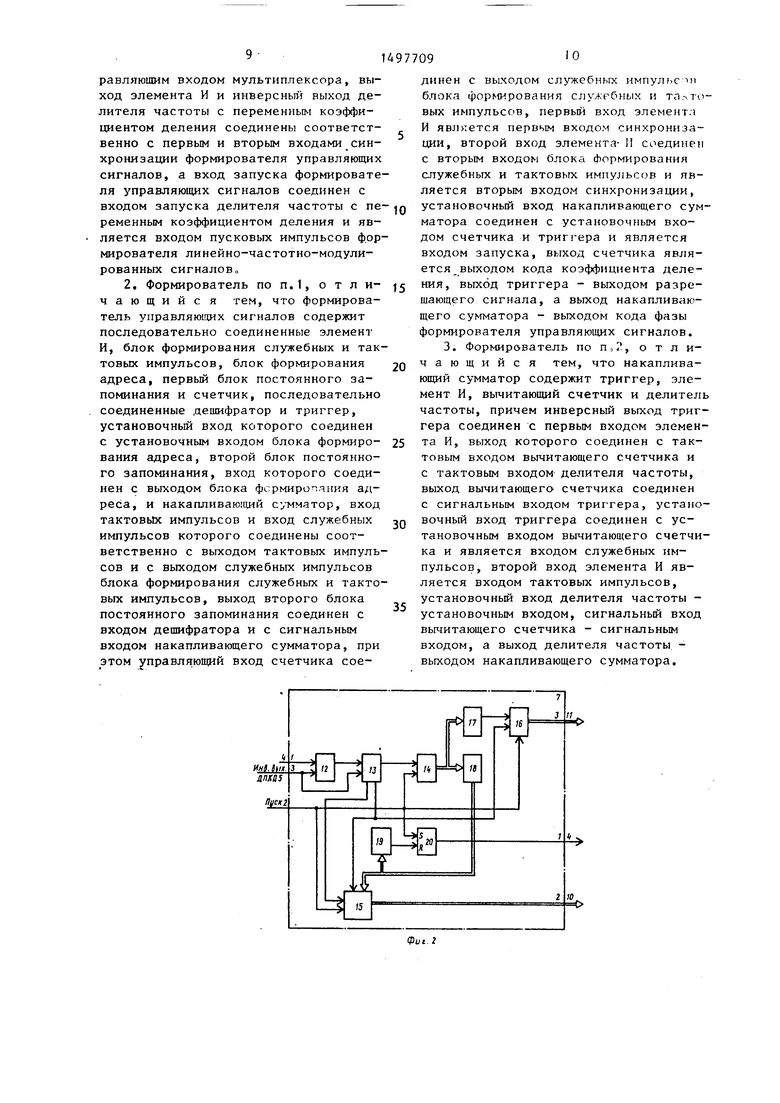

На фигс, представлена структурная ю электрическая схема формирователя линейно-частотно-модулированных сигналов; на фиг с 2 - структурная электрическая схема формирователя управ- ЛЯЮ1ДИХ сигналов; на фиГсЗ - структурпая электрическая схема накапливающего сумматора; на фиг о 4 - пример вьтолнения делителя частоты ,: переменным коэффищгентом деления j на фиг.5 - пример выполнения блока фор- мирования служебных и тактовых импульсов на фиг.6 - временные диаграммы работы формирователя линейно- частотно-модулированных сигналовJ на фиг.7 - диаграммы форкшрования сдви- га фазы на входе делителя частоты с переменным коэффициентом деления

Формирователь линейно-частотно-модулированных (ЛЧМ) сигналом содержит

опорный генератор 1, управляемый мно-30 логически умножается (фиг.6м) с за- гофазньш генератор 2, мультиплексор 3, элемент И 4, делитель частоты с переменным коэффициентом деления (ДПКД) 5, элемент 6 задержки, формирователь 7 управляюиц1х сигналов, - блок 8 стробирования, выходной филь7 р 9, первый 10 и второй 11 дешифраторы. Формирователь 7 управляющих сигналов содер;;сит элемент И 12, блок 13 формидержанными при помощи элемента 6 задержки импульсами и возбуждает колебания в полосовом выходном фильтре 9, выход которого является выходом формирователя ЛЧМ-сигнала. Для грубого изменения частоты формирователь 7 задает коэффициент деления ДПКД 5 при помощи дешифратора 11, для более мелкого изменения частоты в промежут ках между моментами переключения коэффициента деления ДПКД 5 изменяется фаза импульсов, подаваемых на вход ДПКД 5 при помощи мультиплексора 3, которьш управляется дешифратором 10 (фиг57м,н)с Переключение фазы на вхо де ДПКД 5 по квадратичному закону обеспечивает линейное изменение частоты на выходе ДПКД 5. Для исключени вариаций фазы при работе ДПКД 5, свя занных с различными задержками, при различных коэффициентах деления применено стробирование стабильными импульсами с выхода элемента И 4 через элемент 6 задержки.

рован я служебных и тактовых импуль- сов, -лок 14 формирования адреса, нака1ич1 ча ощий сумматор 15, счетчик 16, iiepBbii i 17 и второй 18 блоки по- стояниэго запоминания, деиифратор 19 и триггер 20. Накапливающий сумматор 15 содержит триггер 21, вычитающий счетчик 22, элемент И 23 и делитель 24 частоты. ДПКД 5 содержит триггер 25, первьт 26 и второй 27 элементы И, счетчик 28, первьш 29 и второй 30 дешифраторы, вычитающий счетчик 31, третий дешифратор 32, элемент ИЛИ 33, четвертьш дешифратор 34. Блок 13 формирования служебных и тактовых импульсов содержит счетчик 35, элемент И 36, первьш - третий дешифраторы 37 - 39 и элемент НЕ 40.

Формирователь ЛЧМ-сигналов работает следуюшим образом.

Опорный генератор 1 импульсами на своем выходе (фиг.7а) синхронизирует многофазный генератор 2, в1 еменные соотношения между импульсами опорного генератора 1 и выходами 1,2,.„п многофазного генератора 2 приведены на фиг о 7 б - л, где условно показаны десять выходов многофазного генератора 2, их количество определяется требуемой точностью изменения выходной частоты, значением частоты опорного генератора 1 и коэффициентом деления ДПКД 5.

Пусковой импульс (фиг.ба) запускает формирователь 7, который обеспечивает на одном из своих выходов нулевой код фазы, и дешифратор 10 кода фазы устанавливает управляющие входы мультиплексора 3 в нулевое состояние. Это определяет прохождение фазы номер тин через элемент И А, так как на него подано разрешение с выхода формирователя 7 (фигобб) ДПКД 5 начинает работать, обеспечивая коэффициент деления, задаваемьй с выхода формирователя 7 через дешифратор 11. Импупьс с прямого выхода ДПКД 5 в блоке 8 стробирования

логически умножается (фиг.6м) с за-

держанными при помощи элемента 6 задержки импульсами и возбуждает колебания в полосовом выходном фильтре 9, выход которого является выходом формирователя ЛЧМ-сигнала. Для грубого изменения частоты формирователь 7 задает коэффициент деления ДПКД 5 при помощи дешифратора 11, для более мелкого изменения частоты в промежутках между моментами переключения коэффициента деления ДПКД 5 изменяется фаза импульсов, подаваемых на вход ДПКД 5 при помощи мультиплексора 3, которьш управляется дешифратором 10 (фиг57м,н)с Переключение фазы на входе ДПКД 5 по квадратичному закону обеспечивает линейное изменение частоты на выходе ДПКД 5. Для исключения вариаций фазы при работе ДПКД 5, связанных с различными задержками, при различных коэффициентах деления применено стробирование стабильными импульсами с выхода элемента И 4 через элемент 6 задержки.

Использование импульсов от многофазного генератора 2 позволяет сдвигать фазы на угол, больишй , с точностью, определяемой исключитель 149

но параметрами многофазного генератора 2.

Формирователь 7 использует в качестве входных пусковые импульсы, импульсы с инверсного выхода ДПКД 5 и с выхода элемента И Д, пусковой импульс устанавливает в О блок 14 формирования адреса, накапливающий сумматор 15, а в 1 - триггер 20 и производит установку начального значения счетчика 16 (т,е,. коэффициента деления ДПКД 5 через дешифратор 11).

Триггер 20, будучи установлен в 1, обеспечивает на первом выходе формирователя 7 разрешающий потенциал, который подается на второй вход элемента И 4. ДПКД 5 начинает работать и импульсы от него поступают на вход элемента И 12, на другой его вход проходят импульсы с выхода элемента И 4. На выходе элемента И 12 получают импульсы (фиг.бз), из которых в блоке 13 формирования служебных и тактовых импульсов формируются служебные импульсы 1 и 2 и тактовые импульсы.

Служебный импульс 1 используется для зaпoл feния блока 14 формирования адреса фазы и коэффициента деления. Таким образом, после каждого периода работы ДПКД 5 значение кода в блоке 14 увеличивается на единицу.

Блок 17 постоянного запоминания коэффициента деления и блок 18 постоянного запоминания разности фаз по адресу блока 14 выдают на своих выходах коды коэффициента деления и разности фаз, которые используются для управления работой счетчика 16 и накапливающего сумматора 15. В блоке 17 записана 1 по тому адресу с блока 14 на котором необходимо изменят коэффициент деления ДПКД 5, в счетчик 16 прибавляется единица по служебному импульсу 2 и дешифратор 11 задает нужный коэффициент деления В блоке 18 разности фаз записана раз нойть фаз текущего и предьщущего зна чений фаз, что необходимо для работы накапливающего сумматора 15. Кроме того, в этот же блок 18 записан код

Вычитающий счетчик 22 тактовыми импульсами с выхода элемента И 23 списывает код, занесенньв1 в него ранее, до состояния О на его выхоконца формирования ЛЧМ-сигнала, по

которому дешифратор (конца формирова- 55 триггер 21 по входу установки

ния) 19 устанавливает в Д триггер 1 (сигнальному) переключается в

20, вьдающий запрет на элемент И 4.состояние 1, что прекращает работу

ДПКД 5 перестает работать, формирова-накапливающего сумматора 15 до сление ЛЧМ-сигнала прекращается.дующего цикла работы ДПКД 5.

0

5

0

0

0

Накапливающий сумматор 15 при помощи служебного импульса 2 и тактовых импульсов увеличивает код фазы на своем выходе в соответствии с кодом от блока 18. Таким образом, если требуется другой закон изменения частоты, в блоках 17 и 18 должн - быть записаны другие коды, В накапливающем сумматоре 15 процесс накопления кода фазы происходит последовательно через все промежуточные значения кода Развертывание. Например, если я предыдущем цикле работы ДПКД 5 код фазы 2, а от блока 18 поступает код разности фаз 5, то накапливающий сумматор 15 последовательно в темпе тактовых импульсов изменяет код на своем выходе, например, 3-7. Это необходимо для того, чтобы, в процессе переключения фазы от многофазного генератора 2 не было сбоев в работе ДПКД 5, а также для того, чтобы иметь возможность изменять фазу на угол,

5 больший 360 g В последнем случае, если не производить Развертывания, то разность кодов п, т.е. 360° по шкале многоразрядного генератора, будет потеряна о

Максимальное значение кода в блоке 18 не должно превышать емкость вычитающего счетчика 31, чтобы за время его работы можно было успеть переключить все требующиеся выходы многофазного генератора 2.

Служебный импульс 2 устанавливает в О триггер 21 и записывает по одному входу вычитающего счетчика 22 код с сигнального входа накапливающего сумматора 15 (от блока 18 запоминания разности фаз)о Инверсный выход триггера 21 разрешает прохождение тактовых импульсов через элемент И 23. Эти тактовые импульсы по5 ступают на вход делителя 24 частоты по модулю п, который устанавливается в О только при пуске, а в процессе дальнейшей работы принудительно в О не устанавливается

5

0

Вычитающий счетчик 22 тактовыми импульсами с выхода элемента И 23 списывает код, занесенньв1 в него ранее, до состояния О на его выхов результате описанного взаимодействия триггера 21, вычитающего счетчика 22 и элемента И 23 получают импульсы, количество которых равно значению кода от блока 18, и делител 24 частоты по модулю п прибавляет это количество к уже полученному в предыдущем цикле значению. В процессе работы делитель 2А частоты по мо- дулю п может переполняться, что обеспечивает получение после кода п кода 1,2 и т о д о

Показанные на детали 1 и 2 более крупно развернуты на фиг.7. Работа накапливающего сумматора 15 иллюстрируется при записи в него от блока 18 кода 1 (деталь 1) и кода 2 (деталь 2). На детали 1 происходит переключение фазы с фазы 1 на фазу 2 на детали 2-е фазы 2 на фазу 4 через промежуточное значение - фазу 3

ДПКД 5 представляет собой один из вариантов такого делителя основное требование к которому - возмож- ность изменения коэффициента деления без потери тактовых импульсов, подаваемых на его вход. В данном варианте для этой цели предусмотрен счетчик 28, за время работы которого про изводится установка нового коэффициента деления, таким образом уменьшаются требования к скорости работы ДПКД 5.

По пусковому импульсу, поступающему на вход элемента ИЛИ 33, триггер 25 (фиг„6в) устанавливается в единичное состояние и счетные импульсы через элемент И 26 подаются на счетнь й вход счетчика 28 В процессе счета дешифратор 30 формирует импуль записи (фиг.бг), по которому в вычитающий счетчик 31 заносится код по входу /правления. Счетчик 28 прекращает рсботу после срабатывания дешифратора 29 (фигобд), настроенного на число (), таким образом, количество импульсов, поступающих на вход счетчика 28 - После уста- ,новки триггера 25 (фиг.бв) в состоя

ние О в результате срабатыания дешифратора 29 начинает работать вычитающий счетчик 31, получающие тактовые импульсы с выхода элемента И 27 о В процессе счета срабатьшает дешифратор (начальной установки) 34 (фиг,бе), который устанавливает в О счетчик 28, подготавливая его к следующему циклу. При срабатывании

8

(нуля) 32 (фиг„6ж) через

Q

5 Q

5

0

5

0

5

элемент ИЛИ 33 устанавливается в 1 триггер 25, и процессы повторяются. Прямой и инверсньш вькоды триггера 25 являются прямым и инверсным выходами ДПКД 5с

Блок 13 формирования служебных и тактовых импульсов может быть выполнен различными способами, а данном устройстве это счетчик-защелка, выполненный на счетчике 35 и дешифраторе 39 запрета, дешифраторах 37 и 38 первого и второго служебных импульсов и элементах И 36 и НЕ 40 получения тактовых импульсов. На вхоц установки О счетчика 35 подан сигнал с инверсного выхода ДПКД 5 и va- ким образом блок 13 работает однократно за один цикл работы ДИК; 5 (фиго 6и,к,л)о

Формула изобретения

1. Формирователь линейно-частотно- модулированных сигналов, содержащий последовательно соединенные элемент И и делитель частоты с переменным коэффициентом деления, а опорный генератор, первьй дешифратор, формирователь управляютцих сигналов и выходной фильтр, отличающийся тем, что, с целью увеличения девиации частоты, в него вве- /т.ены управляемьй многофазньй генератор, вход которого соединен с выходом опорного генератора,.мультиплексор, каждый из п сигнальных входов которого соединен с соответствующим из п выходов управляемого многофазного генератора, а выход - с первым входом элемента И, второй дешифратор, вход которого соединен с выходом кода коэффициента деления формирователя управляющих сигналов, а выход - с управляющим входом делителя часто- ты с переменным коэффициентом деления, блок стробирования, первый вход которого соединен с прямым выходом делителя частоты с переменньтм коэффициентом деления, а выход - с входом выходного фильтра, и элемент задержки, вход которого соединен с выходом элемента И, а выход - с вторым входом блока стробирования, при этом выход разрешающего сигнала формиро- ,вателя управляющих сигналов соединен с вторым входом элемента И, выход кода фазы - с входом первого дешифратора, выход которого соединен с управляющим входом мультиплексора, выход элемента И и ниверсньй выход делителя частоты с переменным коэффициентом деления соединены соответственно с первым и вторым входами синхронизации формирователя управляющих сигналов, а вход запуска формирователя управляющих сигналов соединен с входом запуска делителя частоты с переменным коэффициентом деления и является входом пусковых импульсов формирователя линейно-частотно-модулированных сигналов

2. Формирователь по п.1, о т л и- чающийся тем, что формирователь управляющих сигналов содержит последовательно соединенные элемент И, блок формирования служебных и тактовых импульсов, блок формирования адреса, первый блок постоянного запоминания и счетчик, последовательно соединенные дешифратор и триггер, установочный вход которого соединен с установочным входом блока формиро- вания адреса, второй блок постоянного запоминания, вход которого соединен с выходом блока фсрмироляния адреса, и накапливаю1ций о мматор, вход

тактовых импульсов и вход служебных и myльcoв которого соединены соответственно с выходом тактовых импульсов и с выходом служебных импульсов блока формирования служебных и тактовых импульсов, выход второго блока постоянного запоминания соединен с входом дешифратора и с сигнальным входом накапливающего сумматора, при этом управляющий вход счетчика сое

динен с выходом служебных импул с-1|1 блока формирования служебных и та.чт о- вых импульсов, первьй вход элементл И явлкется первым входом синхронизации, второй вход элемента- И соединен с вторым входом блока формирования служебных и тактовых импульсов и является вторым входом синхронизации, установочный вход накапливающего сумматора соединен с установоч 1Ь м входом счетчика и триггера и является входом запуска, выход счетчика является выходом кода коэффициента деления, выход триггера - выходом разрешающего сигнала, а выход накапливающего сумматора - выходом кода фазы формирователя управляющих сигналов.

3. Формирователь по п,, отличающийся тем, что накапливающий сумматор содержит триггер, элемент И, вычитающий счетчик и делитель частоты, причем инверсный выход триггера соединен с первым входом элемента И, выход которого соединен с тактовым входом вычитающего счетчика и с тактовым входом делителя частоты, выход вычитающего счетчика соединен с сигнальным входом триггера, установочный вход триггера соединен с установочным входом вычитающего счетчика и является входом служебных импульсов, второй вход элемента И является входом тактовых импульсов, установочный вход делителя частоты - установочным входом, сигнальный вход вычитающего счетчика - сигнальным входом, а выход делителя частоты - выходом накапливающего сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор синусоидальных сигналов | 1990 |

|

SU1734189A1 |

| Частотный модулятор | 1989 |

|

SU1626320A1 |

| УСТРОЙСТВО ДЛЯ ФОРМОВАНИЯ ЧАСТОТНО-МОДУЛИРОВАННОГО СИГНАЛА | 1992 |

|

RU2039414C1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ ЛИНЕЙНО-ЧАСТОТНО-МОДУЛИРОВАННОГО СИГНАЛА | 1996 |

|

RU2110145C1 |

| Устройство фазовой автоподстройки частоты | 1986 |

|

SU1443173A1 |

| ФОРМИРОВАТЕЛЬ ЧАСТОТНО-МОДУЛИРОВАННЫХ СИГНАЛОВ | 1992 |

|

RU2033685C1 |

| Преобразователь сдвига фазы в код скорости и ускорения | 1986 |

|

SU1358096A1 |

| Устройство синхронизации с фазовой автоподстройкой частоты | 1988 |

|

SU1700751A1 |

| Синтезатор частоты с частотной модуляцией | 1986 |

|

SU1345343A1 |

| Цифровой синтезатор частоты | 1984 |

|

SU1234966A1 |

Изобретение относится к радиотехнике. Цель изобретения - увеличение девиации частоты. Формирователь линейно-частотно-модулированных /ЛЧМ/ сигналов содержит опорный г-р 1, управляемый многофазный г-р 2, мультиплексор 3, эл-т И 4, делитель 5 частоты с переменным коэффициентом деления, элемент задержки 6, формирователь 7 управляющих сигналов, блок стробирования 8, фильтр 9 и дешифраторы 10 и 11. Импульсы г-ра 1 синхронизируют г-р 2, многофазные сигналы которого поступают на мультиплексор 3, управляемый формирователем 7 через дешифратор 10. Каждый сигнал фазы проходит через эл-т И 4, управляемый формирователем 7, и поступает в делитель 5, коэффициент деления которого задается формирователем 7 через дешифратор 11. Импульс с прямого выхода делителя 5 логически умножается в блоке стробирования 8 с задержанными при помощи элемента задержки 6 импульсами и возбуждает в полосовом фильтре 9 выходные колебания ЛЧМ сигналов. Формирователь по пп. 2 и 3 формулы отличается выполнением формирователя 7 и его блока - накапливающего сумматора. 2 з.п.ф-лы, 7 ил.

Фм.Ч

Физ.5

Редактор МоПетрова

Составитель ГсЗахарченко

Техред Л.Олийнык Корректор М.Максимишинец

Заказ 4455/54

Тираж 884

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат Патент, г. Ужгород, ул. Гагарина, 101

Подписное

| Формирователь сигналов с угловой модуляцией | 1985 |

|

SU1319238A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-07-30—Публикация

1987-06-08—Подача