bi

;D

со

| название | год | авторы | номер документа |

|---|---|---|---|

| Декодирующее устройство | 1987 |

|

SU1497745A1 |

| Декодирующее устройство | 1985 |

|

SU1339894A1 |

| Анализатор кодовых последовательностей импульсов (его варианты) | 1984 |

|

SU1238243A1 |

| Кодирующее устройство | 1988 |

|

SU1587638A1 |

| Устройство тактовой синхронизации | 1982 |

|

SU1184105A1 |

| Программируемая линия задержки | 1990 |

|

SU1723656A1 |

| Устройство для передачи и приема данных | 1987 |

|

SU1510105A1 |

| Генератор кодовых последовательностей импульсов | 1987 |

|

SU1531080A1 |

| Многоканальная система сбора и регистрации измерительной информации | 1989 |

|

SU1783547A1 |

| Устройство для чтения микрофиш с автоматической установкой кадра | 1987 |

|

SU1425588A1 |

Изобретение относится к вычислительной технике, может быть использовано в цифровых системах передачи информации и позволяет повысить быстродействие устройства за счет снижения частоты синхронизации. Кодирующее устройство (код 5В6В) содержит преобразователь 1 последовательного кода в параллельный, делитель 2 частоты, элементы 3, 4 задержки, буферные регистры 5,6, преобразователь 8 алфавитных кодов, кодов, регистр 9 управления, блок 10 формирования тактовых импульсов, триггеры 11, 12 и мультиплексор 16. Благодаря введению буферного регистра 7, триггера 13 и элементов 14, 15 ИЛИ-НЕ обеспечивается точная привязка выходных сигналов и сигналов перезаписи, а также снижение частоты синхронизации мультиплексора 16 и преобразователя 1. 1 з.п. ф-лы, 10 ил.

е.7

3151

Изобретение относится к вычислительной технике и может быть использовано в цифровых системах передачи информации,

Цель изобретения - повышение быстродействия за счет снижения частоты синхронизации.

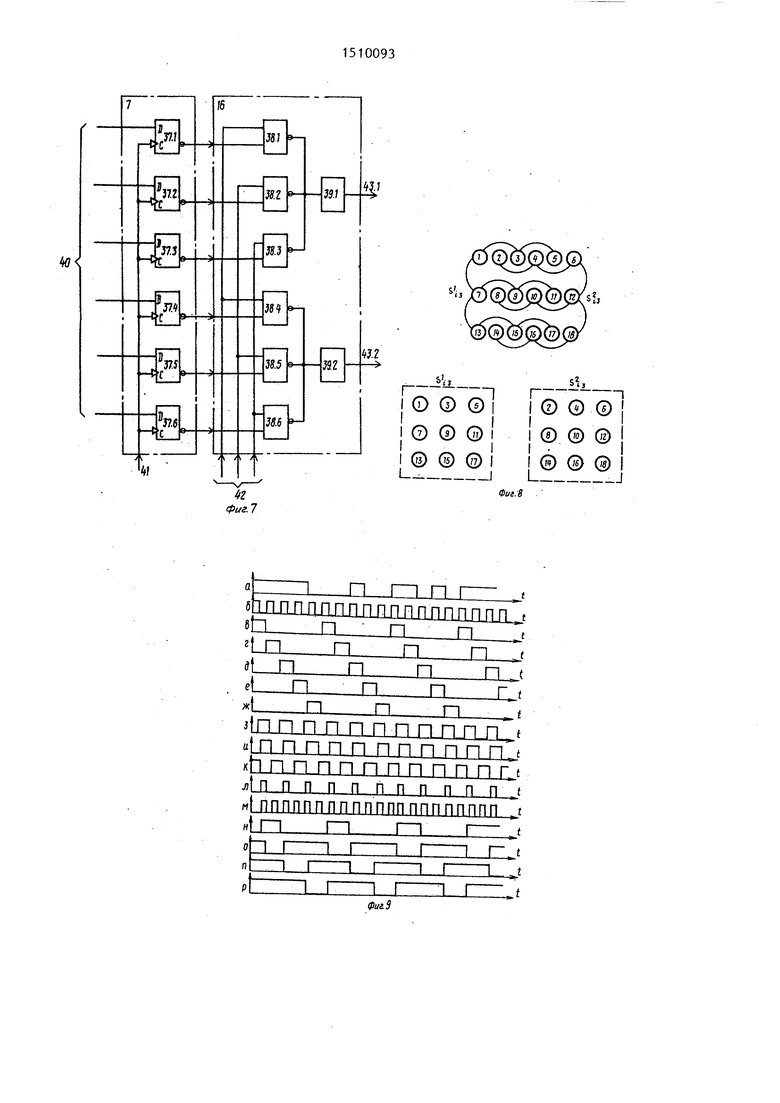

На фиг. 1 приведена блок-схема кодирующего устройства} на фиг, 2-6 - схемы выполнения соответственно преобразователя последовательного кода в параллельный, делителя частоты, преобразователя алфавитных кодов, ре гистра управления и блока формирова- кия тактовых импульсов; на фиг, 7 - схема выполнения третьего буферного регистра и мультиплексора, на фиг,8- алгоритм работы устройства; на фиг, 9 и 10 - временные диаграммы работы.

Кодирующее устройство содержит преобразователь 1 последовательного кода в параллельный, делитель 2 частоты, первый и второй элементы 3 и 4 задержки, первый - третий буферные регистры 5-7, преобразователь 8 алфавитных кодов, регистр 9 управления блок 10 формирования тактовых импульсов, первый т третий триггеры 11-13, первый и второй элементы ИЛИ-НЕ 14 и 15 и мультиплексор 16, На фиг, 1 обозначены информационный и тактовый входы 17 и 18,

Преобразователь 1 последовательно го кода в параллельный (фиг,2) выполнен на триггерах 19, На фиг,2 показаны тактовые входы 20 и выходы 21 преобразователя 1.

Делитель 2 частоты (фиг.З) содержит триггеры 22, имеет выходы 23, Элементы 3 и 4 задержки могут быть вьшолнены на отрезках коаксиальных кабелей, благодаря изменению длины которых можно регулировать ве- личину задержки.

Преобразователь 8 алфавитных кодов предназначен для преобразования пятибитовых слов в шестибитовые и содержит (фиг,4) блоки 24 постоян- ной памяти (реализуемые на ПЗУ), На фиг. 4 обозначены входы 25, первые и второй выходы 26 преобразователя 8, Регистр 9 управления представляет собой регистр сдвига и может быть выполнен (фиг,5) на триггерах 27 и элементах НЕ 28 и имеет информационный и тактовые входы 29 и 30, первые и второй выходы 31,

Блок 10 формирования тактовых импульсов (фиг.6) содержит первый и второй выделители 32 и 33 тактового сигнала, элемент ИЛИ 34,формировател 35 импульсов и первый - третий выходы 36,

Третий буферньм регистр 7 может быть выполнен (фиг,7) на триггерах 37, а мультиплексор 16 - на элементах ИЛИ-НЕ 38 и элементах НЕ 39, На фиг. 7 показано соединение выходов регистра 7 с информационными входами мультиплексора 16, а также обозначены информационные и тактовьш входы 40 и 41 регистра 7, управляющие вход 42 и первый и второй выходы 43 мультиплексора 16.

Алгоритм образования кода 5В6В заключается в преобразовании моды исходной последовательности S из пяти бит в шестибитовую моду S . Очевидно, что из пяти бит можно сформировать 32 кодовые группы, которым будут Соответствовать N кодовых груп из шести бит, где N&32,

S;., ,, ;

где Г - некоторое функциональное нелинейное преобразование (алфавит кодирования).

Сформируем два модернизированных алфавита S- и S-,,, в которых каждой пятибитовой моде Sj будут соответствовать две трехбитовые моды Sj. и S- по принципу, показанному на фиг, 8, В соответствии с этим запрограммированы блоки 24 преобразователя 8 ,

Реализация предложенного алгоритма образования кода позволяет производить обработку и.преобразование сигналов на половинной частоте.

Кодированное устройство функционирует следующим образом.

Информационные сигналы поступают на вход 17 (фиг,9а). Тактовые сигналы с частотой следования с входа 18 через элемент 3 задержки (фиг,96) подаются на вход делителя 2 частоты, на выходах 23 которого формируются сдвинутые сигналы (фиг,9в-ж), которые используются для записи информации в преобразователь 1 с частотой синхронизации Р/5, с последующей перезаписью информациив регистр 5, Оцновременно сигналом перезаписи с выхода 23.1 делителя 2 происходит запись информации с выходов преоб

разователя 8 в регистр 6 и триггер 11 в цепи обратной связи преобразователя 8. Этот же сигнал с выхода 23.1 делителя 2 поступает на входы регистра 9 управления и блока 10 формирования тактовых импульсов.

При поступлении сигнала синхронизации с частотой О,2 F на вход выделителя 32 тактового сигнала на его выходе формируется сигнал с частотой 0,6 F (фиг.9з). На выходах элемента ИЛИ ЗА формируются противофазные сигналы (фиг.9и,к). Эти сигналы формируются по длительности до величины 1/2, 4F формирователем 35 (фиг.9л). Из этих сигналов при помощи выделителя 33 формируются сигналы с частотой 1,2 F (фиг.9м), которые через элемент 4 задержки поступают на вход синхронизации триггера 12.

При подаче на информационный вход 29 регистра 9 управления сигналов с первого выхода 23.1 делителя частоты на его втором и первых, выходах 3 формируются сигналы управления (фиг 9н-р). Информационные сигналы с выходов 26.1 преобразователя 8 пере- письтаются в регистр 6. С целью совмещения во времени с сигналами, которые на выходе имеют частоту дискретизации 0,6 и 1,2 F, применен промежуточный регистр 7, запись информации в который осуществляется сигналами с второго выхода 31.2 регистра 9 (фиг.9н). Так как фронт тактовых сигналов на первом выходе 36.1 блока 10 задержан относительно фронта сигналов синхронизации на величину задержки б , то необходимым условием нормальной перезаписи информации в регистр 9 управления будет: 1

о. S ргде j, - начальная величина задержки для обеспечения нормальной работы первого разряда 27.1 регистра 9 управления.

г

Таким образом, информационные сигналы на выходе регистра 7 жестко привязаны с сигналами с частотой следования 0,6 F.

. Допустим, что на первом - шестом выходах регистра 7 формируются сигналы, приведенные на фиг. 10 а-е, а на первых выходах 31.1 регистра 9 управления имеются сигналы, приведенные на фиг. 10 ж-и. Очевидно,

3

что на выходах элементов 38,1-38.3, образуюЕцих проводное ИЛИ, будут сигналы, приведенные на фиг, 10 к, а

на выходах элементов 38,4-38.6, образующих проводное ИЛИ, будут сигналы, приведенные на фиг. Юл, Соответствующие им инверсные сигналы на выходах 43.1 и 43.2 представлены на фиг,

10 м,н. Прямые и инверсные тактовые сигналы с частотой 0,6 F приведены на фиг. 10о,п. Тогда на выходе триггера 13 будут сигналы, представленные на фиг. Юр, а на выходах элементов РШИ-НЕ 14- и 15 (условно электрически разъединенных) - сигналы, приведенные на фиг. Юс,т. Суммарный кодовый сигнал показан на фиг. 10у. Таким образом, частота синхронизации преобразователя 1 и мультиплексора 16 снижена до величины 0,2 F, а за счет третьего буферного регистра 7 обеспечивается точная временная привязка выходных тактовых сигналов

и сигналов перезаписи.

Формула изобретения

30 1- Кодирующее устройство, содержа щее преобразователь последовательного кода в параллельный, информационный вход которого является информационным входом устройства, а выходы соединены с соответствующими инфор- мационными входами первого буферного регистра, выходы которого подключе- нь К соответствующим информационным входам преобразователя алфавитных .

4Q кодов, первые и второй выходы которого соединены с информационными входами соответственно второго буферного регистра и первого триггера, первый элемент задержки, блок фор-

45 мирования тактовых импульсов, первый

и второй выходы которого- непосред- ственно и через второй элемент задержки подключены к тактовым входам соответственно регистра управления si

50 второго триггера, первые вькоды регистра управления соединены с управляющими входами мультиплексора, делитель частоты, первый выход которого подключен к тактовым входам бу55 ферных регистров и первого триггера, выход которого соединен с тактовым входом преобразователя алфавитных кодов, выход второго триггера является выходом устройства, о т л и ч а35

ю щ е е с я тем, что, с целью повышения быстродействия за счет снижеш1я частоты синхронизации, в устройство введены третий буферный регистр, третий триггер, первый и второй элементы ИЛИ-НЕ, вход блока формирования тактовых импульсов объединен с информационным входом регистра управления и первым тактовым входом преобразователя последовательного кода в параллельный и подключен к первому выводу делителя частоты, вход первого элемента задержки является тактовым входом устройства, выход первого элемента задержки соединен с входом делителя частоты, вторые выходы которого соединены с соответ- ствукяцими вторыми тактовыми входами преобразователя последовательного, кода в параллельный, выходы второго буферного регистра и второй выход регистра управления подключены соответственно к информационным и тактовому входам третьего буферного регистра, первые и вторые выходы которого соединены с одноименш)1ми информационными входами мультиплексора, первый и второй выходы которого подключены соответственно к первому входу первого элемента ИЛИ-НЕ, информационному входу третьего триггера, выход которого соединен с первым входом второго элемента ИЛИ-НЕ, второй

вход первого элемента ИЛИ-НЕ подключен к первому выходу блока формирования тактовых импульсов, третий выход которого соединен с тактовым входом третьего триггера и вторым

:входом второго элемента ИЛИ-НЕ, выходы элементов ИЛИ-НЕ подключены к информационному входу второго триггера.

2, Устройство по п. 1, о т л ичающееся тем, что блок формирования тактовых импульсов содержит первый и второй выделители тактового сигнала, формирователь импульсов и элемент ИЛИ, вход первого выделителя тактового сигнала является входом блока, выход первого выделителя тактового сигнала соединен с входом элемента ИЛИ, прямой выход которого подключен к входу формирователя импульсов и является первым выходом блока, выход формирователя импульсов соединен с входом второго вьщели- теля тактового сигнала, выход которого является вторым выходом блока,

инверсный выход элемента ИЛИ является третьим выходом блока.

Фиг. г

Фиг. 5

itut.S

ш111Ш1а1Ш1и1дя11а

Ппп п п п п п п пп п J

а П П П П П П П

п п,

хП п п п п п л п п п п r.t j;lnnnnnnnnnnn t

j

м1 рппрпппппппппппппяппп ,t

н пI II I г л

f

I (

,

1

I (ra) (2) I - I 0 0 @ I

П П П П П П П П n.t

П П П П П П П П ,t

4

rZL

cf П П

т

t П П

st.

L

-so-.

и

П П П n.t

П

Lt

П I-I П г

Фае. да

| Декодирующее устройство | 1985 |

|

SU1339894A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-09-23—Публикация

1987-12-18—Подача