Изобретение относится к вычислительной технике и может быть использовано для обнаружения неисправностей арифметических устройств вычислительных машин при выполнении операций умножения шестнадцатиричных и десятичных чисел, заданных в коде 8. 42.1.

Известно устройство обнаружения ошибок в интернативном устройстве умножения, содержащее три блока, в одном из которых производится генерация и аккумулирование остатков сомножителей, в другом - генерация и аккумулирование остатков сомножителей на базе частичных произведений, получаемых на выходных шинах блока умножения, а в третьем блоке производится сравнение выходных давних первых двух блоков. Если в результате сравнения обнаруживается неравенство предсказуемого остаткас истинным,, то выдается сигнал ошибки ti . . .

Недостатком описанного устройства является то, что оно не приспособлейо для контроля умножения десятичных чисел.

Наивблее близким по технической сущности к предла гаемрму является устройство для контроля умножения п модулю, содержащее регистры контрольных кодов множимого и множителя, входы КОТОРЫХ являются первым, и вторым входами устройства, а вьгходы подключены к входам формирователя контрольных кодов мантисс множимого и множителя,, входы которых являются третьими и четвертыми входами устройства, выходы соединены с входами .блока перемножения контрольных кодов мантисс, выход которого соедине с первым входом формирователя контрольного кода результата, второй ВХОД.которого является пятым-входом устройства, третий вход соединен с первьш выходом блока формирования контрольного кода отбрасываемой части произведения, а выход соединен с первым входом схемы сравнения второй вход которой соединен с выходом блока свертки результата 2 .

Недостаток известного устройства низкое быстродействие, невозможность указания точного места неисправности, отсутствие возможности предотвращения размножения сшибок, а также его сложность. .

Цель изобретения - повышение быстродействия и предотвращение ошибок.

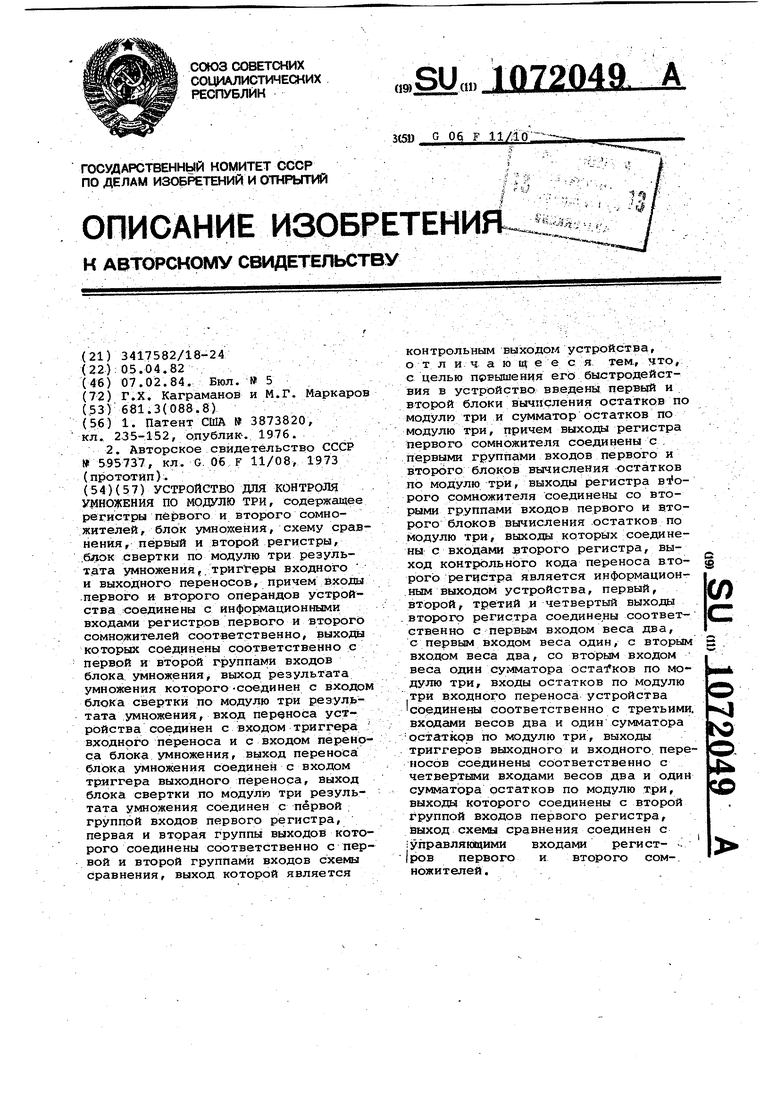

Поставленная цель Достигается тем, что в устройство для контроля умножения по модулю три, содержащее регистры первого и второго сомножителей , блок умножения, схему сравнения, первый и второй регистры, блок свертки по модулю три результата умножения, триггера входного и выходного переносов, причем входы первого и второго операндов устройства соединены с информационными входами регистров первого и 5 второго сомножителей соответственно, выходы крторых соединены соответственно с первой и второй группой входо блока умножения, выход результа -а умножения которого соединен с

0 входом блока свертки по модулю три результата умножения, вход переноса . устройства соединен с входом триггера входного переноса и с входом переноса блока умножения, выход пере5 носа блока умножения соединен с входом триггера выходного переноса, выход .блока свертки по м:одулю три результа:та умножения соединен с первой группой входов первого регист0 Ра, первая и вторая группа выходов которого соединены соответственно с первой и второй группами входов схемы сравнения, выход которой является контрольным выходом устройства, .

5 ввелены первый и второй блоки вычис. ления остатков .по модулю три и сумматор остатков по модулю три, причем выходы регистра первого сомножителя соедин нн с лервьйми группами входов первого и второго блоков вычисления остатков по модулю три, выходы регистра второго сомножителя соединены со вторыми группами входов первого и второго блоков вычисления остатков по модулю три, выходы которых

5 соединены с входами второго регистра, выход контрольного кода переноса второго регистра является информационным выходом устройства, первый, второй, третий и четвертый выходы

0 второго регистра соединены соответственно с первым входом веса два, а первьш входом веса один с вторым входом веса два, с вторым входом веса один сумматора остатков по мо5 дулю три, входы остаткр,в модуля три входного переноса устройства соединены соответственно с третьими вхойами весов Два и один сумматора остатков по модулю три, вькоды тригQ геров выходного и входного переносов соединены соответственно с четвертыми входами весов два и один сумматора остатков по модулю три, . выходы которого соединены с второй группой входов первого регистра, выход cxeNbJ сравнения соединен с управляющими входами регистров первого и второго сомножителей.

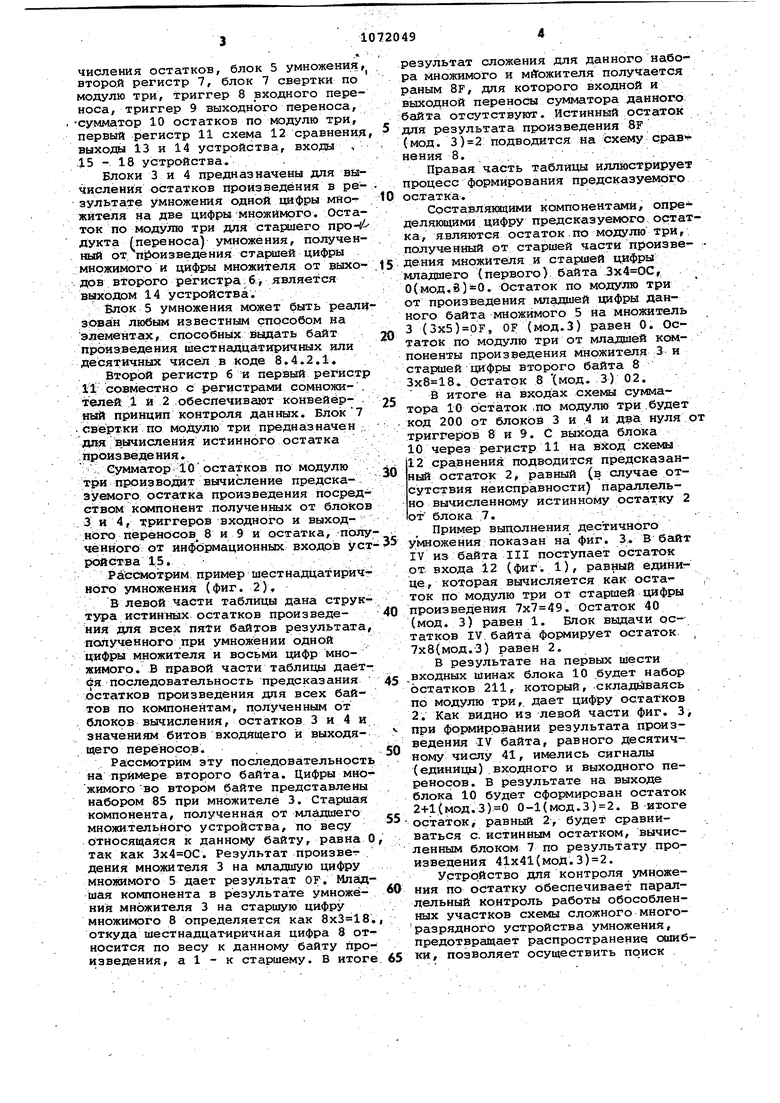

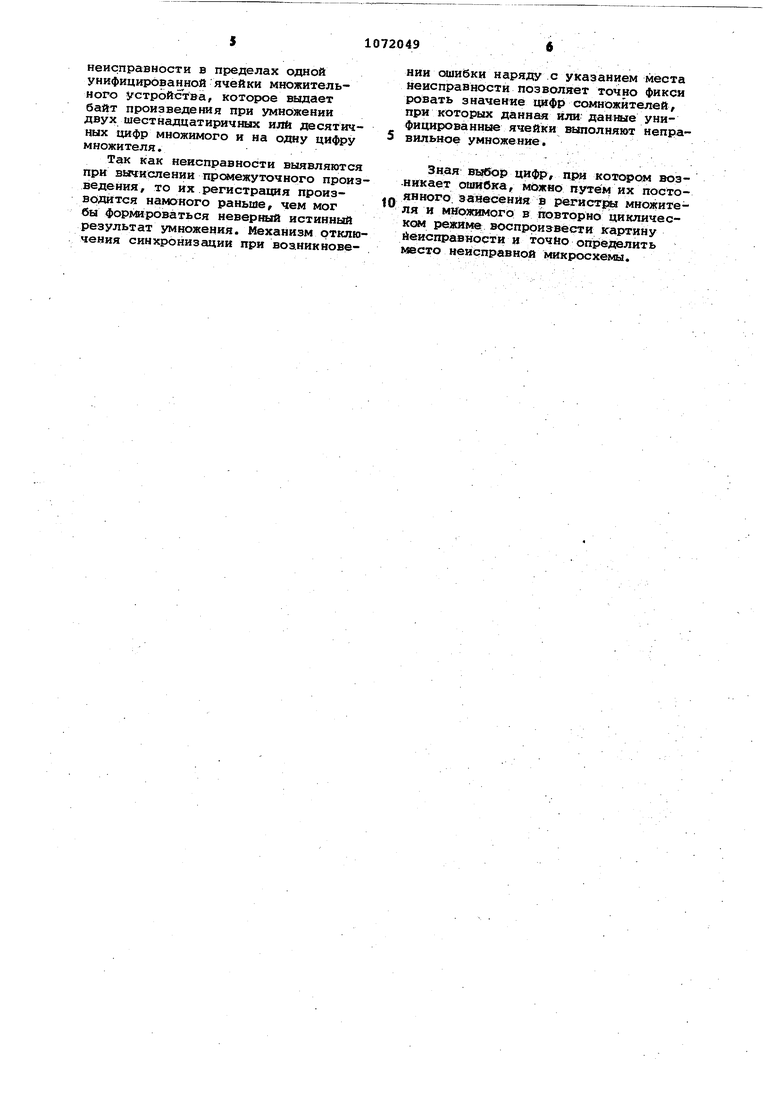

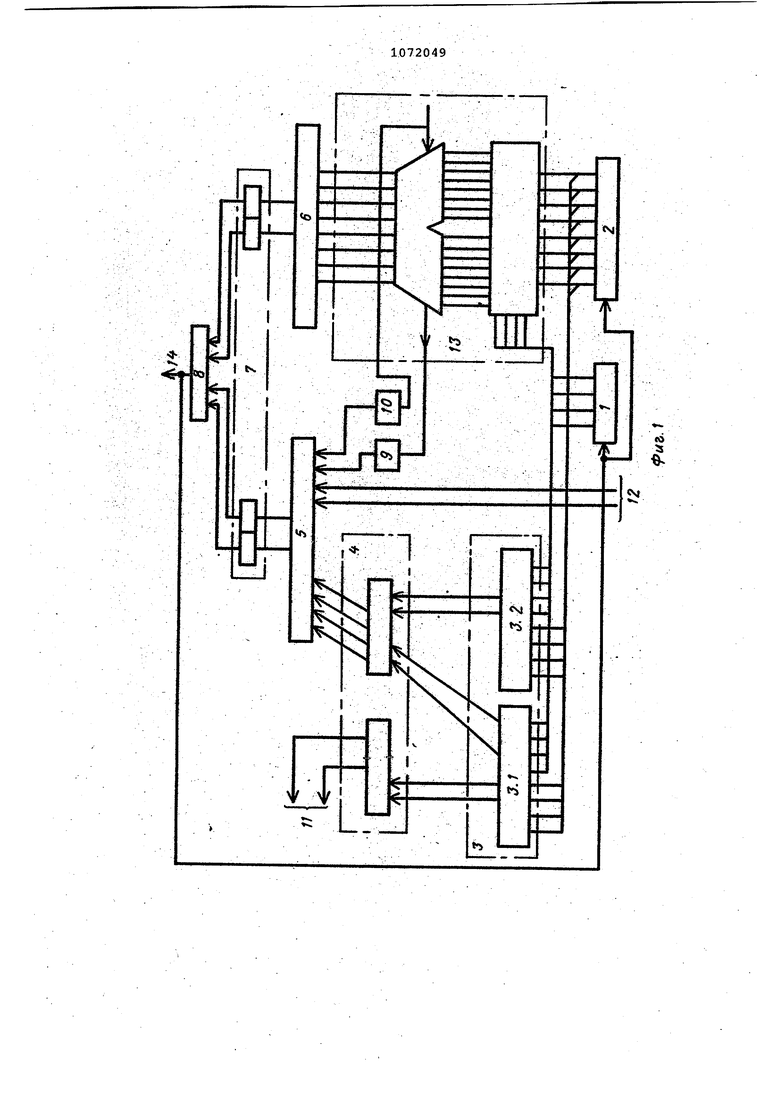

На фиг. 1 представлена блок-схема устройства на фиг. 2 - пример шест0 йадцатиричногр умножения; на фиг.З пример десятичного умножения.

Устройство содержит /регистр 1 первого сомножителя, регистр 2 второго сомножителя, первый блок 3 вы5 числения остатков, второй блок 4 вычисления остатков, блок 5 умножения, второй регистр 7, блок 7 свертки по модулю три, триггер 8 входного переноса, триггер 9 выходного переноса, сумматор 10 остатков по модулю три, первый регистр 11 схема 12 сравнениявыходы 13 и 14 устройства, входа , 15 - 18 устройства. .

Блоки 3 и 4 предназначены для вычисления остатков произведения в результате умножения одной цифры множителя на две цифры множимрго. Остаток по модулю три для старяего про-У дукта Гпереноса) умножения, полученный от произведения стадией цифры множимого и цифры множителя от выхо дов второго регистра 6 является выходом 14 устройства.

: Блок 5 умножения может быть реалЧзован любым известным способом на элементах, способных выдать байт произведения шестнадцатиричных или десятичных чисел в коде 8.4.2.1,

Второй регистр б и первый регистр ii совместно с регистрами сомножи- .

телей: 1 и 2 обеспечивают конвейер- ньай п$ инцип контроля данных. Блок7 . сверт ки по модулю три предназначен .. доя вычисления истинного остатка

произведения

Сумматор 1Оостатков по модулю три производит вычисление предсказуемого остатка произведения посредством компонент полученных от блоков З; И 4, триггеров входного и выходного п реносов 8 и 9 и остатка, полученного от информационных входов уст ,, .. . . ; ; , . ,

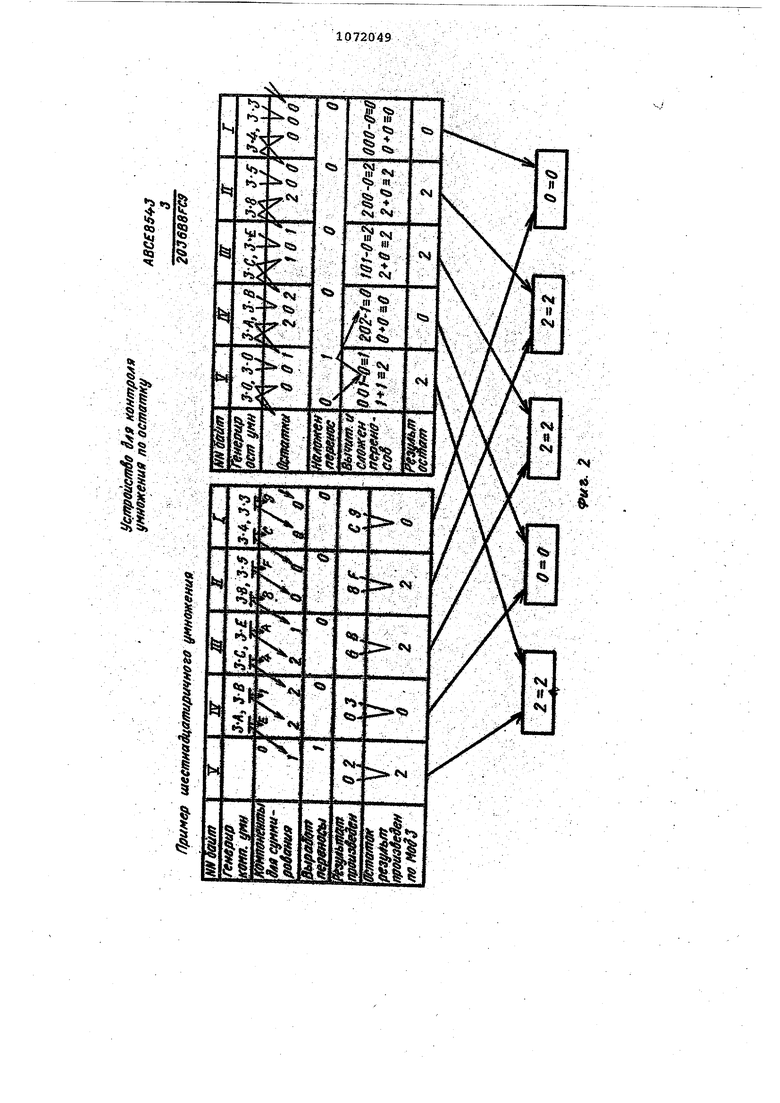

Рассмотрим пример шестнадцатиричного умножения (фиг. 2),

В левой части таблицы дана структура истинных остатков произведения для всех пяти байтов результата, полученного при умножении одной цифры множителя и восьми цифр множимого. В правой части таблицы дается последовательность предсказания остатков произведения дня всех байтов по компонентам, полученным от блоков вычисления, остатков 3 и 4 и значениям битов входящего и выходящего переносов.

Рассмотрим эту последовательность на примере второго байта. Цифры множимого во втором байте представлены набором 85 при множителе 3. Старшая компонента, полученная от младшего множительного устройства, по весу относящаяся к данному байту, равна О так как . Результат произвет дения множителя 3 на младшую цифру Мно5ким6го 5 дает резултьтат OF. Младшая компонента в результате умножёния множителя 3 на старшую цифру множимого В определяется как . откуда шестнадцатиричная цифра 8 относится по весу к данному байту произведения, а 1 - к старшему. В итоге

результат сложения для данного набора множимого и мйожителя получается раным 8F, для которого входной и выходной переносил сумматора данного байта отсутствуют. Истинный остаток для результата произведения 8F (мод. 3)2 подводится на схему сравнения В. . : . - . .

Правая часть таблицы иллаострируе процесс формирования предсказуемого остатка.

Составлякяцими компонентами, определяющими цифру предсказуемого остака, являются остаток по модулю три, полученный от старшей части произве дения множителя и старшей цифры младшего (первого) байта 0(мод.3)0. Остаток по модулю три от произведения младшей цифры данного байта множимого 5 на множитель 3 (3x5)OF, OF (мод.3) равен 0. Остаток по модулю три от младшей компоненты произведения множителя 3 и старшей цифры второго байта В . Остаток 8 (мод. 3) 02.

В итоге на входах cxeNuJ сумматора 10 остаток .по модулю три будет код 200 от блоков 3 и 4 и два нуля TpHrfepOB 8 и 9. С выхода блока 10 через регистр 11 на вход схемы 12 сравнения подводится предсказанный остаток 2 равный (в случае отсутствия неисправности) параллельно вычислен ному истинному остатку 2 от блока 7.. ,

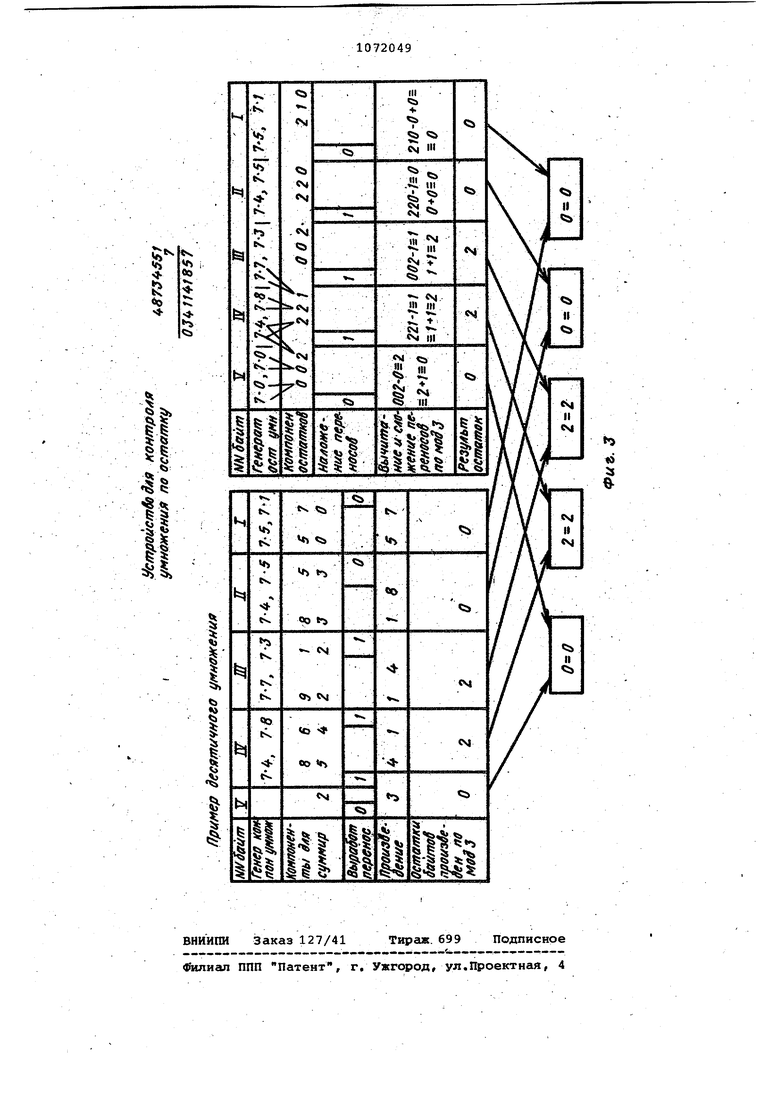

Пример выполнения дестичного умножения показан на фиг. 3. В байт IV из байта III поступает остаток рТ входа 12 (фиг; 1), равный единице, которая вычисляется как остаток по модулю три От старшей цифры произведения . Остаток 40 (мод. 3) равен 1. Блок вьщачи остатков IV байта формирует остаток 7х8(мод.З) равен 2.

В результате на первых шести входных Шинах блока 10 будет набор остатков 211, который, складываясь по модулю три, дает цифру остатков 2. Как видно из левой части фиг. 3, при формировании результата произведения IV байта, равного десятичному числу 41, имелись сигналы (единицы) входного и выходного переносов . В результате на выходе блока 10 будет сформирован остаток 2+1(мод.З)0 0-1(мод.3)2. В итоге остаток, равный 2, будеТ сравниваться с. истинным остатком, вычисленным блоком 7 по результату произведения 41х41(мод.3)2.

Устройство для контроля умножения по остатку Обеспечивает парешлельный контроль работы обособленных участков схемы сложного много разрядного устройства умножения, предотвращает распространение сйшбки, позволяет осуществить поиск .

неисправности в пределах одной унифицированной ячейки множительного устройства, которое выдает байт произведения при умножении двух шестнадцатиричных или десятичных цифр множимого и на одну цифру множителя.

Так как неисправности выявляются при вьргисяении промежуточного произведения, то их регистрация производится намоного раньше, чем мог бы формироваться неверный истинный результат умаоже яя. Механизм отключения синхронизации при возникновении сшибки наряду с указанием места неисправности позволяет точно фикси ровать значение Ю1фр сомножителей, при которых данная или данные унифицированные ячейки выполняют неправильное умножение.

Зная выбор цифр, котором воз-никает ошибка, можно путём их постоянного занесения в рвгист)ри множителя и множимого в повторно циклическом режиме воспроизвести картиНу Неисправности и точно определить место неисправной микросхемы.

п

I

3,

s I

AI f

Г I

ч

V} i «О

v

«

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1986 |

|

SU1432506A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Матричное устройство для умножения | 1979 |

|

SU842800A1 |

| Устройство для умножения | 1981 |

|

SU1032453A1 |

| Устройство для умножения | 1978 |

|

SU888109A1 |

| Устройство для умножения чисел | 1988 |

|

SU1575173A1 |

| Устройство для контроля умножения по модулю три | 1986 |

|

SU1361556A1 |

| Устройство для умножения с контролем | 1989 |

|

SU1741128A1 |

| Устройство для умножения | 1989 |

|

SU1667061A1 |

| Устройство для умножения | 1986 |

|

SU1368882A1 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ УМНОЖЕНИЯ ПО МОДУЛЮ ТРИ, содержащее регистры первого и второго сомножителей, блок умножения схему сравнения, первый и второй регистры, .блок свертки по модулю три результ.ата умножения J .триггеры входного и выходного переносов, причем входы .первого и второго операндов устройства; соединены с информационными входами регистров первого и второго сомножителей соответственно, выхода которых соединены соответственно с первой и второй группами входов блока, умножения, выход результата умножения которого -соединен с входом блока свертки по модулю три результата умножения, вход переноса устройства соединен с входом триггера входного переноса и с входом переноса блока умножения г выход переноса блока умножения соединен с входом триггера выходного переноса, выход блока свертки по модулю три результата умножения соединен с первой группой входов первого регистра, первая и вторая группы выходов которого соединены соответственно с первой и второй группами входов схемы сравнения, выход которой является контрольным выходом устройства, от л и ч. а ю 1Ц ее с я тем, что, с целью првышения его быстродействия в устройство введены первый и второй блоки вычисления остатков по модулю три и сумматор остатков по модулю три, причем выходы регистра первого сомножителя соединены с первыми группами входов первого и второго блоков вычисления остатков по модулю три, выходы регистра В1 орого сомножителя соединены со вторыми группами входов первого и второго блоков вычисления остатков по модулю Три, выходы которых соединены с входами .второго регистра, выход контрольного кода переноса второго регистра является инФормацион(О .ным выходом устройства, первый, второй, третий и четвертый выходы Свторого регистра соединены соответственно с первым входом веса два, с первым входом веса один, с вторым входом веса два, со вторым вхоДом веса один сумматора остатТков по модулю три, входы остатков по модулю .три входного переноса устройства сО|единены соответственно с третьими, входами весов два и один сумматора остатков по модулю три, выходы Триггеров выходного и входного, переносов соединены соответственно с четвертыми входами весов два и один сумматора остатков по модулю три, выходы которого соединены с второй группой входов первого регистра, выход схемы сравнения соединен с I управляющими входами регист- . Iров первого и второго сом-, ножителей.

1

Ъ

«о

« :s e

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США № 3873820, кл | |||

| Упругая металлическая шина для велосипедных колес | 1921 |

|

SU235A1 |

| Планшайба для точной расточки лекал и выработок | 1922 |

|

SU1976A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для контроля умножения по модулю | 1975 |

|

SU595737A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-02-07—Публикация

1982-04-05—Подача