(Л

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для адресации блоков памяти | 1984 |

|

SU1198565A1 |

| Устройство для формирования адреса замещаемого блока памяти | 1990 |

|

SU1777142A1 |

| Устройство для адресации блоков памяти | 1986 |

|

SU1388877A1 |

| Способ диагностики отказов динамических объектов и устройство для его осуществления | 1990 |

|

SU1718190A1 |

| Устройство для адресации блоков памяти | 1986 |

|

SU1394217A1 |

| Генератор цепей Маркова | 1982 |

|

SU1049903A1 |

| Устройство для адресации памяти | 1985 |

|

SU1298755A1 |

| Устройство для распознавания и учета деталей,перемещаемых конвейером | 1985 |

|

SU1300518A1 |

| Устройство адресации для автоматической конфигурации памяти ЭВМ | 1986 |

|

SU1408439A1 |

| Запоминающее устройство с многоформатным доступом к данным | 1986 |

|

SU1345259A1 |

Изобретение относится к вычислительной технике ,в частности, к устройствам управления основной памятью. Цель изобретения - повышение быстродействия и расширение функциональных возможностей за счет использования сигнализации при обращении к отключенным блокам памяти. Новым в устройстве для адресации блоков памяти, содержащем регистр 4 адреса, регистр 6 условного адреса, N переключателей 1 отключения блоков памяти и дешифратор 3, является введение преобразователя 5 математического адреса в условный, что дает возможность исключить режим присвоения адреса и повысить его готовность к применению. 3 ил.

со со оо ел и

3U99

Изобретение относится к вьнисли- тельной технике, в частности к устройствам управления основной памятью.

Целью изобретения является повы- шение быстродействия и расширение функциональных возможностей за счет использования сигнализации при обращении к отключенным блокам памяти.

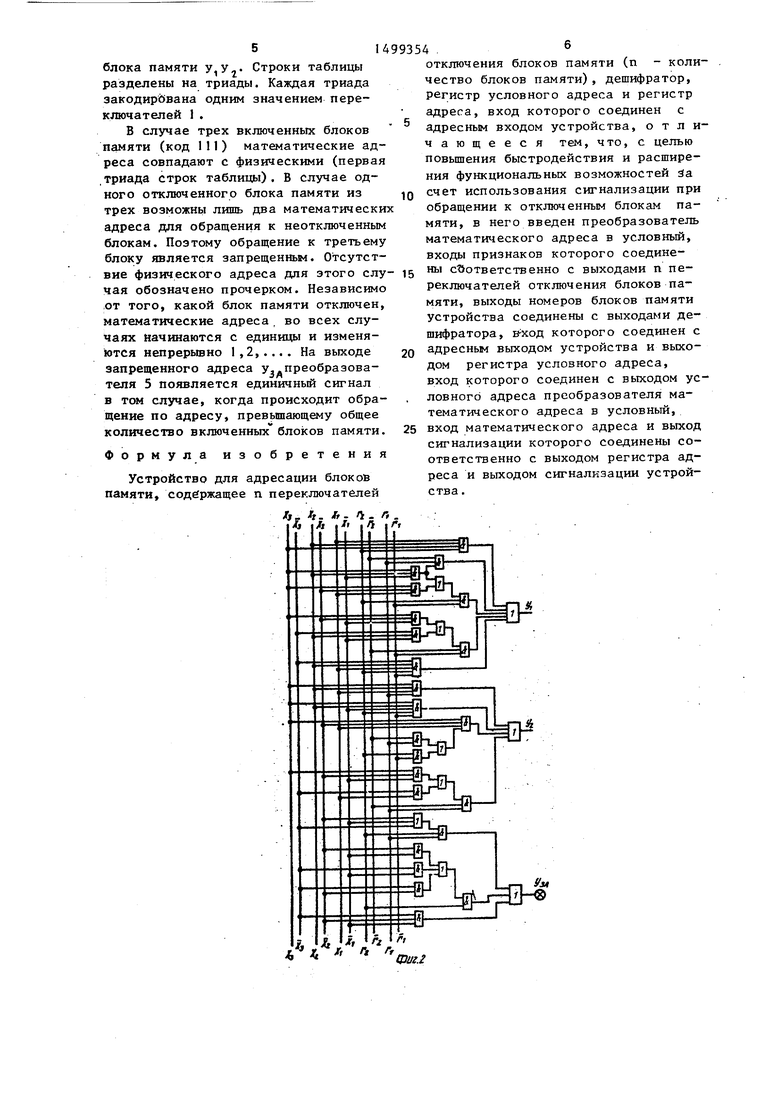

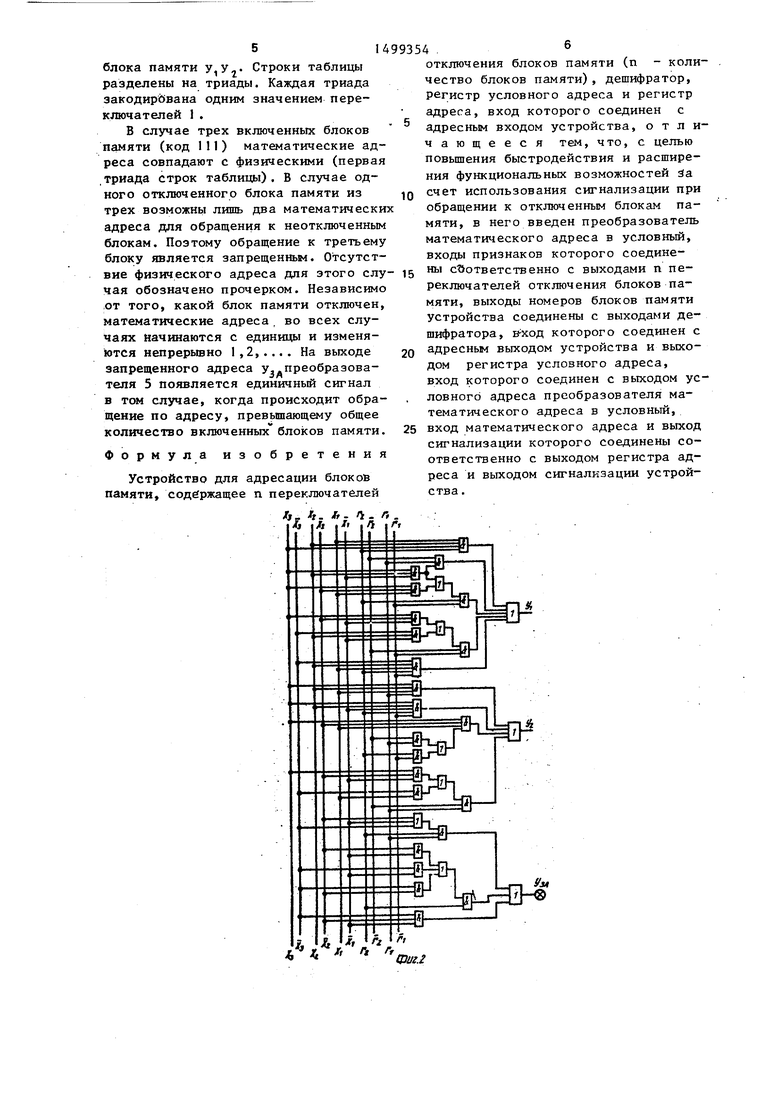

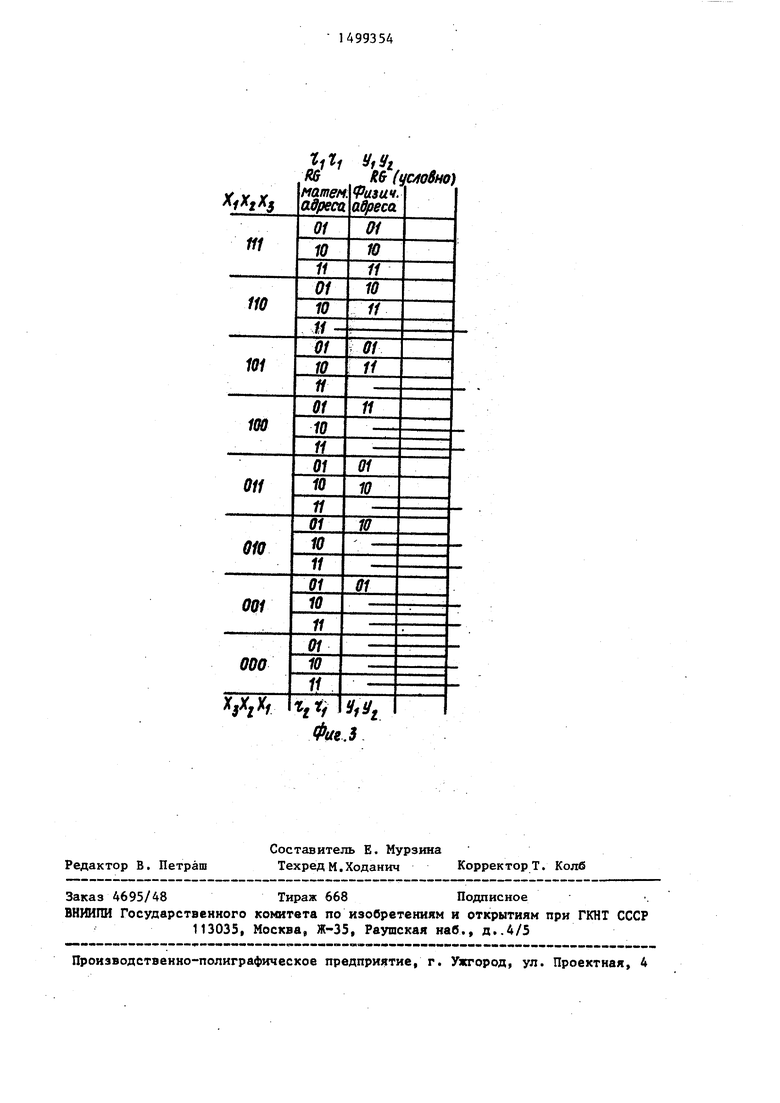

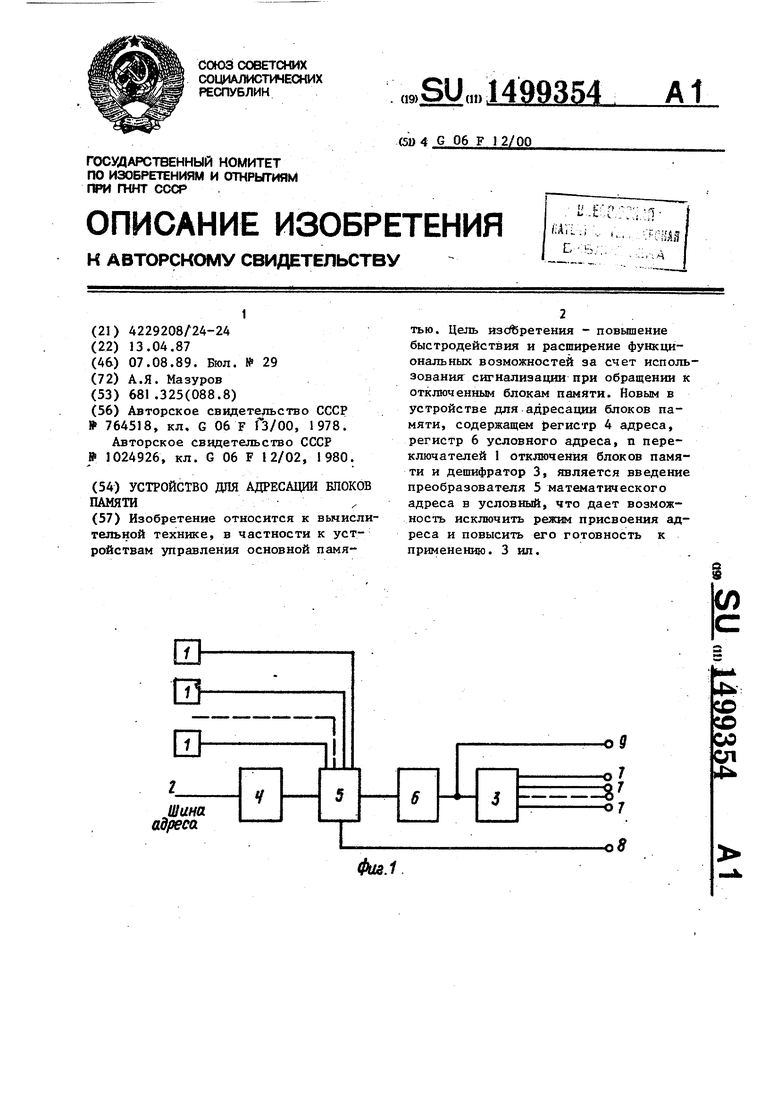

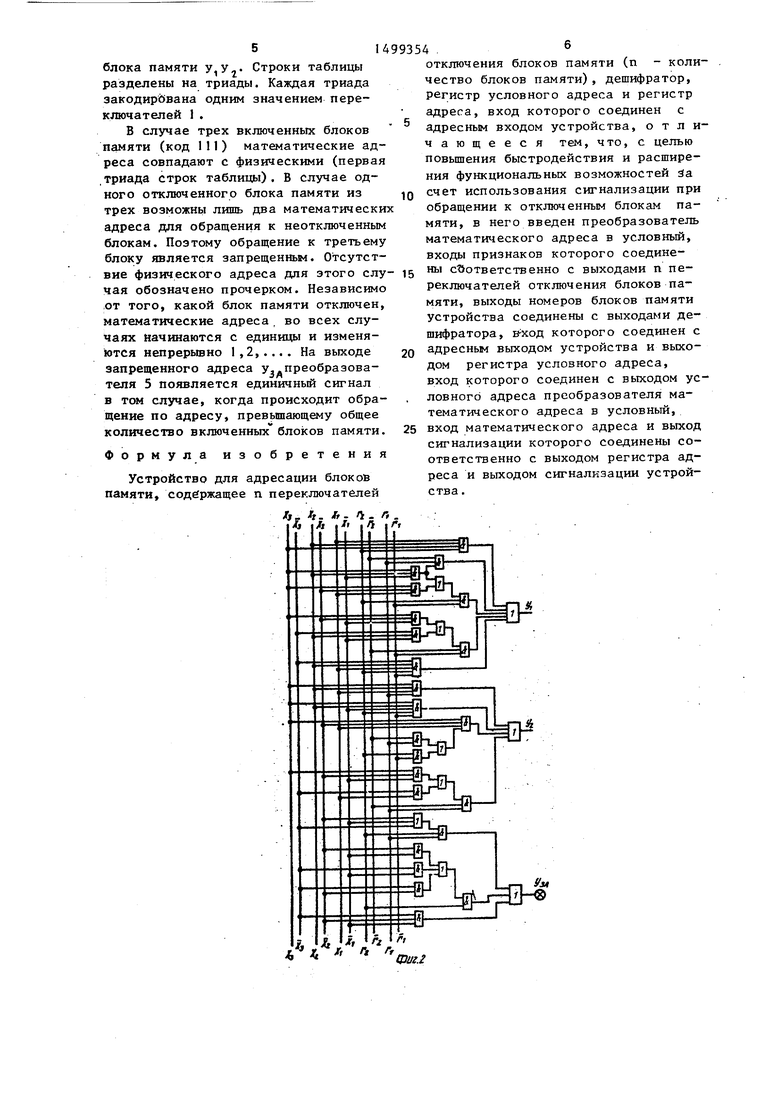

На фиг. 1 показана функциональная схема устройства; на фиг. 2 - схема реализации преобразователя математического адреса в условный ()) на фиг. 3 - таблица, поясняющая его работу.

у 111 (10Vll)vnO(OlvlO)vi01 lOvlOOOlvOlllOvOlOOl ; yj in(01V11)vno 10V101(01VlO)vi0001vOn01vo0101 ; УЗД no 11VI 01 lIVIOO(10VH)VOiniv010(10Vll)/001 (lOYll)vOOO. После упрощения выражения прини-мают следующий вид:

у 111 l-V(I10Vl01)10V(100v010)01V0110r{ у lll-lVl01(01VlO)V(100VO-I)01V11010i УЗД (-0-VOVO)П V(-OOVO-OVOO-)1-VOOO.

Устройство цаботает следующим образом.

Математический адрес поступает на регистр 4 адреса обращения. Этот адрес с регистра 4 передается на ад-f ресный вход преобразователя 5, а на его входы признаков поступают сигна- лы от переключателей 1 отключения блоков памяти. В зависимости от кодов поступающих на входы преобразователя

5,на его выходе условного адреса вы- рабатьшается код условного (физиче- ского) адреса неотключенного блока памяти. Этот адрес передается на регистр 6 условного адреса, с выхода которого адрес поступает на адресный выход устройства для использования при необходимости в ЭВМ. Этот адрес

с регистра 6 поступает также на вход дешифратора 3. Каждый выход дешифратора соответствует одному блоку памяти, а их количество - числу блоков памяти. С одного из выходов дешифратора, соответствующего блоку памяти, адрес которого занесен в регистр

6,снимается единичный сигнал, который используется как возбуждающий и передается в этот блок памяти. Независимо от того, какие блоки памяти отключены, математический их адрес (адрес обращения) начинается с младУстройство содержит переключатели 1 отключения блоков памяти, адресный вход 2 устройства, дешифратор 3, регистр 4 адреса, преобразователь 5 математического адреса в условный, регистр 6 условного адреса, выходы 7 номеров блоков памяти устройства, выход 8 сигнализации устройства, адресный выход 9 устройства.

Преобразователь 5 математического адреса в условный (фиг. 2) представляет собой комбинационную схему, построенную на основании следующих выражений при использовании таблицы.

-ших номеров и непрерьшно изменяется от первого до п-го номера блоков.

Для примера рассмотрено три блока памяти. Их математические номера 1, 2 и 3. В двоичном коде это 01 , 10,11. Если один из блоков отключен (не имеет значения какой), то математический адрес может быть 1(01), 2(10), При.этом, если осуществляется обращение к блоку 3(11), то на выходе сигнализации преобразователя 5 появляется единичный сигнал, который ука- зьтает, что произощло обращение к отключенному блоку памяти. Этот сигнал можно использовать в ЭВМ для выработки прерьшания и для загорания транспаранта Запрещенное обращение.

В первом столбце таблицы (фиг .3) поясняющей работу преобразователя 5, записаны значения положения переключателей 1 X , X J (х j 1 , если i-й блок памяти включен). Значение 110 в первом столбце означает, что первый блок памяти выключен, а второй и третий включены. Так как блоков памяти всего три, то для регистра адреса достаточио двух разрядов. Во втором столбце записаны коды математического адреса г,г, а в третьем - коды условного (физического)адреса

блока памяти У,У. Строки таблиць разделены на триады. Каждая триада закодирована одним значением переключателей 1 .

В случае трех включенных блоков памяти (код 111) математические адреса совпадают с физическими (первая .триада строк таблицы). В случае одного отключенного блока памяти из трех возможны лишь два математически адреса для обращения к неотключенным блокам. Поэтому обращение к третьему блоку 1Шляется запрещенньм. Отсутствие физического адреса для этого случая обозначено прочерком. Независимо от того, какой блок памяти отключен, математические адреса во всех случаях начинаются с единиць и изменяются непрерьгано 1,2На выходе

запрещенного адреса у,.преобразователя 5 появляется единичный сигнал в том случае, когда происходит обращение по адресу, превышающему общее количество включенных блоков памяти.

Формула изобретения

Устройство для адресации блоков памяти, содержащее п переключателей

/,. ft Л. 1. / л А f ft

0

5

0

5

отключения блоков памяти (п - количество блоков памяти), дешифратор, регистр условного адреса и регистр адреса, вход которого соединен с адресным входом устройства, отличающееся тем, что, с целью повьш1ения быстродействия и расширения функциональных возможностей йа счет использования сигнализации при обращении к отключенным блокам памяти, в него введен преобразователь математического адреса в условный, входы признаков которого соединены ctJoTBeTcTBeHHo с выходами п переключателей отключения блоков памяти, выходы номеров блоков памяти устройства соединены с выходами дешифратора, &ХОД которого соединен с адресным выходом устройства и выходом регистра условного адреса, вход которого соединен с выходом условного адреса преобразователя математического адреса в условный, вход математического адреса и выход сигнализации которого соединены соответственно с выходом регистра адреса и выходом сигнализации устройства.

сак/

| Авторское свидетельство СССР № 764518, кл, G 06 F Гз/00, 1978 | |||

| Устройство для адресации блоков памяти | 1980 |

|

SU1024926A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-08-07—Публикация

1987-04-13—Подача