Изобретение относится к вычислительной технике, к разделу запоминающих устройств, и может быть использовано в вычислительных системах с параллельной обработкой информации

Цель изобретения - расширение области применения устройства за счет обеспечения плавающего формата доступа к данным,10

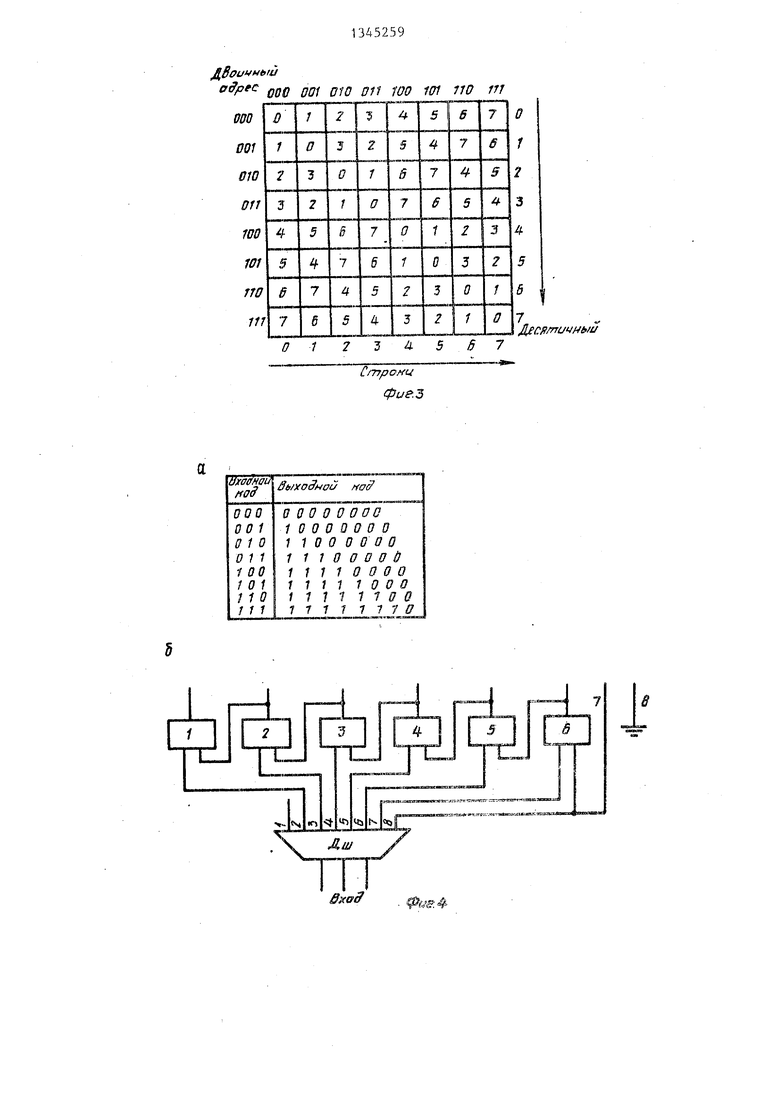

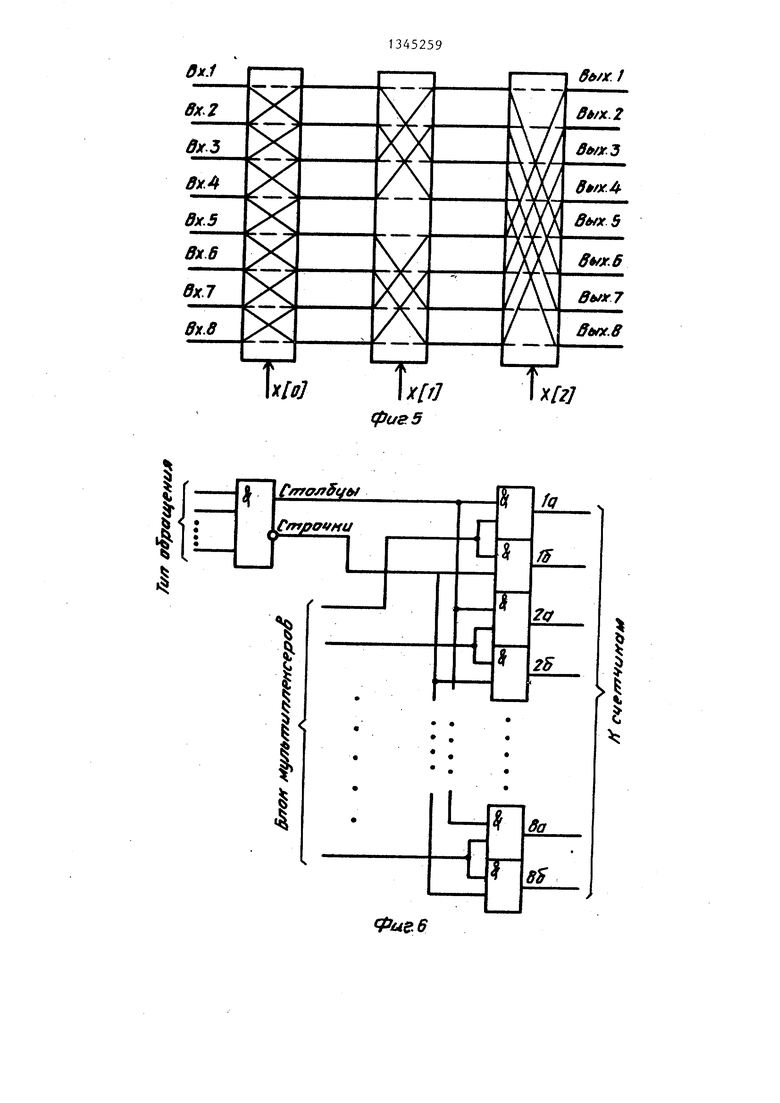

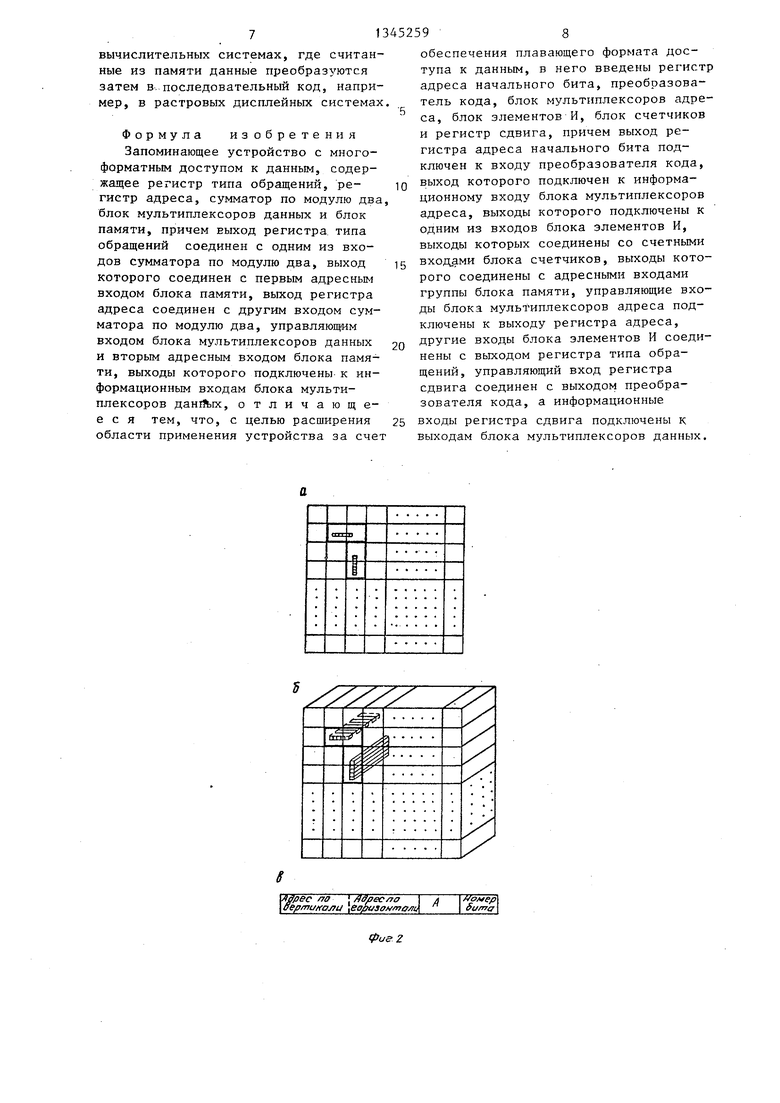

На фиг. 1 изображена блок-схема предлагаемого устройства; на фиг. 2 - варианты доступа и. формат адреса модулей памяти для предлагаемого запоминающего устройства; на фиг. 3- 15

таблица размещения данных в памяти

I

с многоформатным доступом; на фиг. 4таблица входных и выходных сигналов преобразователя кода (а) и один из вариантов реализации преобразователя 20 .кода (б); на фиг. 5 - структура блока мультиплексоров адреса и данных; на фиг. 6 - логическая схема, распределяющая коды по счетчикам в зависимости от типа обращения; на фиг. 7-25 соединение адресньк входов микросхем памяти с соответствующими шинами. Запоминающее устройство с многоъ

форматным доступом к, данньм, представленное на фиг. 1, содержит блок 30 памяти 1, блок 2 мультиплексоров данных, регистр 3 адреса, регистр 4 . типа, обращений, сумматор 5 по модулю два, регистр 6 адреса начального бита, преобразователь кода 7, блок 8 35 мультиплексоров адреса, блок 9 элементов И, блок счетчиков 10 и регистр 11 сдвига данных. Блок памяти содержит W модулей памяти, каждый из которых имеет объем 2 бит, где k - 40 целое положительное число (2 7 W),; регистр адреса начального бита имеет ту же разрядность, что и регистр адреса и равен logjW; преобразователь

регистр сдвига имеет W разрядов, о применяется для восстановления тре емого порядка бит в слове.

Фиг. 2 иллюстрирует доступ к да ным в запоминающем устройстве, пос роенном в соответствии с предлагаемой блок-схемой.. Как видно из фиг. 2.а, предлагаемая блок-схема лает возможной адресацию каждого б информации, что позволяет реализов плавающий формат обращения к данны (фиг. 2.а и 2.6). При такой органи зации памяти к формату кода адреса добавится поле, определяющее место положение начального бита внутри указанного квадрата со стороной W (фиг, 2.в). Разрядность этого поля определяется как logj W, а для его хранения служит регистр 6 адреса

начального бита.

1

Адресация данных в запоминающем устройстве такова, что адреса смеж квадратов со стороною W, в которых располагается требуемая информация отличаются друг от друга на единицу. Причем, при обращении строкам это различие будет в адрес по горизонтали, а при обращении к столбцам - в адресе по вертикали. Это значит,, что в случае размещени требуемых данных в двух смежных кв ратах (фиг, 2,а, 2.6), на одну час модулей памяти требуется подача первоначального адреса, а на остав шуюся - адреса, модифицированного единицу. Поэтому в предлагаемом ус ройстве адресные входы модулей пам ти, идентифицирующие требуемый ква рат со стороной W, имеют индивидуальную адресацию через соответству ющие счетчики.

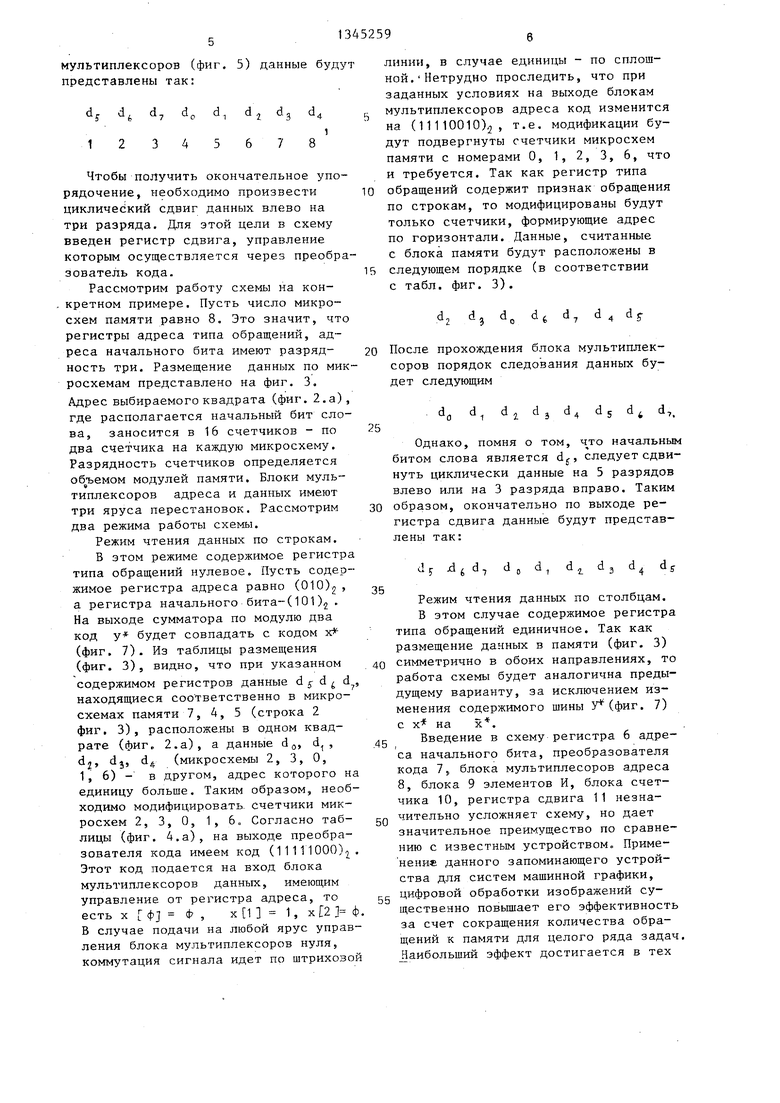

На фиг. 3 представлено размещен данных в памяти с многоформатным

кода осуществляет преобразование дво- 45 доступом с числом модулей памяти.

равным 8, Как видно из таблицы, дл нулевой строки и нулевого столбца используется линейный порядок разм щения данных. Для этого случая мод фикация адреса в соответствующих счетчиках является тривиальной: по коду номера начального бита слова определяются счетчики тех модулей памя.ти, адрес которых должен быть gp. дифицирован на единицу. Например,

ичного кода, задаваемого в регистре адреса начального бита, в единичный унитарный код ; блок мультиплексоров адреса осуществляет диадные сдвиги разрядного вектора и является идентичным блоку мультиплексоров данных; блок элементов И построен на элементах И, коммутирует единицы на соответствующие входы счетчиков в зависимости от типа обращения (строки или сто.лбцы); блок счетчиков содержит 2 X W счетчиков, общая разрядность которых определяется емкостью используемого запоминающего устройства;

регистр сдвига имеет W разрядов, он применяется для восстановления требуемого порядка бит в слове.

Фиг. 2 иллюстрирует доступ к данным в запоминающем устройстве, построенном в соответствии с предлагаемой блок-схемой.. Как видно из фиг. 2.а, предлагаемая блок-схема делает возможной адресацию каждого бит информации, что позволяет реализоват плавающий формат обращения к данным (фиг. 2.а и 2.6). При такой организации памяти к формату кода адреса добавится поле, определяющее местоположение начального бита внутри указанного квадрата со стороной W (фиг, 2.в). Разрядность этого поля определяется как logj W, а для его хранения служит регистр 6 адреса

начального бита.

1

Адресация данных в запоминающем устройстве такова, что адреса смежны квадратов со стороною W, в которых располагается требуемая информация, отличаются друг от друга на единицу. Причем, при обращении к строкам это различие будет в адресе по горизонтали, а при обращении к столбцам - в адресе по вертикали. Это значит,, что в случае размещения требуемых данных в двух смежных квадратах (фиг, 2,а, 2.6), на одну часть модулей памяти требуется подача первоначального адреса, а на оставшуюся - адреса, модифицированного на единицу. Поэтому в предлагаемом устройстве адресные входы модулей памяти, идентифицирующие требуемый квадрат со стороной W, имеют индивидуальную адресацию через соответствующие счетчики.

На фиг. 3 представлено размещение данных в памяти с многоформатным

доступом с числом модулей памяти.

равным 8, Как видно из таблицы, для нулевой строки и нулевого столбца используется линейный порядок размещения данных. Для этого случая модификация адреса в соответствующих счетчиках является тривиальной: по коду номера начального бита слова определяются счетчики тех модулей памя.ти, адрес которых должен быть мо- дифицирован на единицу. Например,

пусть номер начального бита в регистре адреса начального бита равен (lODj, Это значит, что при обращении к нулевому столбцу в счетчиках адреса

по вертикали модулей памяти 5, 6, 7 сохраняется первоначальный адрес, а в соответствующих счетчиках модулей памяти О, 1, 2, 3, 4 потребуется адрес, модифицированный на единицу. Функцию формирования единиц выполня преобразователь кода. Таблица входн и выходных кодов преобразователя представлена на фиг. 4.а. Подобное преобразование выполняется довольно просто и может быть реализовано с помощью обычного дешифратора кода и нескольких схем РШИ (фиг. 4.6).

На фиг. 3 видно, что линейньш сп соб размещения данных соответствует только нулевым строкам и столбцам. Для других строк и столбцов используется диадный способ размещения данных, который потребовал в схеме наличия блока мультиплексоров адресов. Его назначение - упорядочение нулей и единиц по соответствующим счетчикам в зависимости от порядка размещения данных. Блок мультиплексоров адреса 8 идентичен блоку мультиплексоров данных 2 и имеет.с ним . совместное управление (фиг. 5).

Назначение блока 9 элементов И состоит в коммутации нулей и единиц на соответствующие счетчики (адреса по вертикали или горизонтали) в зависимости от типа обращения (столбцы или строки). По своей структуре это (2 X W) двухвходовых элемента И; один из входов каждого элемента И соединен с соответствующим выходом блока мультиплексоров адреса, а второй вход связан с одним из двух выходов схемы И, вырабатывающей признак обращения (строки или столбцы) в зависимости от содержимого регистра типа обращения (фиг. 6) .

Блок памяти 1 состоит из W микросхем памяти-, адресные ззходы которых имеют соединение, показанное на фиг, 7. Весь формат адреса, подаваемого на вход микросхем, состоит из трех полей. Первое поле (А) служит для реализации непосредственно многоформатного доступа, т.е. возможности обращения к данным по строкам и столбцам. В этом случае на блок микросхем поступают две шины -х и у По шине подается адрес, определяющий номер строки или столбца в заданном квадрате, Значения кодов шины у получаются после поразрядного сложе-

ния по модулю два помощью сумматора

кодов S и X с 5 по модулю два

у

х

(1)

где

S код типа обращения. В этом случае правило подключения адресных входов в блоке памяти следуА

ющее: d

адресные входы

L-1

L-2

номером

do микросхем памяти с

N п,.,, п

L 2

П,

соединяются с соответствующими прово

дами шины

у/.-,

У L-1 У С-2 о

еслИ в соответствующих разрядах двоичного номера данной микросхемы есть 1, а остальные входы соединяются с соответствующими проводами шины х, схема такого соединения описывается выражением

А (у л N) V (х- д N).

(2)

Из выражения (2) следует, что

если вектор S

полностью нулевой, то х и на всех адресных входах микросхем памяти будет один и тот же код X, что соответствует выборке строки. Если S полностью единичный вектор, то из (2) следует, что у х , а выражение (2) преобразуется к виду

(3)

X

Из (3) следует, что при одном и том же X на всех микросхемах памяти выбираются биты по разным адресам. Это соответствует режиму обращения к столбцам.

Следующие 2 адресных поля микросхем памяти служат для задания требуемого квадрата в общем объеме памяти и имеют индивидуальную адресацию. Данные, считанные с блока памяти, перетасованы в соответствии с таблицей размещения, представленной на фиг. 3. Для приведения их к требуемому порядку служит блок мультиплексоров данных, структура и управление которого полностью совпадает с блоком мультиплексоров адреса (фиг. 5).

На выходе блока мультиплексоров упорядоченные по битам данные циклически сдвинуты на число разрядов, определяемое двоичным кодом регистра адреса начального бита. Например, если содержимое указанного регистра равно (101)/, то на выходе блока

мультиплексоров (фиг. 5) данные буду представлены так:

dj d d dp d, d dg d 12345678

Чтобы получить окончательное упорядочение, необходимо произвести циклический сдвиг данных влево на три разряда. Для этой цели в схему введен регистр сдвига, управление которым осуществляется через преобразователь кода.

Рассмотрим работу схемы на конкретном примере. Пусть число микросхем памяти равно 8. Это значит, что регистры адреса типа обращений, адреса начального бита имеют разрядность три. Размещение данных по микросхемам представлено на фиг. 3. Адрес выбираемого квадрата (фиг. 2.а), где располагается начальный бит слова, заносится в 16 счетчиков - по два счетчика на каждую микросхему. Разрядность счетчиков определяется об ьемом модулей памяти. Блоки мультиплексоров адреса и данных имеют три яруса перестановок. Рассмотрим два режима работы схемы.

Режим чтения данных по строкам. В этом режиме содержимое регистра типа обращений нулевое, Пусть содержимое регистра адреса равно (010) , а регистра начального бита-(101)2 . На выходе сумматора по модулю два код у будет совпадать с кодом х (фиг. 7). Из таблицы размещения (фиг. 3), видно, что при указанном

содержимом регистров данные d d d., находящиеся соответственно в микросхемах памяти 7, 4, 5 (строка 2 фиг, 3), расположены в одном квадрате (фиг, 2.а), а данные d, d , d, dj, d (микросхемы 2, 3, О, 1,6)- в другом, адрес которого на единицу больше. Таким образом, необходимо модифицировать- счетчики микросхем 2, 3, О, 1, 6. Согласно таблицы (фиг. 4.а), на выходе преобразователя кода имеем код (11111000) Этот код подается на вход блока мультиплексоров данных, имеющим управление от регистра адреса, то есть X Г Ф Ф , X 1 1, X 2 1 ф В случае подачи на любой ярус управления блока мультиплексоров нуля, коммутация сигнала идет по штриховой

линии, в случае единицы - по сплошной. Нетрудно проследить, что при заданных условиях на выходе блокам

мультиплексоров адреса код изменится на (111 10010),2 , т.е. модификации будут подвергнуты счетчики микросхем памяти с номерами О, 1, 2, 3, 6, что и требуется. Так как регистр типа

обращений содержит признак обращения по строкам, то модифицированы будут только счетчики, формирующие адрес по горизонтали. Данные, считанные с блока памяти будут расположены в

следующем порядке (в соответствии с табл. фиг. 3).

г 0 (, d 4 df

После прохождения блока мультиплексоров порядок следования данных будет следующим

25

dg d d . d j d d 5 d d,

Однако, помня о том, начальным битом слова является dj, следует сдвинуть циклически данные на 5 разрядов влево или на 3 разряда вправо. Таким образом, окончательно по выходе регистра сдвига данные будут представлены так:

d , dj d, d d d dg

Режим чтения данных по столбцам. В этом случае содержимое регистра типа обращений единичное. Так как размещение данных в памяти (фиг. 3)

симметрично в обоих направлениях, то работа схемы будет аналогична предыдущему варианту, за исключением изменения содержимого шины У(фиг. 7) с X на X.

Введение в схему регистра 6 адреса начального бита, преобразователя кода 7, блока мультиплесоров адреса 8, блока 9 элементов И, блока счетчика 10, регистра сдвига 11 незначительно усложняет схему, но дает значительное преимущество по сравнению с известным устройством. Приме- нени« данного запоминающего устройства для систем машинной графики, цифровой обработки изображений существенно повьшает его эффективность за счет сокращения количества обращений к памяти для целого ряда задач. 1аибольший эффект достигается в тех

вычислительных системах, где считанные из памяти данные преобразуются затем в. последовательный код, например, в растровых дисплейных системах

Формула изобретения Запоминающее устройство с многоформатным доступом к данным, содержащее регистр типа обращений, регистр адреса, сумматор по модулю два блок мультиплексоров данных и блок памяти, причем выход регистра типа обращений соединен с одним из входов сумматора по модулю два, выход которого соединен с первым адресным входом блока памяти, выход регистра адреса соединен с другим входом сумматора по модулю два, управляющим входом блока мультиплексоров данных и вторым адресным входом блока памяти, выходы которого подключены к информационным входам блока мультиплексоров данЙЬгх, отличающееся тем, что, с целью расширения

области применения устройства за счет

.

,

Ъ

10

3452598

обеспечения плавающего формата доступа к данным, в него введены регистр адреса начального бита, преобразователь кода, блок мультиплексоров адреса, блок элементов И, блок счетчиков и регистр сдвига, причем выход регистра адреса начального бита подключен к входу преобразователя кода, выход которого подключен к информационному входу блока мультиплексоров адреса, выходы которого подключены к одним из входов блока элементов И, выходы которых соединены со счетными входами блока счетчиков, выходы которого соединены с адресными входами группы блока памяти, управляющие входы блока мультиплексоров адреса подключены к выходу регистра адреса, другие входы блока элементов И соединены с выходом регистра типа обращений, управляющий вход регистра сдвига соединен с выходом преобразователя кода, а информационные входы регистра сдвига подключены к выходам блока мультиплексоров данных.

15

20

25

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с многоформатным доступом к данным | 1981 |

|

SU1043747A1 |

| Запоминающее устройство с многоформатным доступом к данным | 1983 |

|

SU1108507A1 |

| Запоминающее устройство с параллельным произвольным доступом к строкам и окнам данных | 1987 |

|

SU1499355A1 |

| Ассоциативное запоминающее устройство с многоформатным доступом к данным | 1988 |

|

SU1684812A1 |

| УСТРОЙСТВО ДЛЯ РЕГЕНЕРАЦИИ ИНФОРМАЦИИ ДИНАМИЧЕСКОЙ ПАМЯТИ | 1992 |

|

RU2049363C1 |

| Распределенная система для программного управления технологическими процессами | 1988 |

|

SU1605212A1 |

| Запоминающее устройство с многоформатным доступом к данным | 1986 |

|

SU1336108A1 |

| Распределенная система для программного управления технологическими процессами | 1990 |

|

SU1797096A1 |

| Оперативное запоминающее устройство с самоконтролем | 1986 |

|

SU1332386A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ИЗОБРАЖЕНИЙ | 1990 |

|

RU2047921C1 |

Изобретение относится к вычислительной технике, к разделу запоминающих устройств, и может быть использовано в вычислительных системах с параллельной обработкой информации. Целью изобретения является расширение области применения устройства за счет обеспечения плавающего формата доступа к даннь1М. Устройство содержит блок 1 памяти, блок 2 мультиплексоров данных, регистр 3 адреса, регистр 4 типа обращений, сумма Гор 5 по модулю два, регистр 6 адреса начального бита, преобразователь 7 кода, блок 8 мультиплексоров адреса, блок 9 элементов И, блок 10 счетчиков и регистр 11 сдвига данных. Применение запоминающего устройства для систем машинной графики, цифровой обработки изображений существенно повысит его эффективность за счет со.кращения количества обращений к памяти для целого ряда задач. Наибольший эффект достигается в тех вычислительных системах, где считанные из памяти данные преобразуются затем в последний код, например в растровых дисплейных системах. 7 ил. W со ел ю ел Х)

jS, адрес QQQ fju j QQ 77л jj

BOO 001 010

oir

WO 101

no in

CmpcMU фиеЗ

Фиеб

Составитель Н Фокина Редактор И. Сегляник Техред Л.Сердюкова Корректор М. Шароши

4927/51

Тираж 587 Подписное

ВНИИПИ Государственного комитета СССР

по целам изобретений и о1жрытий 113035, Москва, Ж-35, Раушская каб. , д, 4/5

Производственно-полиграфическое предприятие, г, Ужгород, ул. Гфоектная, 4

Фаг.7

| Авторское свидетельство СССР № 1200341, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Патент США № 3800289, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

Авторы

Даты

1987-10-15—Публикация

1986-03-19—Подача