со

00

оо 00 -а

Изобретение относится к вычислительной технике и может быть использовано для адресации блоков памяти в системе памяти.

Целью изобретения является упрощение устройства и повышение надеж ности его работы, за счет исключения тактируемых элементов.

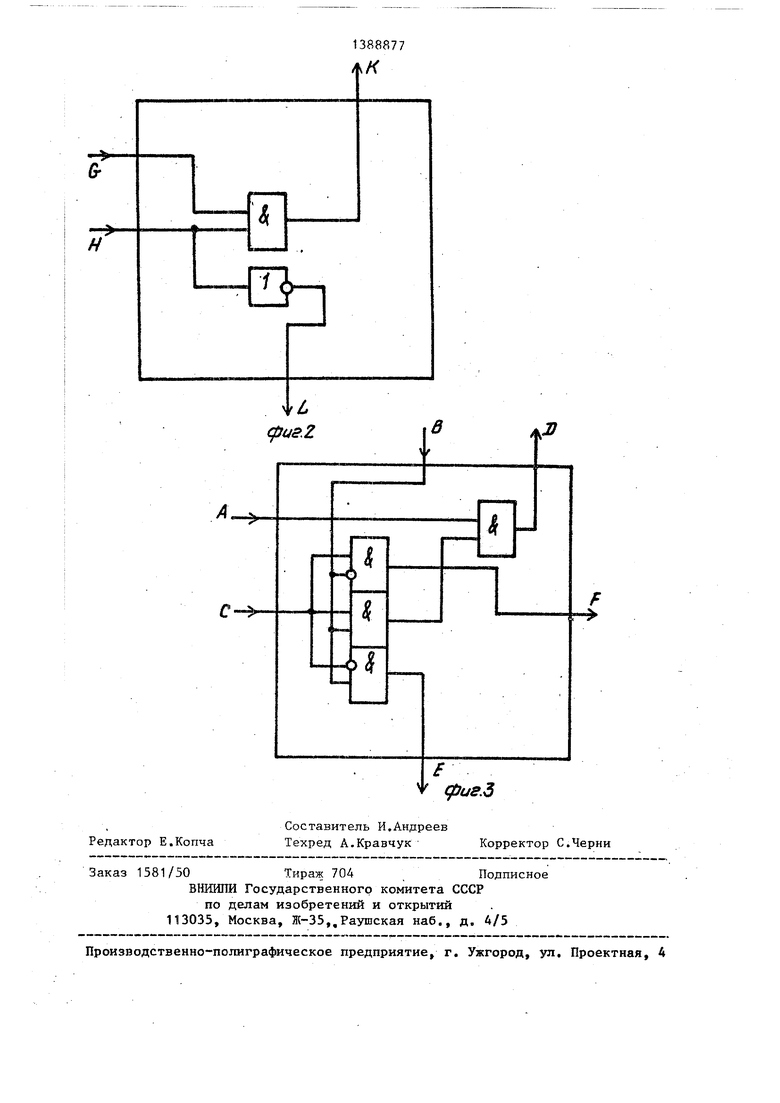

На фиг.1 представлена функциональная схема устройства для случая четырех блоков памяти; на фиг.2 и 3 - примеры реализации первого и второго элементов комм тации.

Устройство для адресации блоков памяти содержит переключатели 1-4., регистр 5 адреса, дешифратор 6 адреса, элементы ИЛИ 7-9, первый 10 и второй 11 элементы коммутации и имеет вход 12 адреса и вькоды 13-16 устройства.

Устройство работает следующим образом.

Элемент 10 коммутации (фиг.2) реализует логические функции , L Н, где G, Н, К, L - сигналы на первом, втором входах и первом, втором выходах соответственно. Элемент 11 коммутации (фиг.З) реализует ло- функции D ABC, Е ВС, F ВС, где А, С, Б.,, D, F - сигналы на первом, втором, третьем входах и первом, втором, третьем выходах соответственно.

Сразу же после подачи питания начинается сеанс распределения памяти в матрице элементов 10 и 11 коммутации в соответствии с сигналами переключателей 1-4. Сигнал высокого уровня (ВУ) на выходе переключателей 1-4 соответствует состоянию Блок включен , сигнал низкого уровня (НУ) - Блок выключен.

Предпотгожим, что на выходе переключателя 1 присутствует сигнал НУ (первый блок памяти выключен). Тогда в соответствии с функцией К GH элемента 10, расположенного в первой строке первого столбца, это делает невозможной коммутацию первого блока памяти, а в соответствии с функцией L Н на втором выходе элемента 10 устанавливается сигнал ВУ, который поступает на второй вход элемента 11 коммутации второй строки первого столбца. Предположи :-, что на выходе переключателя 2 установлен сигнал ВУ (второй блок памяти включен). Тогда

0

5

0

5

0

5

5

на выходе второго элемента И (в этом элементе коммутации) устанавливается сигнал ВУ, который поступил на второй вход четвертого элемента И, подготавливая его к включению. Одновременно с этим в соответствии с функцией F ВС на третьем выходе элемента 11 коммутации устанавливается сигнал НУ, который делает невозможным возбуждение второго блока любым выходом дешифратора 6, кроме первого. В соответствии с функцией F ВС на втором выходе элемента 11 коммутации устанавливается сигнал НУ, который делает невозможным возбуждение первым выходом депшфратора 6 любого блока, кроме второго.

г

Предположим, что на выходе переключателя 3 установлен сигнал НУ. Это делает невозможным включение ни одного элемента коммутации в третьей строке. Если на выходе переключателя 4 установлен сигнал ВУ, то это вызывает включение элемента коммутации четвертой строки второго столбца аналогично описанному. Процесс переключения элементов коммутации протекает асинхронно, причем коммутация через включившиеся элементы коммутации выходов дешифратора 6 и выходов элементов 7-9 ИЛИ, подключенных к адресным схемам блоков памяти, происходит сверху вниз и слева направо.

Таким образом, если на выходе какого-либо переключателя установлен НУ, то в этой строке матрицы на первых выходах всех элементов коммутации устанавливаются сигналы НУ и, следовательно, сигнал .НУ на выходе соответствующего элемента ИЖ, что делает невозможным возбуждение отключенного блока памяти при любом адресе обращения. Если на выходе какого-либо переключателя установлен сигнал ВУ, то это вызывает включение в этой строке того элемента коммутации, который расположен в ближайшем к началу матрицы столбце, не содержащем включиввшхся ранее элементов коммутации. В каждой строке и каждом столбце матрицы может быть включено не более одного элемента коммутации. После времени, необходимого на распространение сигналов по цепям матрицы элементов 10 и 11, считается, что распределение памяти в соответствии с положениями переключателей

1-4 произошло и блоки памяти доступны для обращения. Адрес обращения с входа .12 поступает в регистр 5 и передается на дешифратор 6. С j-ro выхода дешифратора 6 сигнал ВУ (в соответствии с адресом обращения) поступает на первые входы всех элементов коммутации j-ro с голбца. При этом на первом выходе включившегося элемента коммутации 1-й строки (т.е. того элемента, у которого во время сеанса распределения памяти на втором входе четвертого элемента И ус- тановился сигнал ВУ) устанавливает- ся сигнал ВУ, который поступает на один из входов i-ro элемента ИЛИ. С выхода i-ro элемента ИЛИ сигнал поступает в адресную схему i-ro блока памяти, вызывая его возбуждение. Так, если в регистр 5 поступит первый адрес, то в соответствии с произошедшей коммутацией через элемент ИЛИ 7 будет возбужден второй блок памяти, если в регистр 5 поступит вто- рой адрес, то через элемент ИЛИ 9 будет возбужден четвертый блок памяти и- так далее независимо от очередности прихода адресов обращения. Если i-й блок памяти будет отключен в процессе работы, то перераспределени памяти произойдет автоматически путем переключения элементов 10 -и 11 матрицы.

Таким образом, адресу обращения j всегда соответствует j-й блок памяти из числа неотключенных и незанятых блоков памяти.

Формула изобретения

Устройство для адресации блоков памяти, содержащее группу переключателей, регистр адреса, дешифратор

Q 5 0 5 О

5

0

5

адреса, группу элементов ИЛИ, причем информационный вход регистра адреса является адресным входом устройства, выход регистра адреса соединен с входом дешифратора адреса, выходы элементов ИЛИ группы являются выходами устройства, о т л и ч а ю- in; е е с я тем, что, с целью упрощения устройства, в него введены две - группы элементов коммутации, образующие треугольную матрицу размерности п-п, причем элементы коммутации первой руппы расположены по главной диагонали матрицы, а элементы коммутации второй группы расположены под главной диагональю матрицы и образуют треугольную подматрицу элементов коммутации второй группы, i-й выход дешифратора адреса соединен с первыми входами элементов коммутации первой и второй групп i-ro столбца треугольной матрицы (i 1,...,п), выход j-ro переключателя группы соединен с вторым входом j-ro элемента коммутации (j 1,...,п) первого столбца треугольной матрицы, первый выход элемента коммутации первой группы первого столбца матрицы является первым выходом устройства, первые выходы элементов коммутации первой и второй групп каждой строки матрицы, кроме первой, соединены с входами соответствующих элементов IiЛИ группы, второй -выход каждого элемента коммутации i-ro столбца k-й строки матрицы (k 1,...,п-1) соединен с третьим входом элемента коммутации i-ro столбца (и+1)-й строки матрицы, третий выход каждого из элементов коммутации второй группы i-ro столбца j-й строки матрицы соединен с вторым входом элемента коммутации (i + 1)-го столбца j-й строки матрицы.

/

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для адресации блоков памяти | 1988 |

|

SU1575189A1 |

| Устройство для адресации | 1988 |

|

SU1573458A2 |

| Матричный коммутатор | 1988 |

|

SU1596342A1 |

| Устройство для адресации блоков памяти | 1984 |

|

SU1198565A1 |

| Устройство для сопряжения каналов ввода-вывода с внешними устройствами | 1985 |

|

SU1277128A1 |

| Устройство для адресации блоков памяти | 1989 |

|

SU1661774A1 |

| Устройство для сопряжения | 1990 |

|

SU1784984A1 |

| Запоминающее устройство с переменным форматом данных | 1981 |

|

SU987678A1 |

| Устройство для решения дифференциальных уравнений | 1985 |

|

SU1310839A1 |

| Устройство для контроля микропроцессорных блоков | 1988 |

|

SU1531099A1 |

L

cfitjs.Z

.-О

С

| Устройство для управления памятью | 1978 |

|

SU999058A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Транспортер для перевозки товарных вагонов по трамвайным путям | 1919 |

|

SU102A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для адресации блоков памяти | 1984 |

|

SU1198565A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1988-04-15—Публикация

1986-09-16—Подача