Изобретение относится к вычислительной технике и может быть исполь- Эовано при непрерывной адресации модулей памяти ЭВМ,

Оперативная память вычислительных Машин большой мощности состоит из Отдельных модулей, которые могут быть |этключе ны в случае наличия в них не- |1справностей, причем исправные моду- W в данном случае должны иметь непрерывную адресацию.

I Операции присвоения неотключенным модулям памяти непрерывной адресации осуществляются устройствами конфигу- {рации памяти.

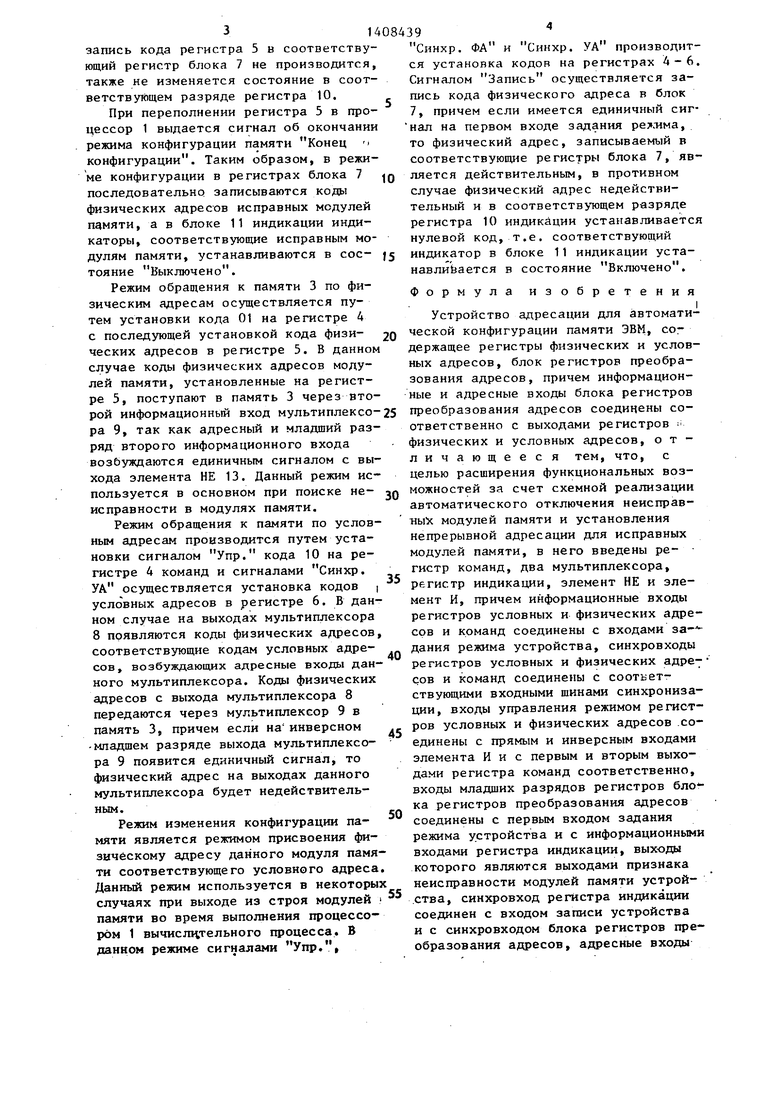

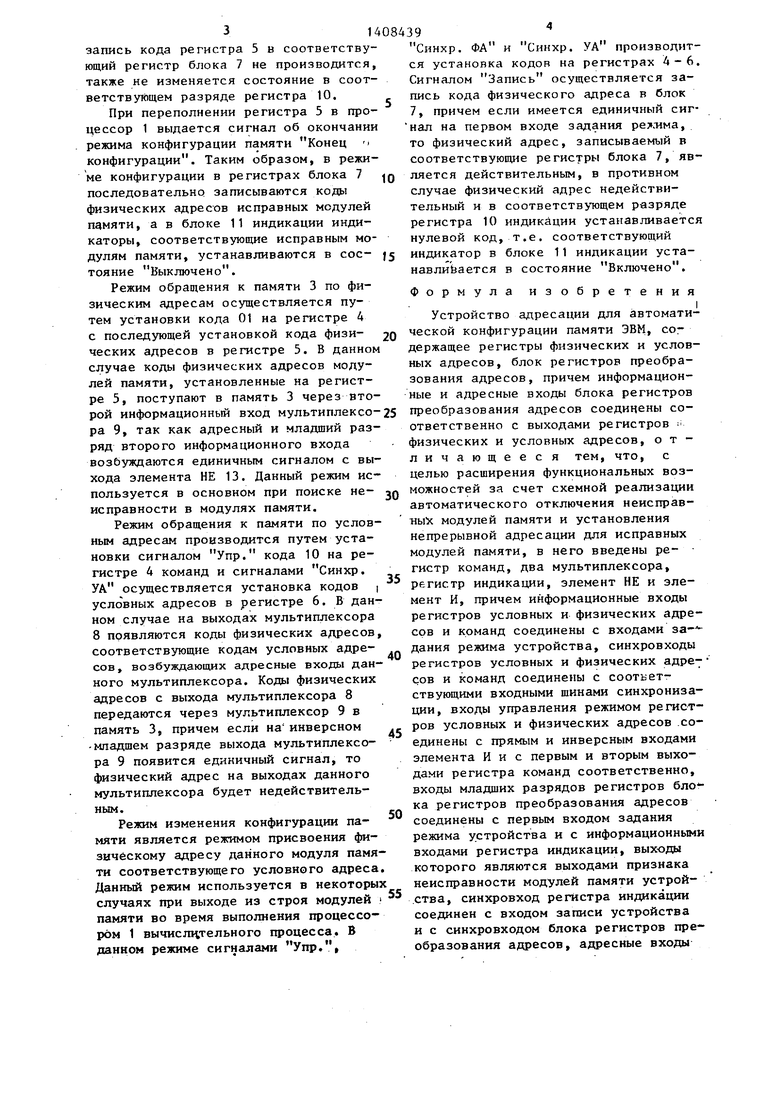

i Цель изобретения - расширение функциональных возможностей за счет схемной реализации автоматического отключения неисправных модулей памяти |и установления непрерывной адресации |для исправных модулей памяти, : На фиг,1 представлена структурная |схема соединения процессора, устрой- (ства адресации и оперативной памяти; {на фиг.2 - функциональная схема уст- {ройства.

I Схема соединения включает процес- I сор 1, устройство 2 адресации и one- Iративную память 3.

г Устройство адресации содержит регистр 4 команд, регистр 5 физических адресов, регистр 6 условных адресов, I блок 7 регистров преобразования адре- сов, первый 8 и второй 9 мультиплек- соры, регистр 10 индикации, блок 11 индикации, элемент И 12 и элемент , НЕ 13.

Выходы F, ,Р„,Q,A2,A1,Fj процессор I 1 являются соответственно выходом записи информации, в память 3, выходом обращения к памяти 3, информационным выходом, выходом адреса в модулях памяти, выходом адреса модулей памяти, выходом управления устройством 2.

Выходы устройства 2 А и F являются соответственно выходами физического адреса модулей памяти и управляющим выходом, последний служит для передачи в процессор 1 сигнала Не действительный адрес в случае обращени процессора 1 к отключенному модулю памяти,и сигнала, Конец конфигурации, необходимого для сигнализации об окончании в устройстве 2 режима конфигурации памяти.

Режимы работы устройства определяются кодами, установленными на регистре 4 команд, первый и второй выхо

о

5

0 5

0

с

д

0

5

ды которого подключены к управляющим входам регистров физических 5 и условных 6 адресов соответственно. При единичном значении на каком-либо выходе регистра 4 команд соответствующий регистр физического 5 или условного 6 адресов работает в режиме занесения информации по информационным входам, в противном случае данные регистры работают в режиме счетчика, причем режимы работы регистров условных 6 и физических 5 адресов осуществляются при наличии на их синхровхо- дах единичных сигналов.

В зависимости от кодов, установленных на выходах регистра 4 команд, устройство может работать в следующих режимах: конфигурации памяти (код 00 на регистре 4), обращения к памяти по физическим адресам (код 01 на регистре 4), обращения к памяти по условным адресам- (код 10 на регистре 4), изменения конфигурации памяти (код 11 на регистре 4).

Режим конфигурации памяти осуществляется следующим образом. Сигналом управления Сброс производится установка всех регистров устройства 2 в нулевое состояние, сигналом управления Упр. - установка кода команды Конфигурация (код 00) на регистре 4 команд, осуществляется проверка тестовой информации модуля памяти памяти 3, адрес которой соответствует коду, установленному на регистре 5, который работает в счетчика (на адресном входе мультиплексора 9, в данном случае, разрешающий сигнал с выхода элемента НЕ 13). В случае положительного результата проверки модуля памяти памяти 3 в устройство 2 выдается из процессора 1 единичный сигнал Запись и единичный сигнал на первый вход задания режима и производится занесение кода, установленного на регистре 5, в регистр блока 7, определенного кодом на регистре 6, в разряде регистра 1Q индикации, соответствующем коду на регистре 6, устанавливается единичное значение. Сигналами Синхр. ФА и Синхр УА, поступакяцими с процессора 1, происходит изменение кодов на +1 в регистрах 6 и 5.

В случае отрицательного результата при проверке тестовым контролем модуля памяти fl памяти 3 сигналы Запись и Синхр, УА не вырабатываются, т.е.

запись кода регистра 5 в соответствующий регистр блока 7 не производится также не изменяется состояние в соответствующем разряде регистра 10.

При переполнении регистра 5 в процессор 1 выдается сигнал об окончании режима конфигурации памяти Конец ч конфигурации. Таким образом, в режиме конфигурации в регистрах блока 7 последовательно записываются коды физических адресов исправных модулей памяти, а в блоке 11 индикации индикаторы, соответствующие исправным модулям памяти, устанавливаются в состояние Выключено.

Режим обращения к памяти 3 по физическим адресам осуществляется путем установки кода 01 на регистре 4 с последующей установкой кода физических адресов в регистре 5. В данном случае коды физических адресов модулей памяти, установленные на регистре 5, поступают в память 3 через второй информационный вход мультиплексора 9, так как адресный и младший разряд второго информационного входа возбуждаются единичным сигналом с выхода элемента НЕ 13. Данный режим используется в основном при поиске не- исправности в модулях памяти.

Режим обращения к памяти по условным адресам производится путем установки сигналом Упр. кода 10 на регистре 4 команд и сигналами Синхр. УА осуществляется установка кодов | условных адресов в регистре 6. В данном случае на выходах мультиплексора 8 появляются коды физических адресов, соответствующие кодам условных адресов, возбуждающих адресные входы данного мультиплексора. Коды физических адресов с выхода мультиплексора 8 передаются через мультиплексор 9 в память 3, причем если иа инверсном -младшем разряде выхода мультиплексора 9 появится единичный сигнал, то физический адрес на выходах данного мультиплексора будет недействительным.

Режим изменения конфигурации памяти является режимом присвоения физическому адресу данного модуля памяти соответствующего условного адреса. Данный режим используется в некоторых случаях при выходе из строя модулей памяти во время выполнения процессором 1 вычислительного процесса. В данном режиме сигналами Упр.,

Синхр. ФА и Синхр. УА производ 1Т- ся установка кодов на регистрах 4-6. Сигналом Запись осуществляется запись кода физического адреса в блок 7, причем если имеется единичный сиг- нал на первом входе задания режима, то физический адрес, записываемый в соответствующие регистры блока 7, является действительным, в противном случае физический адрес недействительный и в соответствующем разряде регистра 10 индикации устанавливается нулевой код, т.е. соответствующий индикатор в блоке 11 индикации устанавливается в состояние Включено.

0

5 Q

5

0

5

0

5

I

Формула изобретени

Устройство адресации для автоматической конфигурации памяти ЭВМ, содержащее регистры физических и условных адресов, блок регистров преобразования адресов, причем информационные и адресные входы блока регистров преобразования адресов соединены соответственно с выходами регистров физических и условных адресов, отличающееся тем, что, с целью расширения функциональных возможностей за счет схемной реализации автоматического отключения неисправных модулей памяти и установления непрерывной адресации для исправных модулей памяти, в него введены ре- гистр команд, два мультиплексора, регистр индикации, элемент НЕ и элемент И, причем информационные входы регистров условных и физических адресов и команд соединены с входами за- - Дания режима устройства, синхровходы регистров условных и физических адре- сов и команд соединены с соответствующими входными щинами синхронизации, входы управления режимом регистров условных и физических адресов соединены с прямым и инверсным входами элемента И и с первым и вторым выходами регистра команд соответственно, входы младших разрядов регистров ка регистров преобразования адресов соединены с первым входом задания режима устройства и с информационными входами регистра индикации, выходы которого являются выходами признака неисправности модулей памяти устройства, синхровход регистра индикации соединен с входом записи устройства и с синхровходом блока регистров преобразования адресов, адресные входы

которого соединены с адресными входами первого мультиплексора, адресные входы регистра индикации соединены с выходами регистра физических дресов и с старшими разрядами второго информационного входа второго мультиплексора, младший разряд второго информационного входа и адресный вход которого соединены с выходом элемента НЕ вход которого соединен с вторым выходом регистра команд, первый информационный вход второго мультиплексора соединен с выходом первого мультиплексора, информационные входы которого соединены с выходами блока регистров преобразования адресов, входы установки нуля всех регистров соединены с входом сброса устройства, инверсный выход элемента И является выходом признака завершения тестирования памяти устройства, выходы второго мультиплексора являются выходами задания адреса устройства, выход переполнения регистра физических адресов является выходом признака конца конфигурации памяти устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ АДРЕСАЦИИ ПАМЯТИ | 1990 |

|

RU2020566C1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1383368A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1260961A1 |

| Устройство для формирования адресов команд и данных | 1985 |

|

SU1312573A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1134937A1 |

| Модульное устройство для программного управления и контроля | 1988 |

|

SU1647519A1 |

| Табличный процессор | 1982 |

|

SU1108446A1 |

| Устройство сопряжения процессора с памятью | 1986 |

|

SU1322296A1 |

| Устройство для записи и коррекции программ | 1982 |

|

SU1149268A1 |

| Устройство для сопряжения двух магистралей | 1986 |

|

SU1348874A1 |

Изобретение относится к вычислительной технике и может быть использовано при непрерывной адресации модулей памяти ЭВМ. Целью изобретения является расширение функциональных возможностей устройства за счет схемной реализации автоматического отключения неисправных модулей па.мяти и установления непрерывной адресации для исправных модулей памяти,- причем информация об отключенных (неисправных) модулях памяти визуально представляется .оператору на блоке инди-, кации. Данная цель достигается за счет того, что в устройство, содержащее регистр физических адресов, регистр условных адресов, блок регистров преобразования , дополнительно введены регастр команд, два мультиплексора, регистр индикацш, элемент НЕ и элемент И. 2 ил. г (О

, fi S

At А1

D

s

ммяш

тяяш

} At

НЯЯЕ

А1

фиг.1

| Прожиялковский В.В., Ломов Ю.С | |||

| Технические и программные средства ЭВМ | |||

| М.: Статистика, 1980, с.66-67 | |||

| Авторское свидетельство СССР № 764518, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для адресации блоков памяти | 1980 |

|

SU1024926A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-07-07—Публикация

1986-10-20—Подача