&

Ј

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения двух ЭВМ | 1987 |

|

SU1499360A1 |

| Устройство для контроля системы обработки данных | 1985 |

|

SU1305689A1 |

| Устройство для преобразования сейсморазведочной информации | 1987 |

|

SU1497599A1 |

| Устройство сопряжения между процессором верхнего уровня и группой процессоров нижнего уровня иерархической мультипроцессорной системы | 1990 |

|

SU1789988A1 |

| Станция локальной сети | 1990 |

|

SU1824640A1 |

| Устройство для сопряжения двух магистралей | 1990 |

|

SU1778760A1 |

| Устройство для обмена информацией между ЭВМ и периферийными устройствами | 1989 |

|

SU1777145A2 |

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1702380A1 |

| Устройство для сопряжения процессора с памятью | 1987 |

|

SU1481779A1 |

| Устройство для сопряжения магистрали ЭВМ с магистралью внешних устройств | 1984 |

|

SU1246105A1 |

Изобретение относится к устройствам вычислительной техники и может быть использовано в вычислительных многомашинных системах для сопряжения ЭВМ. Цель изобретения - повышение быстродействия, за счет сокращения времени на программ- ные операции при записи и чтении информации из оперативной памяти. Устройство содержит блок приемников, блок передатчиков, блок приемопередатчиков, счетчик адреса, блок оперативной памяти, коммутатор, элемент сравнения, элемент задержки, блок приемников без управления, девять элементов И, шесть триггеров, четыре элемента НЕ, два элемента И-НЕ, три элемента ИЛИ. Зил.

Изобретение относится к устройствам вычислительной техники и может быть использовано в вычислительных многомашинных системах для сопряжения ЭВМ.

Целью изобретения является повышение быстродействия за счет сокращения времени на программные операции при записи и чтении информации в/из оперативной памяти.

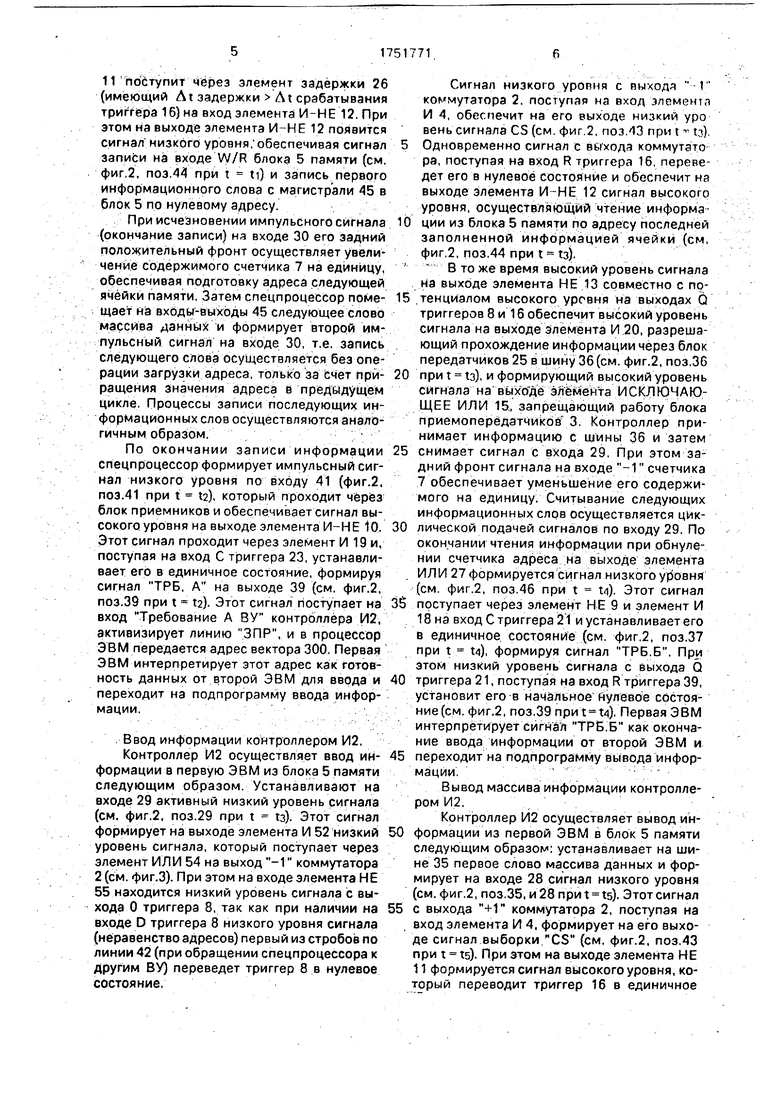

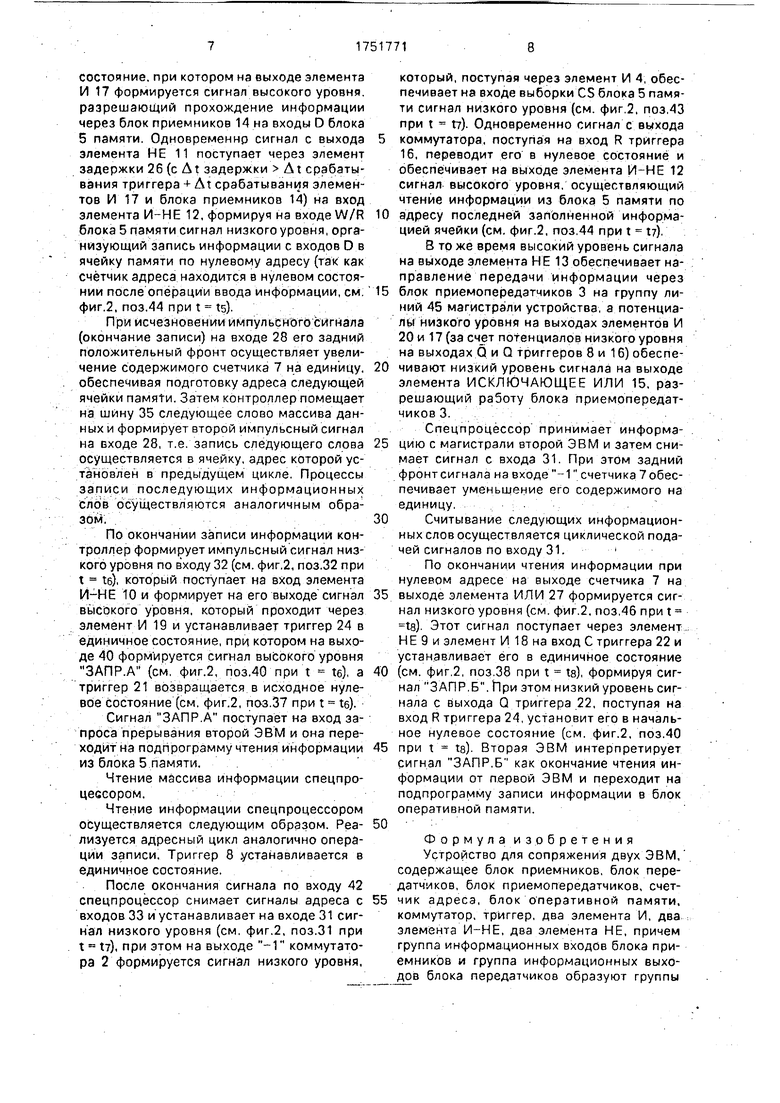

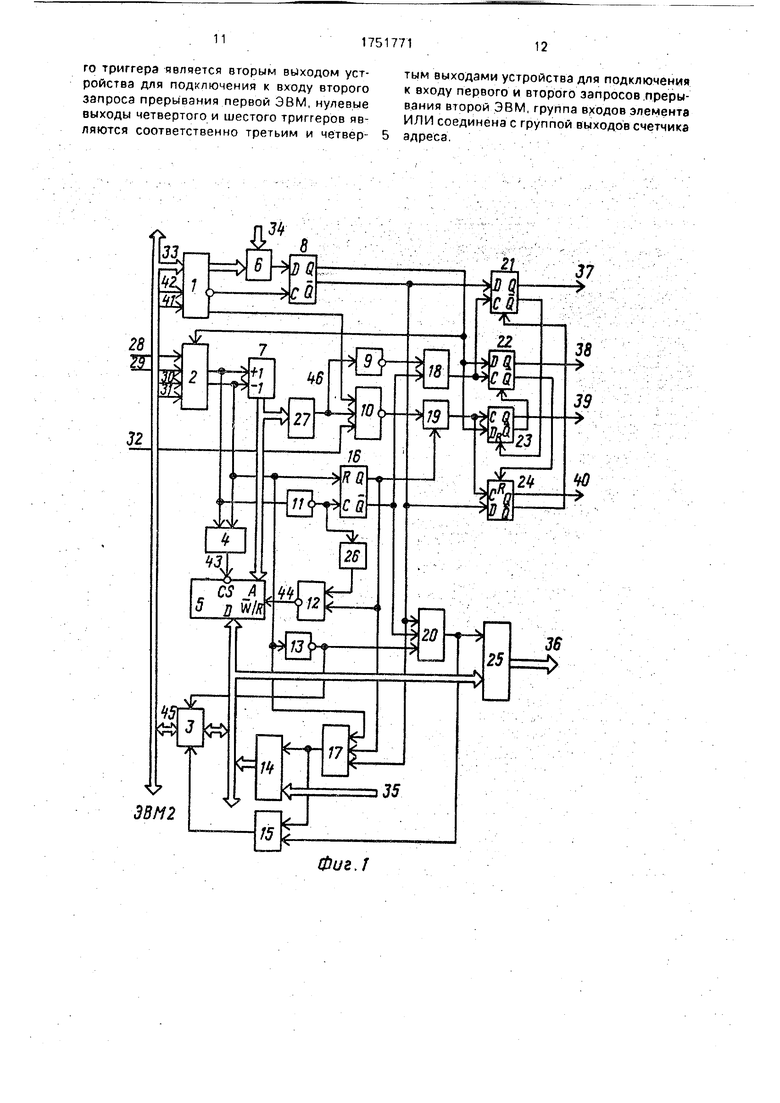

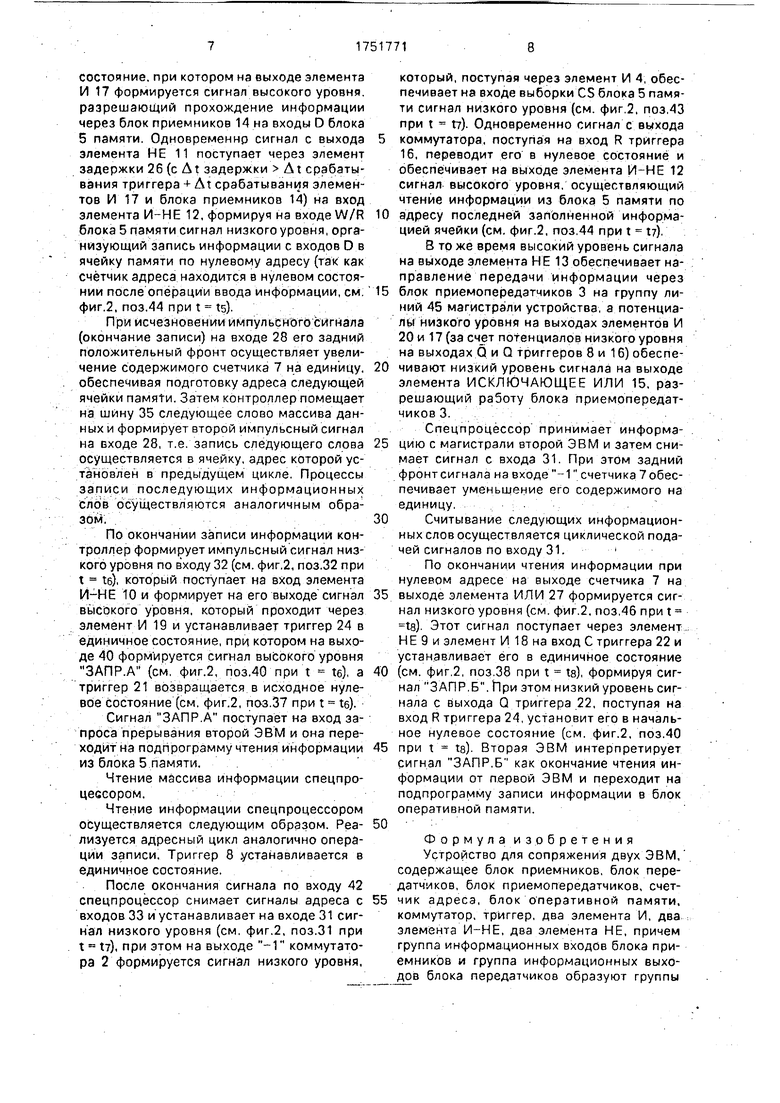

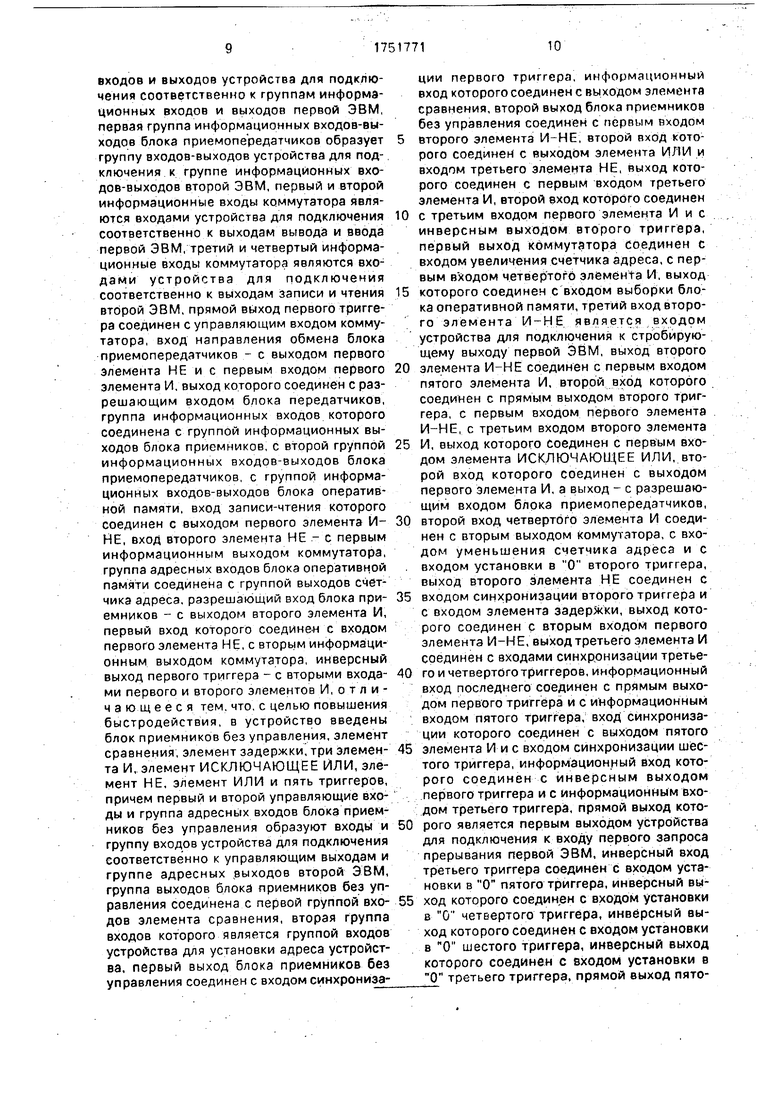

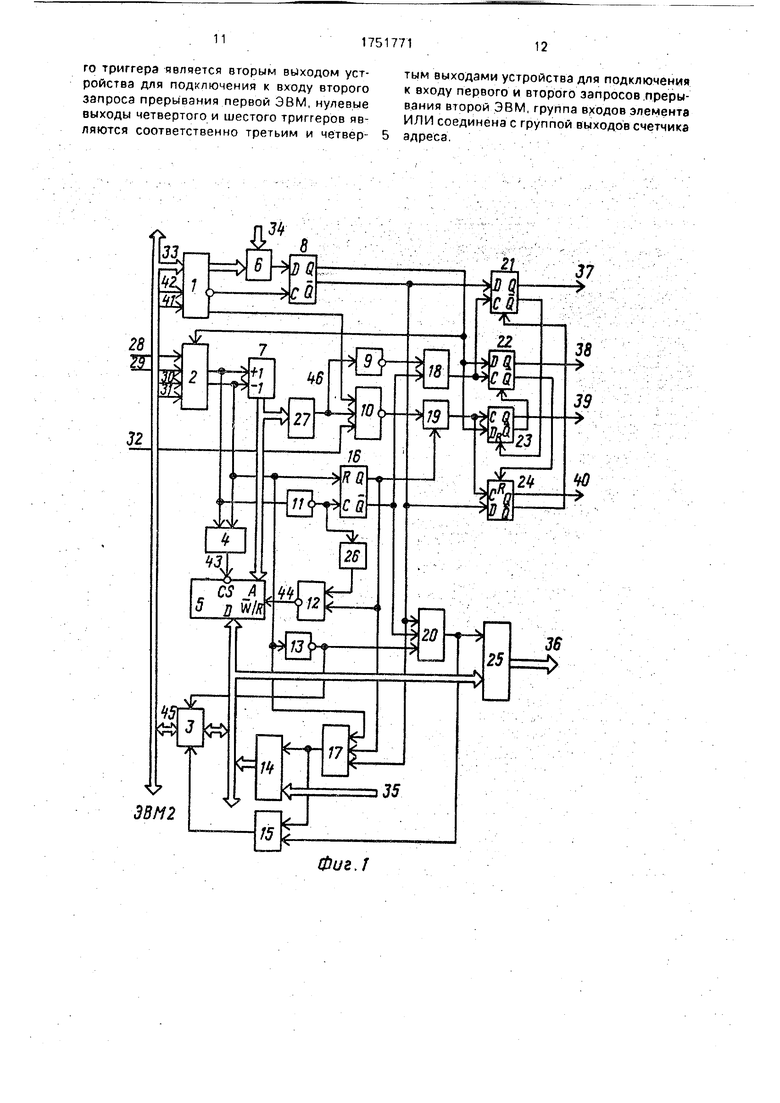

На фиг.1 приведена структурная схема устройства; на фиг.2 - временные диаграммы работы элементов устройства; на фиг.З - коммутатор.

Устройство содержит блок 1 приемников без управления (например, типа 559ИП2), коммутатор 2, блок 3 приемопередатчиков (например, типа 559ИП1 и 559ИП2), третий элемент И 4, блок 5 оперативной памяти (например, типа 537РУ9), элемент 6 сравнения, счетчик 7 адреса (например, серии 155ИЕ5, ИЕ7 или аналогичный), первый триггео 8, третий элемент НЕ 9, второй элемент И-НЁ 10, второй элемент НЕ 11, первый элемент И-НЕ 12, первый элемент НЕ 13, блок 14 приемников, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 15, второй триггер 16, второй элемент И 17, четвертый элемент И 18, пятый элемент И 19, первый элемент И 20, третий, четвертый, пятый и шестой триггеры 21-24, блок 25 передатчиков (например, типа 559ИП1), элемент 26 задержки, элемент ИЛИ 27, линию 28 сигнала Вывод, линию 29 сигнала Ввод, линию 30 сигнала Запись, линию 31 сигнала Чтение, линию 32 сигнала Конец операции ЭВМ 1 группу 33 линий адреса, группу 34 линий Установка адреса, группу 35 линий Данные вх, группу 36 линий Данные вых, линию 37 сигнала ТРББ, линию 38 сигнала Запр.Б, линию 39 сигнала ТРБ.А, линию 40 сигнала Запр.А, линию 41 сигнала Конец операции ЭВМ 2,

VJ

сл ч

ч|

линию 42 сигнала Строб адр., линию 43 сигнала CS, линию 44 сигнала W/R, шину 45 данных, линию 46 сигнала Адрес 6.

На фиг.2 обозначения позиций соответствуют номерам линий на фиг.4.

На фиг.З обозначены магистральные приемники 47, 48, элементы И 49-52, элементы ИЛИ 53, 54, элемент НЕ 55.

Работу устройства рассмотрим на примере обмена массивами информации между контроллером И23.858.383 из состава первой ЭВМ типа Электроника-60 и спецпроцессором второй ЭВМ, подключаемым к магистрали устройства. При этом группу входов 35 подключают к выходным инфор- мационным линиям контроллера И2, группу выходов 36 - к входным информационным линиям контроллера И2,-вход 32 - к выходу разряда РСОО регистра состояния контроллера, вход 28 - к линии Вывод данных, вход 29 - к линии Ввод данных, выходы 37 и 39 - к линиям соответственно Требование Б ВУ и Требование А ВУ контроллера И2. Группу входов 33 магистрали устройства подключают к адресным линиям, а входы 42 и 41 - к управляющим выходам спецпроцессора,

Входы S всех триггеров соединяют с потенциалом Лог.1, группу входов-выходов 45 - к информационным цепям магист- рали 26.

Линии 38 и 40 подключают к входам запросов прерывания спецпроцессора второй ЭВМ. Информационный вход D триггера 16 соединяют с потенциалом Лог.1(+5В через резистор 1 Ком).

После включения питания спецпроцессор формирует сигнал Установка, который поступает на .входы установки в ноль (R) триггеров 8, 16, 21-24 и счетчика 7 и уста- навливает их в нулевое состояние (линии установки на фиг.1 не показаны). При этом на выходах 0 триггеров 8,16, 21-24 и группе линий D счетчика 7 установятся сигналы низкого уровня.

Первая и вторая ЭВМ перед началом обмена устанавливают сигналы разрешения прерывания, в первой ЭВМ устанавливаются в регистре состояний контроллера И2 разряды РС05 и. РС06, во второй ЭВМ устанавливаются разрешающие сигналы в схеме обработки прерываний.

Устройство работает в четырех режимах: запись массива информации спецпроцессором, ввод массива информации контроллером ,12. вывод массива информации контроллером 112, чтение массива информации спецпроцессором.

Запись массива информации спецпроцессором.

Спецпроцессор ЭВМ 2 устанавливает на линиях 22 магистрали адрес устройства. Адрес поступает с магистрали по шине 33 на входы блока приемников 1, использующего для согласования входных сигналов магистрали. С выходов блока приемников сигналы адреса (см, фиг.2, поз.33-45) поступают на первую группу входов элемента 6 сравнения, где сравниваются с группой сигналов, установленных на входах 34. При равенстве сигналов на выходе элемента 6 сравнения формируется сигнал высокого уровня, который поступает на информационный вход D триггера 8. Затем с задержкой относительно адресных сигналов спецпроцессор формирует импульсный сигнал низкого уровня по входу 42, (см. фиг.2, поз.42), при этом на выходе блока приемников 1 без управления появляется сигнал высокого уровня, осуществляющий установку триггера 8 в единичное состояние, при этом на выходе Q триггера 8 появится потенциал высокого уровня, который, поступая на управляющий вход коммутатора 2, разрешит прохождение сигналов с входов 30 и 31 магистрали устройства.

На выходах коммутатора 2 находятся сигналы высокого уровня, которые определяют высокие (неактивные) уровни сигналов на входах CS и W/R блока памяти 5. На выходах элементов И 17, 20 присутствуют низкие уровни сигналов, которые определяют низкий уровень сигнала на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 15, разрешающий прохождение информации через блок приемопередатчиков 3, при этом низкий уровень сигнала на выходе элемента НЕ 13 определяет направление поступления информации от линии 45 магистрали к блоку памяти. После окончания сигнала по входу 42 спецпроцессор снимает сигналы адреса с входом 33 и устанавливает на входах-выходах 45 первое слово массива данных. Затем с задержкой на время распространения информации с входов-выходов 45 до входов-выходов D блока 5 спецпроцессор формирует сигнал низкого уровня на входе 30 (см. фиг.2, поз.30 при t ч). При этом на выходе 1 коммутатора 2 формируются импульсы сигнала низкого уровня, который, поступая через элемент И 4, обеспечивает на входе выборки CS блока 5 памяти сигнал- низкого уровня (см, фиг.2, поз.43 при t ti). Кроме того, сигнал низкого уровня с первого выхода коммутатора 2, поступая через элемент НЕ 11 высоким уровнем на вход С триггера 16, переведет триггер 16 в единичное состояние, при котором на выходе Q появится потенциал высокого уровня. Сигнал высокого уровня с выхода элемента НЕ

11 поступит через элемент задержки 26 (имеющий At задержки At срабатывания триггера 16) на вход элемента И-НЕ 12. При этом на выходе элемента И-НЕ 12 появится сигнал низкого уровня;обеспечивая сигнал записи на входе W/R блока 5 памяти (см. фиг.2, поз.44 при t ti) и запись первого информационного слова с магистрали 45 в блок 5 по нулевому адресу.

При исчезновении импульсного сигнала (окончание записи) на входе 30 его задний положительный фронт осуществляет увеличение содержимого счетчика 7 на единицу, обеспечивая подготовку адреса следующей ячейки памяти. Затем спецпроцессор поме- щает на входы-выходы 45 следующее слово массива данных и формирует второй импульсный сигнал на входе 30, т.е. запись следующего слова осуществляется без операции загрузки адреса, только за счет при- ращения значения адреса в предыдущем цикле. Процессы записи последующих информационных слов осуществляются аналогичным образом.

По окончании записи информации спецпроцессор формирует импульсный сигнал низкого уровня по входу 41 (фиг.2. поз.41 при t ts), который проходит через блок приемников и обеспечивает сигнал высокого уровня на выходе элемента И-НЕ 10. Этот сигнал проходит через элемент И 19 и, поступая на вход С триггера 23, устанавливает его в единичное состояние, формируя сигнал ТРБ, А на выходе 39 (см. фиг.2, поз.39 при t 12). Этот сигнал поступает на вход Требование А ВУ контроллера И2, активизирует линию ЗПР, и в процессор ЭВМ передается адрес вектора 300, Первая ЭВМ интерпретирует этот адрес как готовность данных от второй ЭВМ для ввода и переходит на подпрограмму ввода информации.

Ввод информации контроллером И2.

Контроллер И2 осуществляет ввод ин- формации в первую ЭВМ из блока 5 памяти следующим образом. Устанавливают на входе 29 активный низкий уровень сигнала (см. фиг,2, поз.29 при t 13). Этот сигнал формирует на выходе элемента И 52 низкий уровень сигнала, который поступает через элемент ИЛИ 54 на выход -1 коммутатора 2 (см. фиг.З). При этом на входе элемента НЕ 55 находится низкий уровень сигнала с выхода 0 триггера 8, так как при наличии на входе D триггера 8 низкого уровня сигнала (неравенство адресов) первый из стробов по линии 42 (при обращении спецпроцессора к другим ВУ) переведет триггер 8 в нулевое состояние,

Сигнал низкого уровня с выходя 1 коммутатора 2. поступая на вход элемента И 4, обеспечит на его выходе низкий уро вень сигнала CS (см. фиг 2, поз 43 при t - t) Одновременно сигнал с выходя коммутато ра, поступая на вход R триггера 16, переведет его в нулевое состояние и обеспечит на выходе элемента И-НЕ 12 сигнал высокого уровня, осуществляющий чтение информации из блока 5 памяти по адресу последней заполненной информацией ячейки (см, фиг.2, поз.44 при t ts).

В то же время высокий уровень сигнала на выходе элемента НЕ 13 совместно с потенциалом высокого уровня на выходах Q триггеров 8 и 16 обеспечит высокий уровень сигнала на выходе элемента И 20, разрешающий прохождение информации через блок передатчиков 25 в шину 36(см. фиг.2, поз,36 при t ta), и формирующий высокий уровень сигнала на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 15, запрещающий работу блока приемопередатчиков 3. Контроллер принимает информацию с шины 36 и затем снимает сигнал с входа 29. При этом задний фронт сигнала на входе -1 счетчика 7 обеспечивает уменьшение его содержимого на единицу. Считывание следующих информационных слов осуществляется циклической подачей сигналов по входу 29. По окончании чтения информации при обнулении счетчика адреса на выходе элемента ИЛИ 27 формируется сигнал низкого уровня (см. фиг.2, поз.46 при t 14). Этот сигнал поступает через элемент НЕ 9 и элемент И 18 на вход С триггера 21 и устанавливает его в единичное состояние (см. фиг.2, поз.37 при t t), формируя сигнал ТРБ.Б. При этом низкий уровень сигнала с выхода Q триггера 21, поступая на вход R триггера 39, установит его в начальное нулевое состояние (см. фиг,2, no3.39npnt t4). Первая ЭВМ интерпретирует сигнал ТРБ.Б как окончание ввода информации от второй ЭВМ и переходит на подпрограмму вывода информации.

Вывод массива информации контроллером И2.

Контроллер И2 осуществляет вывод информации из первой ЭВМ в блок 5 памяти следующим образом: устанавливает на шине 35 первое слово массива данных и формирует на входе 28 сигнал низкого уровня (см. фиг.2, поз.35,и28приг 15). Этот сигнал с выхода и+1 коммутатора 2, поступая на вход элемента И 4, формирует на его выходе сигнал выборки CS (см. фиг.2, поз.43 при t ts). При этом на выходе элемента НЕ 11 формируется сигнал высокого уровня, который переводит триггер 16 в единичное

состояние, при котором на выходе элемента И 17 формируется сигнал высокого уровня, разрешающий прохождение информации через блок приемников 14 на входы D блока 5 памяти. Одновременнр сигнал с выхода элемента НЕ 11 поступает через элемент задержки 26 (с At задержки At срабатывания триггера + At срабатывания элементов И 17 и блока приемников 14) на вход элемента И-НЕ 12, формируя на входе W/R блока 5 памяти сигнал низкого уровня, организующий запись информации с входов D в ячейку памяти по нулевому адресу (так как счётчик адреса находится в нулевом состоянии после операции ввода информации, см. фиг.2, поз.44 при t ts).

При исчезновении импульсного сигнала (окончание записи) на входе 28 его задний положительный фронт осуществляет увеличение содержимого счетчика 7 на единицу, обеспечивая подготовку адреса следующей ячейки памяти. Затем контроллер помещает на шину 35 следующее слово массива данных и формирует второй импульсный сигнал на входе 28, т.е. запись следующего слова осуществляется в ячейку, адрес которой установлен в предыдущем цикле. Процессы записи последующих информационных слов осуществляются аналогичным образом,

По окончании записи информации контроллер формирует импульсный сигнал низкого уровня по входу 32 (см. фиг.2, поз.32 при t te). который поступает на вход элемента И-НЕ 10 и формирует на его выходе сигнал высокого уровня, который проходит через элемент И 19 и устанавливает триггер 24 в единичное состояние, при котором на выходе 40 формируется сигнал высокого уровня ЗАПР.А (см, фиг.2, поз.40 при t te), a триггер 21 возвращается в исходное нулевое состояние (см. фиг.2, поз.37 при t te).

Сигнал ЗАПР.А поступает на вход запроса прерывания второй ЭВМ и она переходит на подпрограмму чтения информации из блока 5 памяти.

Чтение массива информации спецпроцессором.

Чтение информации спецпроцессором осуществляется следующим образом. Реализуется адресный цикл аналогично операции записи. Триггер 8 устанавливается в единичное состояние.

После окончания сигнала по входу 42 спецпроцессор снимает сигналы адреса с входов 33 и устанавливает на входе 31 сигнал низкого уровня (см. фиг.2, поз.31 при t t), при этом на выходе -1 коммутатора 2 формируется сигнал низкого уровня,

который, поступая через элемент И 4, обеспечивает на входе выборки CS блока 5 памяти сигнал низкого уровня (см. фиг.2, поз,43 при t t). Одновременно сигнал с выхода

коммутатора, поступая на вход R триггера 16, переводит его в нулевое состояние и обеспечивает на выходе элемента И-НЕ 12 сигнал высокого уровня, осуществляющий чтение информации из блока 5 памяти по

0 адресу последней заполненной информацией ячейки (см. фиг.2, поз.44 при t 17).

В то же время высокий уровень сигнала на выходе элемента НЕ 13 обеспечивает направление передачи информации через

5 блок приемопередатчиков 3 на группу линий 45 магистрали устройства, а потенциалы низкого уровня на выходах элементов И 20 и 17 (за счет потенциалов низкого уровня на выходах Q и Q триггеров 8 и 16) обеспе0 чивают низкий уровень сигнала на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 15, разрешающий работу блока приемопередатчиков 3.

Спецпроцессор принимает информа5 цию с магистрали второй ЭВМ и затем снимает сигнал с входа 31. При этом задний фронт сигнала на входе -1 счетчика 7 обеспечивает уменьшение его содержимого на единицу.

0 Считывание следующих информационных слов осуществляется циклической подачей сигналов по входу 31.

По окончании чтения информации при нулевом адресе на выходе счетчика 7 на

5 выходе элемента ИЛИ 27 формируется сигнал низкого уровня (см. фиг.2. поз,46 при t ta) Этот сигнал поступает через элемент НЕ 9 и элемент И 18 на вход С триггера 22 и устанавливает его в единичное состояние

0 (см. фиг.2, поз 38 при t ts), формируя сигнал ЗАПР.Б. При этом низкий уровень сигнала с выхода Q триггера 22, поступая на вход R триггера 24, установит его в начальное нулевое состояние (см. фиг.2, поз.40

5 при t ts). Вторая ЭВМ интерпретирует сигнал ЗАПР.Б как окончание чтения информации от первой ЭВМ и переходит на подпрограмму записи информации в блок оперативной памяти.

0

Формула изобретения Устройство для сопряжения двух ЭВМ, содержащее блок приемников, блок передатчиков, блок приемопередатчиков, счет5 чик адреса, блок оперативной памяти, коммутатор, триггер, два элемента И, два элемента И-НЕ, два элемента НЕ, причем группа информационных входов блока приемников и группа информационных выходов блока передатчиков образуют группы

входов и выходов устройства для подключения соответственно к группам информационных входов и выходов первой ЭВМ, первая группа информационных входов-выходов блока приемопередатчиков образует группу входов-выходов устройства для подключения к группе информационных входов-выходов второй ЭВМ, первый и второй информационные входы коммутатора являются входами устройства для подключения соответственно к выходам вывода и ввода первой ЭВМ, третий и четвертый информационные входы коммутатора являются входами устройства для подключения соответственно к выходам записи и чтения второй ЭВМ, прямой выход первого триггера соединен с управляющим входом коммутатора, вход направления обмена блока приемопередатчиков - с выходом первого элемента НЕ и с первым входом первого элемента И, выход которого соединен с разрешающим входом блока передатчиков, группа информационных входов которого соединена с группой информационных выходов блока приемников, с второй группой информационных входов-выходов блока приемопередатчиков, с группой информационных входов-выходов блока оперативной памяти, вход записи-чтения которого соединен с выходом первого элемента И- НЕ, вход второго элемента НЕ - с первым информационным выходом коммутатора, группа адресных входов блока оперативной памяти соединена с группой выходов счетчика адреса, разрешающий вход блока приемников - с выходом второго элемента И, первый вход которого соединен с входом первого элемента НЕ, с вторым информационным выходом коммутатора, инверсный выход первого триггера - с вторыми входами первого и второго элементов И, о т л и - чающееся тем, что. с целью повышения быстродействия, в устройство введены блок приемников без управления, элемент сравнения, элемент задержки, три элемента И, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент НЕ, элемент ИЛИ и пять триггеров, причем первый и второй управляющие входы и группа адресных входов блока приемников без управления образуют входы и группу входов устройства для подключения соответственно к управляющим выходам и группе адресных выходов второй ЭВМ, группа выходов блока приемников без управления соединена с первой группой входов элемента сравнения, вторая группа входов которого является группой входов устройства для установки адреса устройства, первый выход блока приемников без управления соединен с входом синхрониэации первого триггера, информационный вход которого соединен с выходом элемента сравнения, второй выход блока приемников без управления соединен с первым входом 5 второго элемента И-НЕ, второй вход которого соединен с выходом элемента ИЛИ и входом третьего элемента НЕ, выход которого соединен с первым входом третьего элемента И, второй вход которого соединен

0 с третьим входом первого элемента И и с инверсным выходом второго триггера, первый выход коммутатора соединен с входом увеличения счетчика адреса, с первым входом четвертого элемента И, выход

5 которого соединен с входом выборки блока оперативной памяти, третий вход второго элемента И-НЕ является входом устройства для подключения к стробирую- щему выходу первой ЭВМ, выход второго

0 элемента И-НЕ соединен с первым входом пятого элемента И, второй вход которого соединен с прямым выходом второго триггера, с первым входом первого элемента И-НЕ, с третьим входом второго элемента

5 И, выход которого соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с выходом первого элемента И, а выход - с разрешающим входом блока приемопередатчиков,

0 второй вход четвертого элемента И соединен с вторым выходом коммутатора, с входом уменьшения счетчика адреса и с входом установки в О второго триггера, выход второго элемента НЕ соединен с

5 входом синхронизации второго триггера и с входом элемента задержки, выход которого соединен с вторым входом первого элемента И-НЕ, выход третьего элемента И соединен с входами синхронизации третье0 го и четвертого триггеров, информационный вход последнего соединен с прямым выходом первого триггера и с информационным входом пятого триггера, вход синхронизации которого соединен с выходом пятого

5 элемента И и с входом синхронизации шестого триггера, информационный вход которого соединен с инверсным выходом первого триггера и с информационным входом третьего триггера, прямой выход кото0 рого является первым выходом устройства для подключения к входу первого запроса прерывания первой ЭВМ, инверсный вход третьего триггера соединен с входом установки в О пятого триггера, инверсный вы5 ход которого соединен с входом установки в О четвертого триггера, инверсный выход которого соединен с входом установки в О шестого триггера, инверсный выход которого соединен с входом установки в О третьего триггера, прямой выход пятого триггера является вторым выходом устройства для подключения к входу второго запроса прерывания первой ЭВМ, нулевые выходы четвертого и шестого триггеров являются соответственно третьим и четвер-

Фиг.

тым выходами устройства для подключения к входу первого и второго запросов прерывания второй ЭВМ, группа входов элемента ИЛИ соединена с группой выходов счетчика адреса

t, tz ts tif t$ ts Фие. г

t

tB

| Авторское свидетельство СССР № 760076 | |||

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Солесос | 1922 |

|

SU29A1 |

Авторы

Даты

1992-07-30—Публикация

1990-02-28—Подача