Изобретение относится к вычислительной технике, предназначено для сдвига информации на заданное число разрядов с соответствующим заполнени- ем освобождающихся позиций и с обеспечением полного контроля сдвига информации и может использоваться в ЭВМ, вычислительных устройствах и приборах цифровой автоматики (напри- мер, для построения АЛУ с плавающей запятой, умножителей, устройств деления, для выравнивания границ слов, считанных из памяти и т.д.), а также дпя построения контролируемых сдвигагелей с расширенной разрядностью.

Устройство обеспечивает принцип линейного наращивания разрядности, зг ключающийся в том, что контролируемое устройство для сдвига, конструк- тивно и технологически оформленное в виде большой интегральной схемы (БИС) является элементарной секцией, на базе которой без обрамления из дополнительных микросхем можно формировать 25 ля вдвигаемой информации, шифратор 24

сдвигающие устройства, аналогичные данному, с разрядностью, кратной раз35

-рядности секции. Объем оборудования, используемый для построения предлагаемого устройства, позволяет изгото- 30 вить его в виде БИС.

Цель изобретения - повышение достоверности контроля.

Предлагаемое устройство обеспечивает полноту контроля всех операций сдвига информации (циклического, логического и ари(|метического сдвигов) . Это достигается за счет обеспечения контро.пя входной информации, контроля сдвига информации байтами между секциями в режиме-наращивания разрядности, контроля выходной информации и контроля разрядных сдвигов информации в пределах байта как в режиме одиночной работы, так и вания разрядности.

Устройство формирует общий сигнал Ошибка при наличии сбоя в работе устройства, позволяет указать на месрезультатов контроля, блок 25 контроля сдвигаемой информации, первый и второй блоки 26 и 27 формирования четности выдвигаемой информации, группу информационных входов 28 устройства, первую группу информационных выходов 29 устройства, группу информационных выходов 30 устройства при сдвиге влево с расширенным шагом, группу информационных выходов 31 устройства при сдвиге вправо с расширенным щагом, группу информационных входов 32 при сдвиге влево с расширенным шагом, группу информационных входов 33 при сдвиге вправо с расширенна шагом, выход 34 контрольного разряда при сдвиге влево, вход 35 задания признака контрольного разряда при контроле сдвига влево, вход 36 пуска уств режиме наращи- 45 ройства, вход 37 задания режима работы устройства, вход 38 синхронизации устройства, группу входов 39 задания типа сдвига устройства, шину 40 логического нуля, левый выход 41 четности

40

то нахождения ошибки путем (юрмирова- 50 вдвигаемой информации, вход 42 задания четности левой вдвигаемой информации, левый выход 43 контроля устройства, выходы 44 общей ошибки устройства, ошибки по четности 45, приния пяти контрольных сигналов, а также обеспечивает предсказание четности сдвинутой информации.

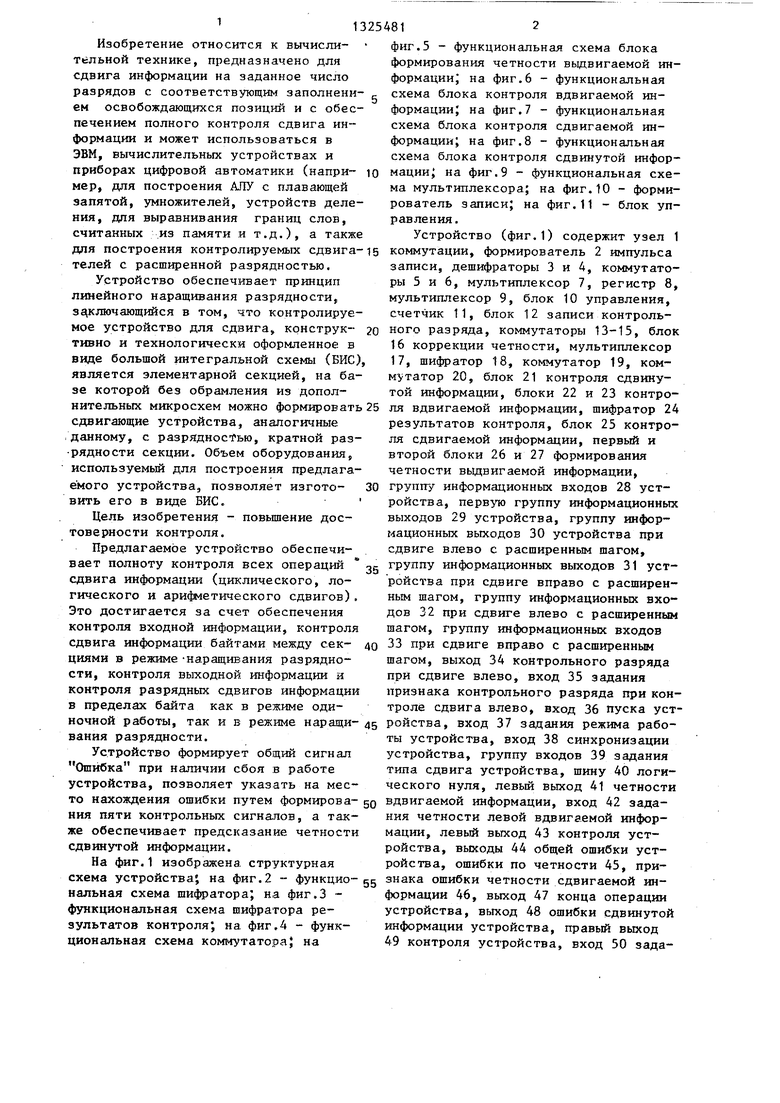

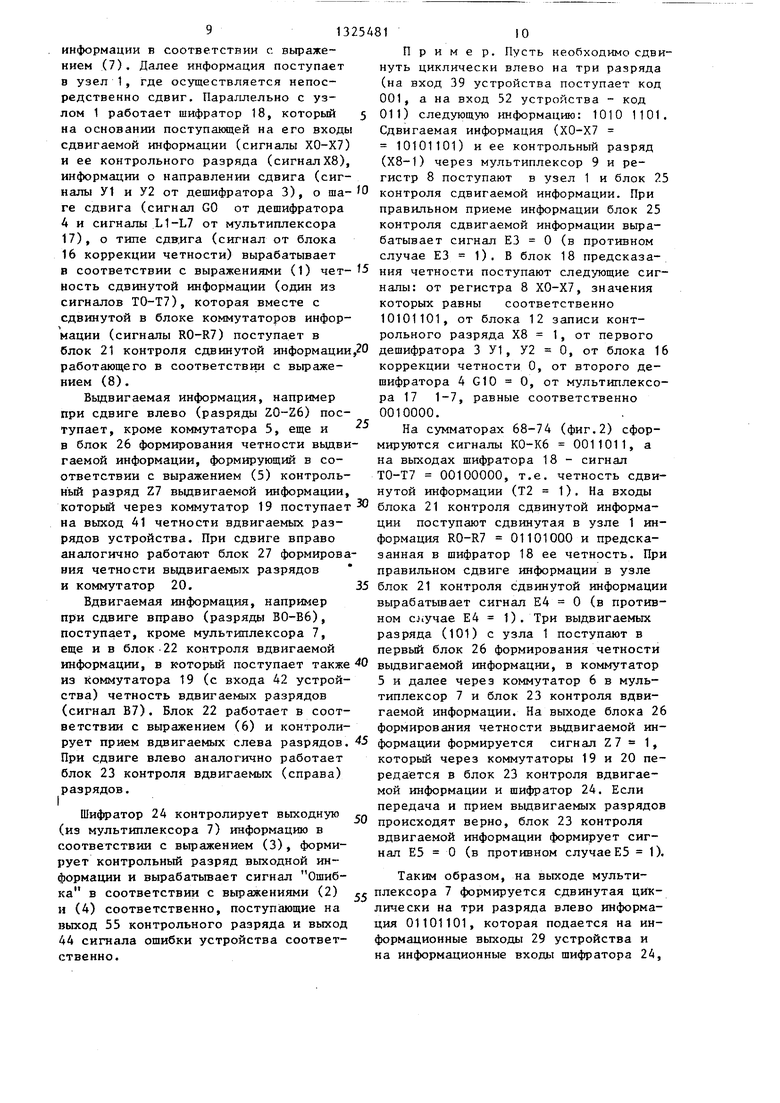

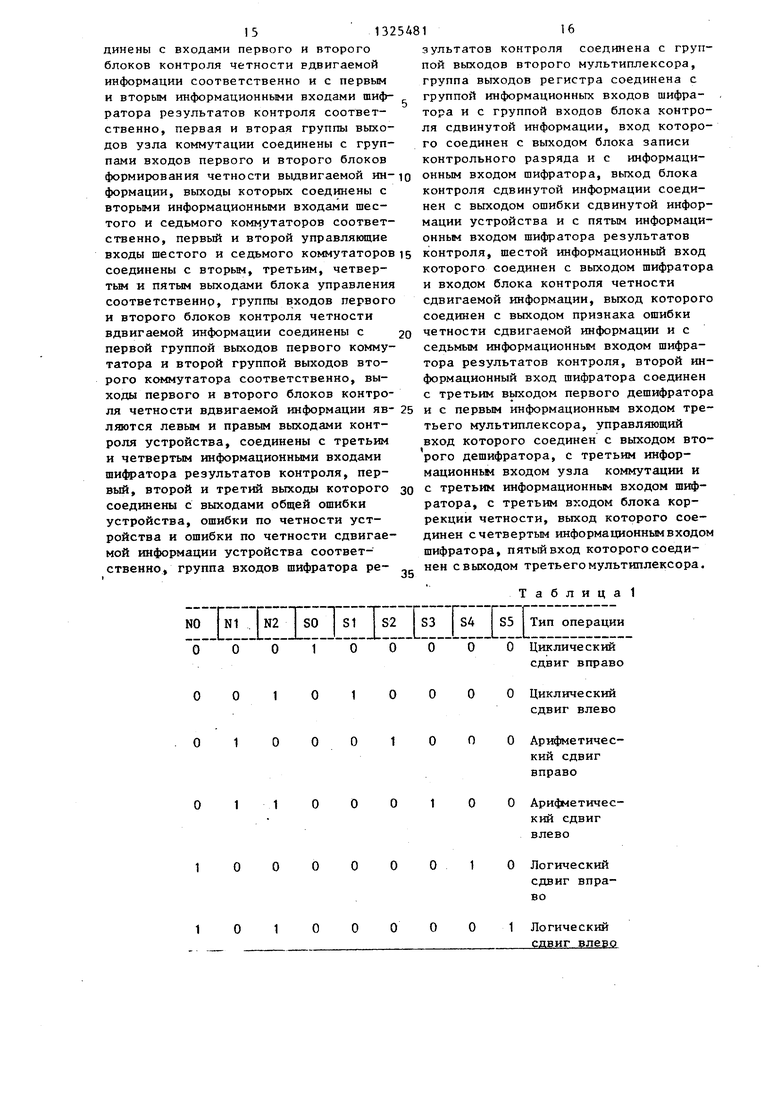

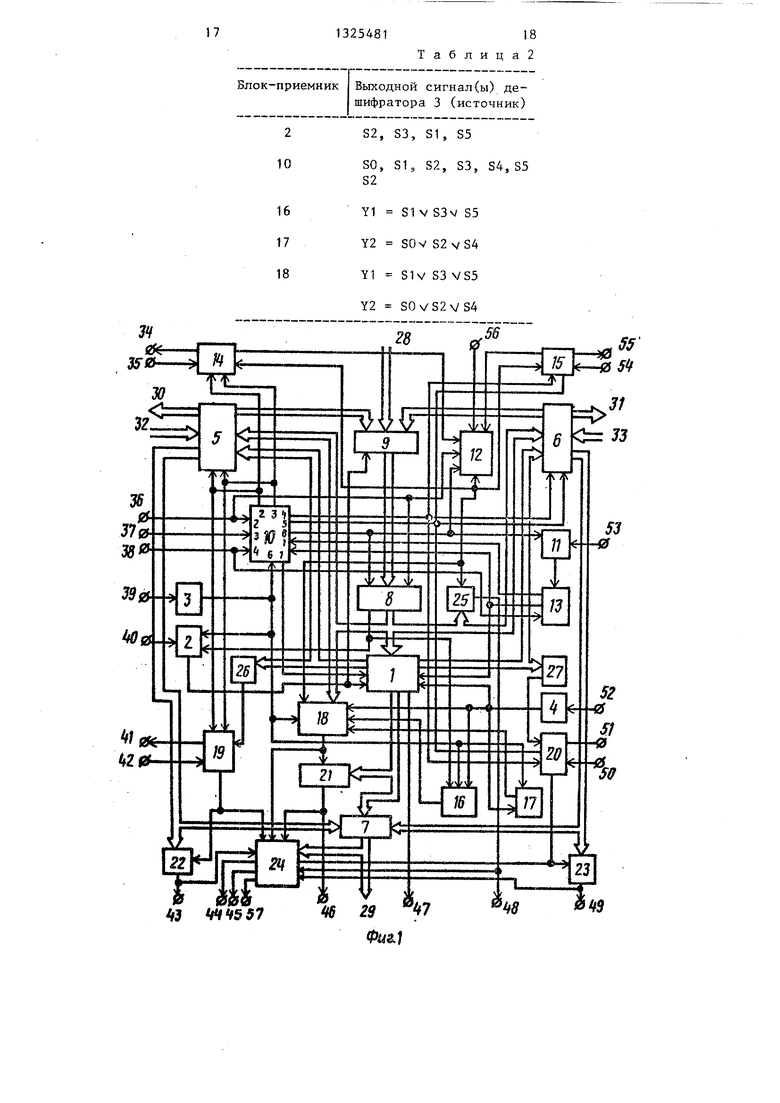

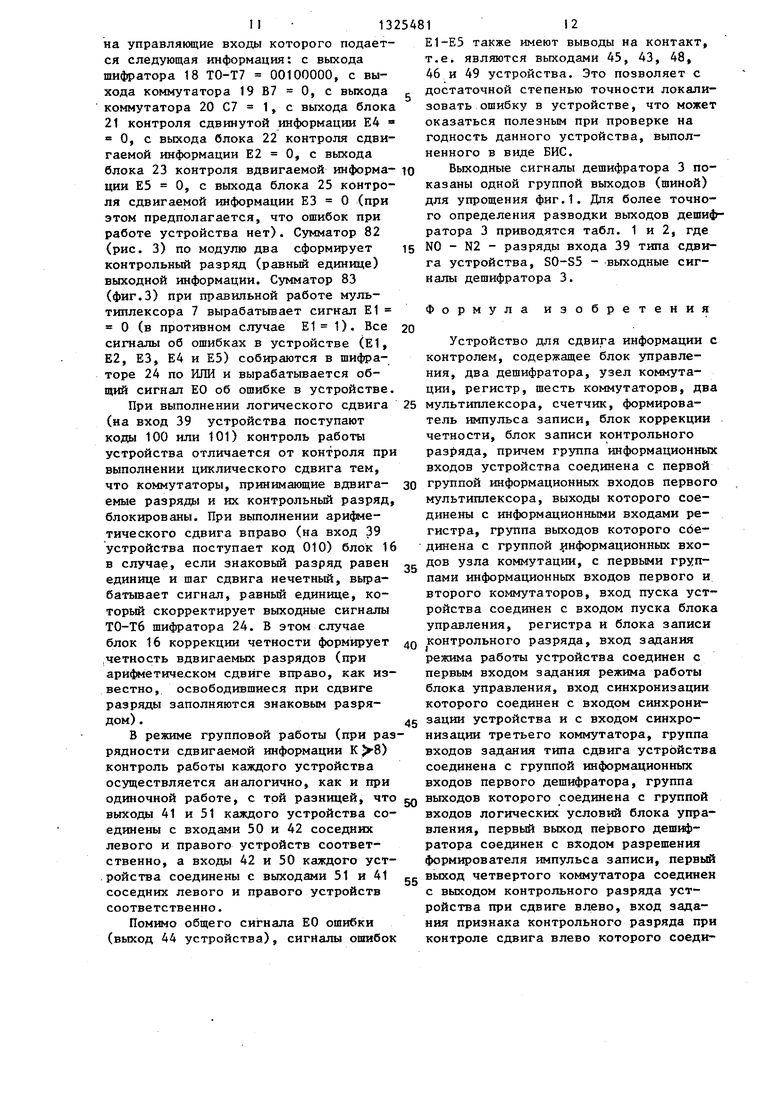

На фиг.1 изображена структурная схема устройства; на фиг.2 - функцио-55 знака ошибки четности сдвигаемой ин- нальная схема шифратора; на фиг.З - формации 46, выход 47 конца операции функциональная схема шифратора результатов контроля; на фиг,4 - функциональная схема коммутатора; на

устройства, вьпсод 48 ошибки сдвинутой информации устройства, правый выход 49 контроля устройства, вход 50 задафиг.5 - функциональная схема блока формирования четности выдвигаемой информации J на фиг.6 - функциональная схема блока контроля вдвигаемой информации; на фиг.7 - функциональная схема блока контроля сдвигаемой информации; на фиг.8 - функциональная схема блока контроля сдвинутой информации; на фиг.9 - функциональная схема мультиплексора; на фиг.10 - формирователь записи; на фиг.11 - блок управления.

Устройство (фиг.1) содержит узел 1 коммутации, формирователь 2 импульса записи, дешифраторы 3 и 4, коммутаторы 5 и 6, мультиплексор 7, регистр 8, мультиплексор 9, блок 10 управления, счетчик 11, блок 12 записи контрольного разряда, коммутаторы 13-15, блок 16 коррекции четности, мультиплексор 17, шифратор 18, коммутатор 19, коммутатор 20, блок 21 контроля сдвинутой информации, блоки 22 и 23 контрония четности левой вдвигаемой информации, левый выход 43 контроля устройства, выходы 44 общей ошибки устройства, ошибки по четности 45, признака ошибки четности сдвигаемой ин- формации 46, выход 47 конца операции

знака ошибки четности сдвигаемой ин- формации 46, выход 47 конца операции

устройства, вьпсод 48 ошибки сдвинутой информации устройства, правый выход 49 контроля устройства, вход 50 задания четности правой вдвигаемой информации, правь й выход 51 четности вдвигаемой информации устройства, группу входов 52 задания величины шага сдвига, входы 53 задания величины расширенного шага сдвига, вход 54 задания и выход 55 контрольного разряда устройства при сдвиге вправо, вход 56 задания контрольного разряда устройства, выход 57 ошибки по четности сдвигаемой информации.

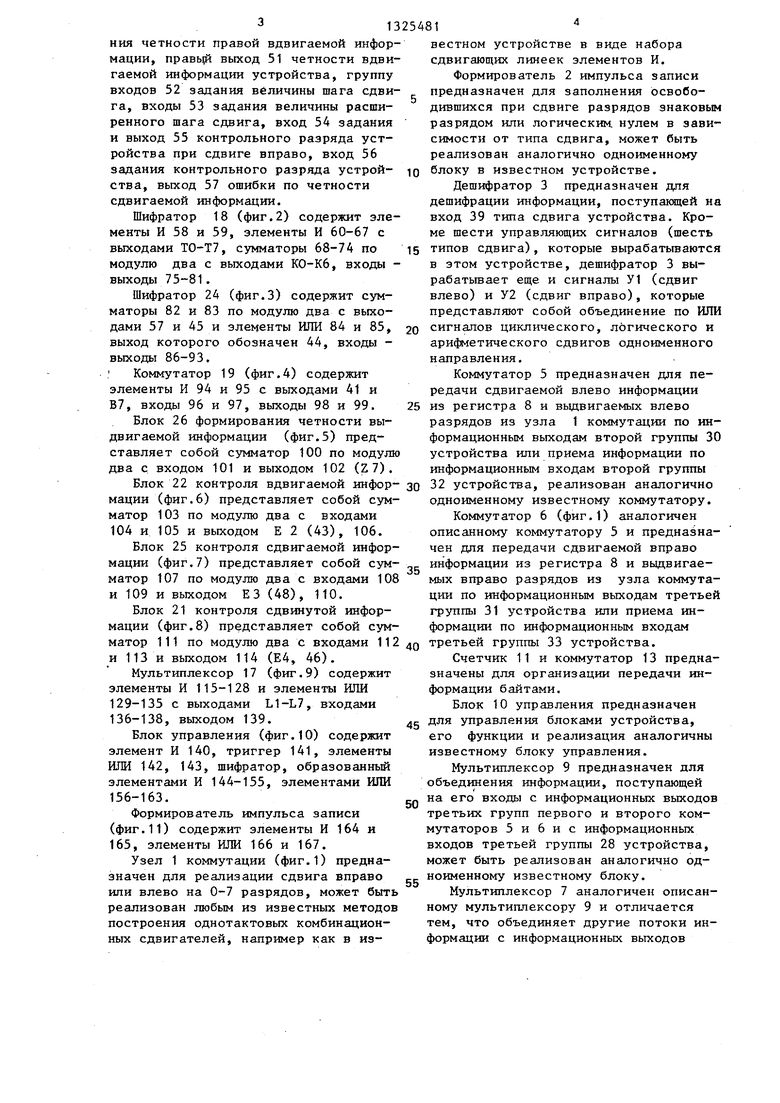

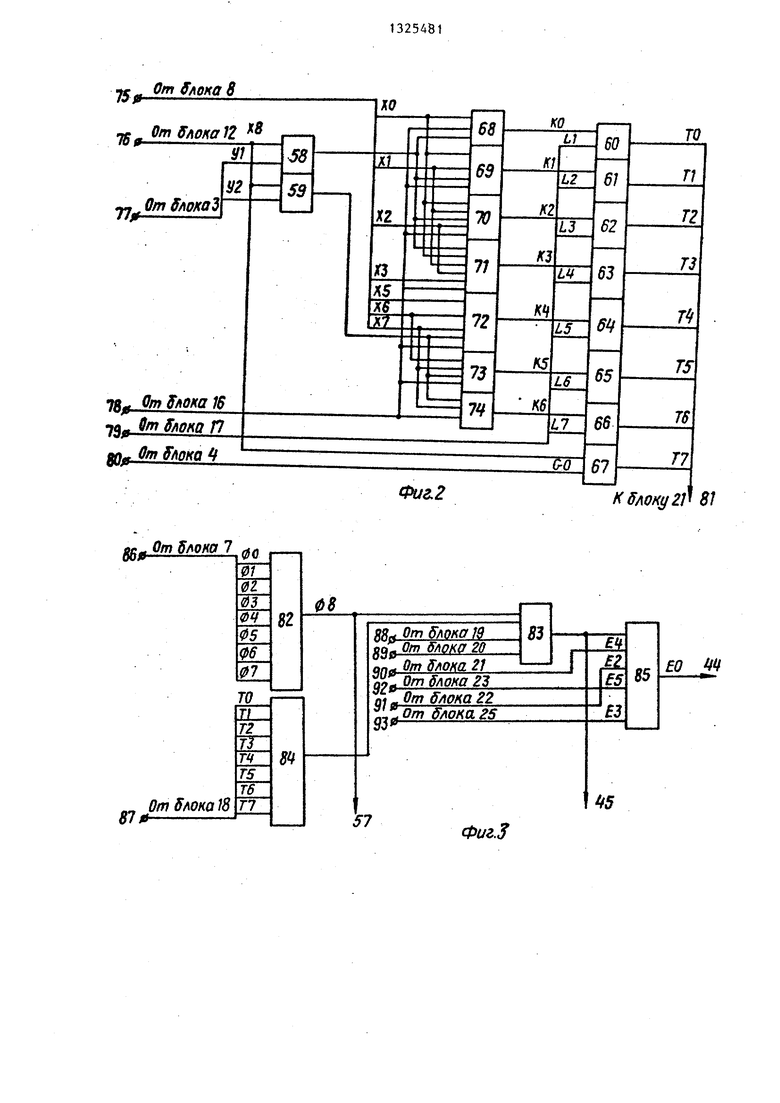

Шифратор 18 (фиг.2) содержит элементы И 58 и 59, элементы И 60-67 с выходами ТО-Т7, сумматоры 68-74 по модулю два с выходами КО-К6, входы - выходы 75-81.

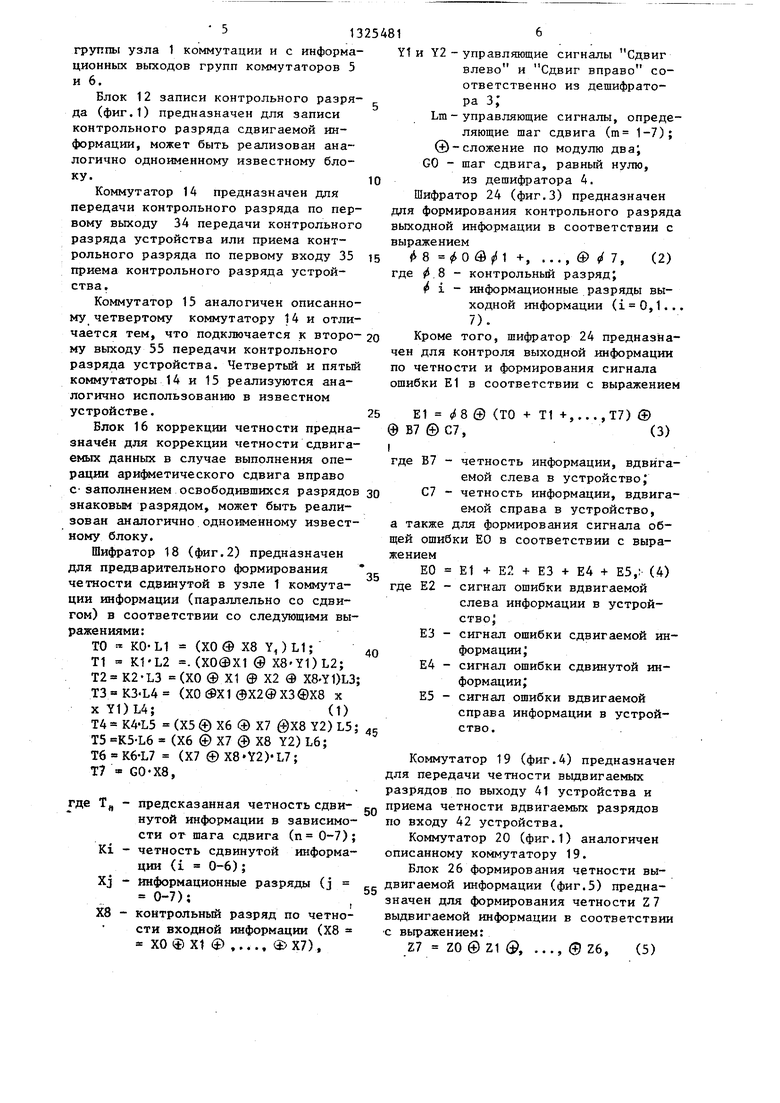

Шифратор 24 (фиг.З) содержит сумматоры 82 и 83 по модулю два с выходами 57 и 45 и элементы ИЛИ 84 и 85, выход которого обозначен 44, входы - выходы 86-93.

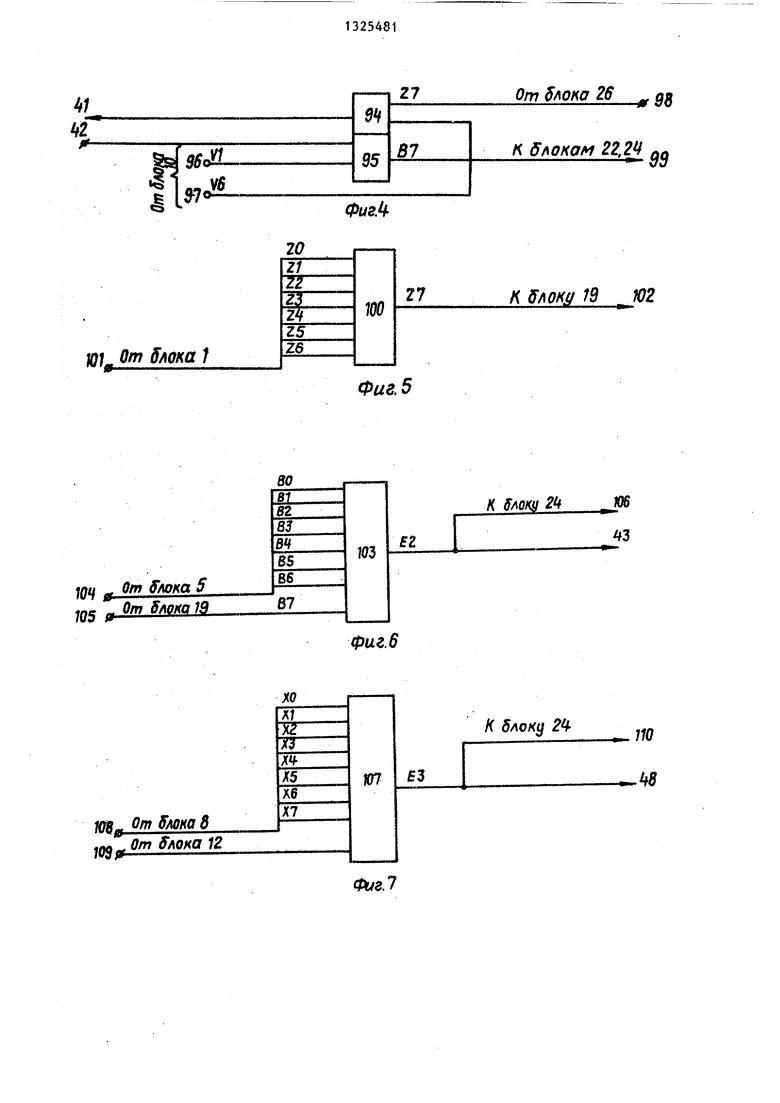

Коммутатор 19 (фиг.4) содержит элементы И 94 и 95 с выходами 41 и В7, входы 96 и 97, выходы 98 и 99.

Блок 26 формирования четности выдвигаемой информации (фиг.5) представляет собой сумматор 100 по модулю два с входом 101 и выходом 102 (Z 7) .

Блок 22 контроля вдвигаемой инфор- зо 32 устройства, реализован аналогично

мации (фиг.6) представляет собой сумматор 103 по модулю два с входами 104 и 105 и выходом Е 2 (43), 106.

Блок 25 контроля сдвигаемой информации (фиг.7) представляет собой сумматор 107 по модулю два с входами 108 и 109 и выходом ЕЗ (48), 110.

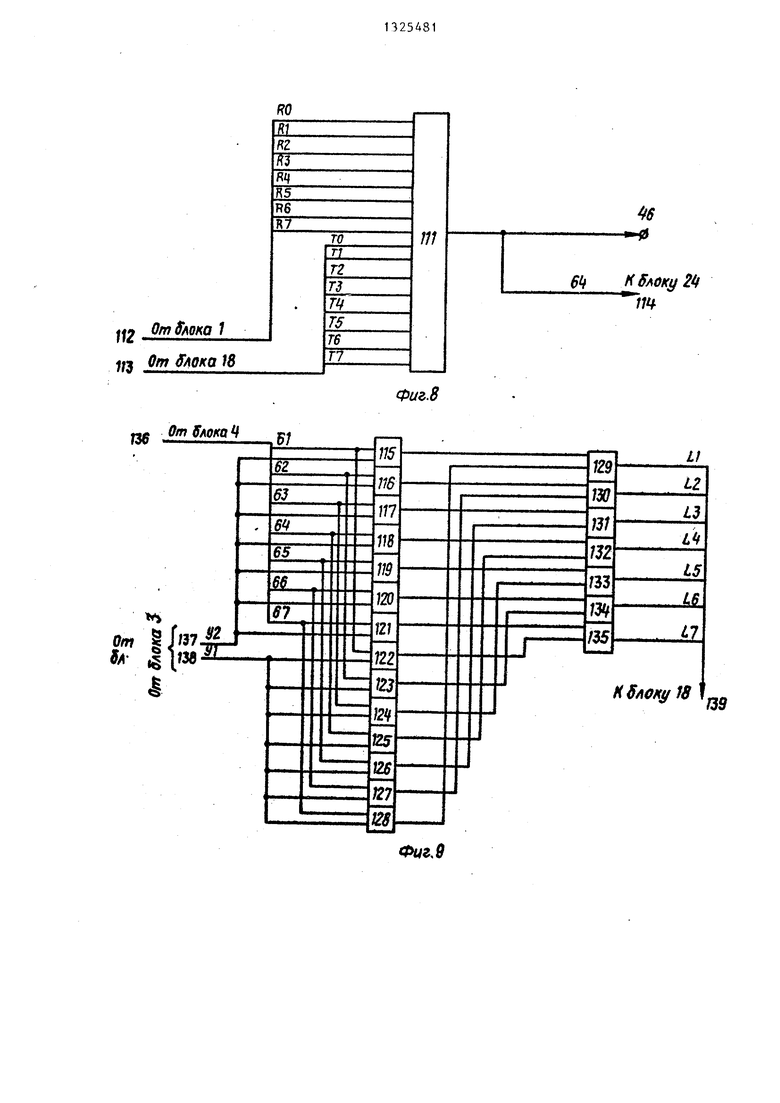

Блок 21 контроля сдвинутой информации (фиг.8) представляет собой сум35

одноименному известному коммутатору.

Коммутатор 6 (фиг.1) аналогичен описанному коммутатору 5 и предназначен для передачи сдвигаемой вправо информации из регистра 8 и выдвигаемых вправо разрядов из узла коммутации по информационным выходам третьей группы 31 устройства или приема информации по ршформационным входам

матор 111 по модулю два с входами 112 до третьей группы 33 устройства.

и 113 и выходом 114 (Е4, 46).

Мультиплексор 17 (фиг.9) содержит элементы И 115-128 и элементы ИЛИ 129-135 с выходами L1-L7, входами 136-138, выходом 139.

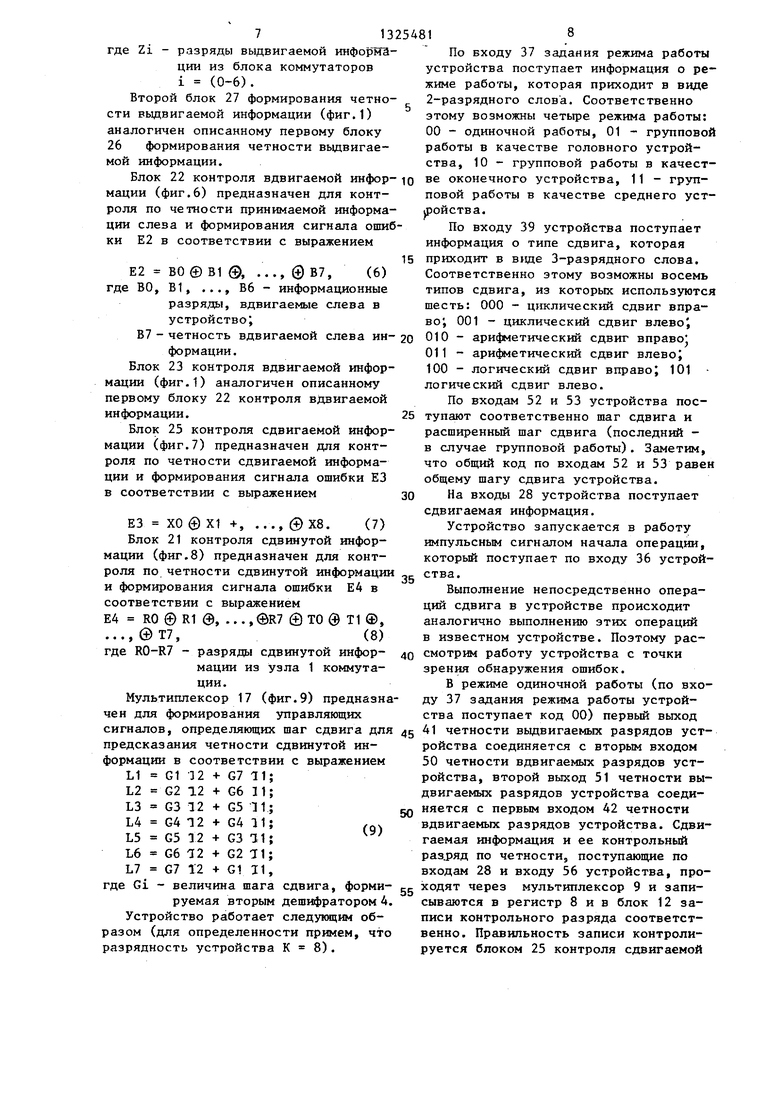

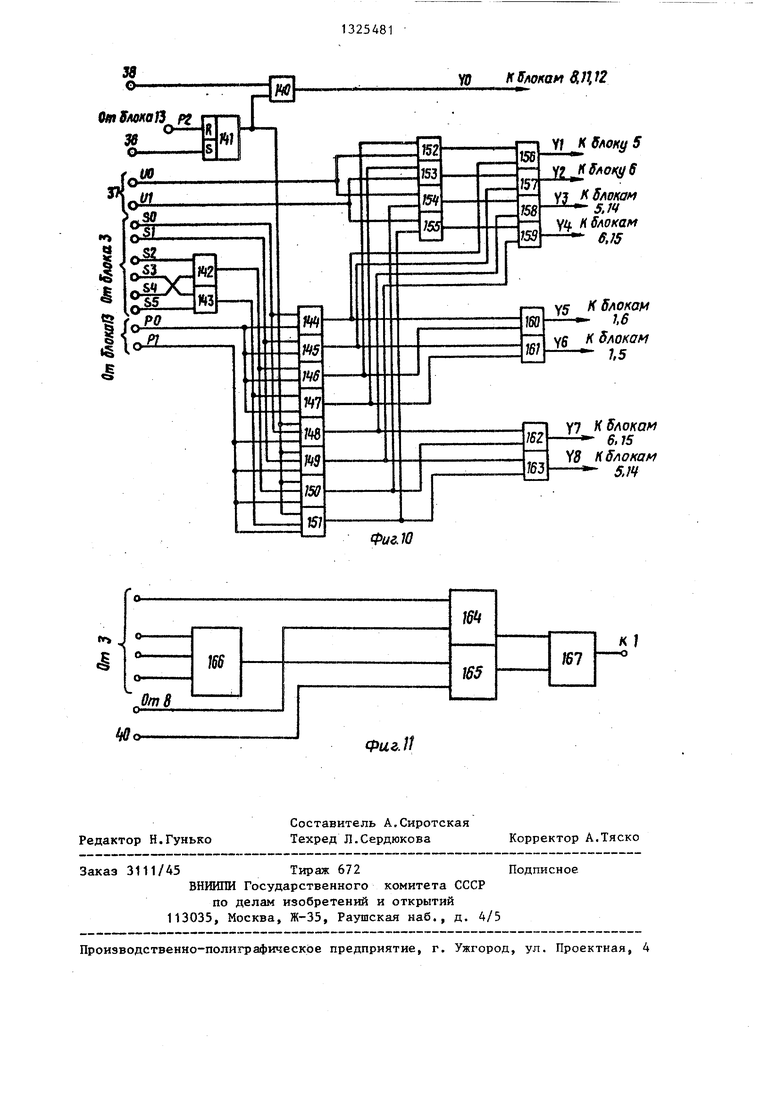

Блок управления (фиг.10) содержит элемент И 140, триггер 141, элементы ИЛИ 142, 143, шифратор, образованный элементами И 144-155, элементами ИЛИ 156-163.

Формирователь импульса записи (фиг.11) содержит элементы И 164 и 165, элементы ИЛИ 166 и 167.

Узел 1 коммутации (фиг.1) предназначен для реализации сдвига вправо или влево на 0-7 разрядов, может быть реализован любым из известных методов построения однотактовых комбинационных сдвигателей, например как в изСчетчик 11 и коммутатор 13 значены для организации переда формации байтами.

Блок 10 управления предназн 4g для управления блоками устройс его функции и реализация анал известному блоку управления.

Мультиплексор 9 предназначе объединения информации, поступ на его входы с информационных третьих групп первого и второг мутаторов 5 и 6 и с информацио входов третьей группы 28 устро может быть реализован аналогич ноименному известному блоку.

Мультиплексор 7 аналогичен ному мультиплексору 9 и отлича тем, что объединяет другие пот формации с информационных выхо

50

55

вестном устройстве в виде набора сдвигающих линеек элементов И.

Формирователь 2 импульса записи предназначен для заполнения освободившихся при сдвиге разрядов знаковым разрядом или логическим, нулем в зависимости от типа сдвига, может быть реализован аналогично одноименному

0 блоку в известном устройстве.

Дешифратор 3 предназначен для дешифрации информации, поступажнцей на вход 39 типа сдвига устройства. Кроме шести управляющих сигналов (шесть

5 типов сдвига), которые вырабатываются в этом устройстве, дешифратор 3 вы- рабатьшает еще и сигналы У1 (сдвиг влево) и У2 (сдвиг вправо), которые представляют собой объединение по ИЛИ

0 сигналов циклического, логического и арифметического сдвигов одноименного направления.

Коммутатор 5 предназначен для передачи сдвигаемой влево информации

5 из регистра 8 и вьщвигаемых влево

разрядов из узла 1 коммутации по информационным выходам второй группы 30 устройства или приема информации по информационным входам второй группы

5

одноименному известному коммутатору.

Коммутатор 6 (фиг.1) аналогичен описанному коммутатору 5 и предназначен для передачи сдвигаемой вправо информации из регистра 8 и выдвигаемых вправо разрядов из узла коммутации по информационным выходам третьей группы 31 устройства или приема информации по ршформационным входам

Счетчик 11 и коммутатор 13 предназначены для организации передачи информации байтами.

Блок 10 управления предназначен для управления блоками устройства, его функции и реализация аналогичны известному блоку управления.

Мультиплексор 9 предназначен для объединения информации, поступающей на его входы с информационных выходов третьих групп первого и второго коммутаторов 5 и 6 и с информационных входов третьей группы 28 устройства, может быть реализован аналогично одноименному известному блоку.

Мультиплексор 7 аналогичен описанному мультиплексору 9 и отличается тем, что объединяет другие потоки информации с информационных выходов

группы узла 1 коммутации и с информационных выходов групп коммутаторов 5 и 6.

Блок 12 записи контрольного разряда (фиг.1) предназначен для записи контрольного разряда сдвигаемой информации, может быть реализован аналогично одноименному известному блоку.

Коммутатор 14 предназначен для передачи контрольного разряда по первому выходу 34 передачи контрольного разряда устройства или приема контрольного разряда по первому входу 35 приема контрольного разряда устройства.

Коммутатор 15 аналогичен описанному четвертому коммутатору 14 и отличается тем, что подключается к второ- му выходу 55 передачи контрольного разряда устройства. Четвертый и пятый коммутаторы 14 и 15 реализуются аналогично использованию в известном устройстве.

Блок 16 коррекции четности предназначен для коррекции четности сдвигаемых данных в случае выполнения операции арифметического сдвига вправо с-заполнением освободившихся разрядов знаковым разрядом, может быть реализован аналогично одно менному известному блоку.

Шифратор 18 (фиг.2) предназначен для предварительного формирования четности сдвинутой в узле 1 коммута ции информации (параллельно со сдвигом) в соответствии со следующими выражениями:

ТО KO-L1 (ХО® Х8 Y,)L1;

Т1 K1 L2 . (ХОФХ1 О X8 Y1)L2;

Т2 K2 L3 (ХО ® XI ф Х2 ® X8-Y1)L3

T3 K3 L4 (ХО(9Х1 (5Х2ФХЗ®Х8 х

xY1)L4;(1)

Т4 K4 L5 (Х5 @ Х6 ® Х7 @Х8 Y2) L5

15 K5-L6 (Х6 © Х7 @ Х8 Y2) L6;

T6 K6-L7 (Х7 ®X8 Y2) L7;

Т7 GO X8,

де Тд - предсказанная четность сдвинутой информации в зависимости от шага сдвига (п 0-7); Ki - четность сдвинутой информации (i 0-6); Xj - информационные разряды (j

0-7);

KB - контрольный разряд по четности входной информации (Х8 « ХОФ XI Ф ,..., ФХ7),

Y1 и Y2 управляющие сигналы Сдвиг влево и Сдвиг вправо соответственно из дешифратора з;

Lm - управляющие сигналы, определяющие шаг сдвига (т 1-7); (±) сложение по модулю два; GO - шаг сдвига, равный нулю,

из дешифратора 4. Шифратор 24 (фиг.З) предназначен для формирования контрольного разряда вьгходной информации в соответствии с выражением

i 8 0 ffl jiM +® 7, (2)

где .8 - контрольный разряд;

/ i - информационные разряды выходной информации (i 0,1... 7).

Кроме того, шифратор 24 предназначен для контроля выходной информации по четности и формирования сигнала ошибки Е1 в соответствии с выражением

Е1 @ В7 © С7,

(ТО + Т1 +,..., Т7)

(3)

о

0

5

5

0

5

где В7 - четность информации, вдвигаемой слева в устройствоJ С7 - четность информации, вдвигаемой справа в устройство, а также для формирования сигнала общей ошибки ЕС в соответствии с выражением

ЕО Е1 -f Е2 + ЕЗ + Е4 + E5,i (4) где Е2 - сигнгш ошибки вдвигаемой

слева информации в устрой- ство

ЕЗ - сигнал ошибки сдвигаемой информации ,

Е4 - сигнал ошибки сдвинутой информации;Е5 - сигнгш ошибки вдвигаемой

справа информации в устройство.

Коммутатор 19 (фиг.4) предназначен для передачи четности вьщвигаемых разрядов по выходу 41 устройства и приема четности вдвигаемых разрядов по входу 42 устройства.

Коммутатор 20 (фиг.1) аналогичен описанному коммутатору 19.

Блок 26 формирования четности выдвигаемой информации (фиг.5) предназначен для формирования четности Z 7 выдвигаемой информации в соответствии с вьфажением:

Z7 ZO © Z1 ф, ,.., © Z6, (5)

71325481

где Zi - разряды выдвигаемой инфорна- ции из блока коммутаторов i (0-6).

Второй блок 27 формирования четности выдвигаемой информации (фиг.1) аналогичен описанному первому блоку 26 формирования четности выдвигаемой информации.

8

По входу 37 задания режима работы устройства поступает информация о режиме работы, которая приходит в виде 2-разрядного слова. Соответственно этому возможны четыре режима работы: 00 - одиночной работы, 01 - групповой работы в качестве головного устройства, 10 - групповой работы в качест- Блок 22 контроля вдвигаемой инфор- ю оконечного устройства, 11 - груп- мации (фиг.6) предназначен для конт- повой работы в качестве среднего уст- роля по четности принимаемой информа- 1ройства. ции слева и формирования сигнала ошибки Е2 в соответствии с выражением

По входу 39 устройства поступает информация о типе сдвига, которая 15 приходит в В1ще 3-разрядного слова. Соответственно этому возможны восемь типов сдвига, из которых используются шесть: 000 - циклический сдвиг вправо; 001 - циклический сдвиг влево .

В1

В7,

(6)

Е2 ВО

где ВО, В1, ... В6 - информационные разряды, вдвигаемые слева в устройство;

В7 - четность вдвигаемой слева ин-20 010 - арифметический сдвиг вправо формации.011 - арифметический сдвиг влево

По входу 39 устройства поступае информация о типе сдвига, которая 15 приходит в В1ще 3-разрядного слова Соответственно этому возможны восе типов сдвига, из которых использую шесть: 000 - циклический сдвиг впр во; 001 - циклический сдвиг влево .

Блок 23 контроля вдвигаемой информации (фиг.1) аналогичен описанному первому блоку 22 контроля вдвигаемой информации.

Блок 25 контроля сдвигаемой информации (фиг.7) предназначен для контроля по четности сдвигаемой информации и формирования сигнала ошибки ЕЗ в соответствии с выражением

ЕЗ ХО @ Х1 +, ..., g)X8. (7) Блок 21 контроля сдвинутой информации (фиг.8) предназначен для контроля по четности сдвинутой информации и формирования сигнала ошибки Е4 в соответствии с выражением Е4 RO © R1 @, ... ,®R7 (J) ТО @ Т1 Ф, ...,@Т7,(8)

30

100 - логический сдвиг вправо; 101 логический сдвиг влево.

По входам 52 и 53 устройства по 25 тупают соответственно шаг сдвига и расширенный шаг сдвига (последний в случае групповой работы). Замети что общий код по входам 52 и 53 ра общему шагу сдвига устройства.

На входы 28 устройства поступае сдвигаемая информация.

Устройство запускается в работу импульсным сигналом начала операци который поступает по входу 36 устр ства.

Выполнение непосредственно опер ций сдвига в устройстве происходит аналогично выполнению этих операци в известном устройстве. Поэтому ра

35

где RO-R7 - разряды сдвинутой инфор- 40 смотрим работу устройства с точки мации из узла 1 коммута- зрения обнаружения ошибок, ции.В режиме одиночной работы (по вхоМультиплексор 17 (фиг.9) предназна- ду 37 задания режима работы устрой- чен для формирования управляющих ства поступает код 00) первый выход сигналов, определяющих шаг сдвига для в четности выдвигаемых разрядов устпредсказания четности сдвинутой информации в соответствии с выражением L1 G1 32 + G7 11; L2 G2 12 + G6 11; G3 12 + G5 11; G4 Т2 + G4 11; G5 12 + G3 11; G6 12 + G2 11;

L3 L4 L5 L6 L7

50

(9)

ройства соединяется с вторым входом 50 четности вдвигаемых разрядов устройства, второй выход 51 четности выдвигаемых разрядов устройства соединяется с первым входом 42 четности вдвигаемых разрядов устройства. Сдви гаемая информация и ее контрольный раз.ряд по четности, поступающие по входам 28 и входу 56 устройства, проG7 12 + G1 11,

где Gi - величина шага сдвига, форми- gg ходят через мультиплексор 9 и запи- руемая вторым дешифратором 4. сываются в регистр 8 и в блок 12 за- Устройство работает следующим образом (для определенности примем, что разрядность устройства К 8).

писи контрольного разряда соответственно. Правильность записи контролируется блоком 25 контроля сдвигаемой

8

По входу 37 задания режима работы устройства поступает информация о режиме работы, которая приходит в виде 2-разрядного слова. Соответственно этому возможны четыре режима работы: 00 - одиночной работы, 01 - групповой работы в качестве головного устройства, 10 - групповой работы в качест- ю оконечного устройства, 11 - груп- повой работы в качестве среднего уст- 1ройства.

По входу 39 устройства поступает информация о типе сдвига, которая 15 приходит в В1ще 3-разрядного слова. Соответственно этому возможны восемь типов сдвига, из которых используются шесть: 000 - циклический сдвиг вправо; 001 - циклический сдвиг влево .

100 - логический сдвиг вправо; 101 логический сдвиг влево.

По входам 52 и 53 устройства пос- тупают соответственно шаг сдвига и расширенный шаг сдвига (последний - в случае групповой работы). Заметим, что общий код по входам 52 и 53 равен общему шагу сдвига устройства.

На входы 28 устройства поступает сдвигаемая информация.

Устройство запускается в работу импульсным сигналом начала операции, который поступает по входу 36 устройства.

Выполнение непосредственно операций сдвига в устройстве происходит аналогично выполнению этих операций в известном устройстве. Поэтому рас

50

ройства соединяется с вторым входом 50 четности вдвигаемых разрядов устройства, второй выход 51 четности выдвигаемых разрядов устройства соединяется с первым входом 42 четности вдвигаемых разрядов устройства. Сдвигаемая информация и ее контрольный раз.ряд по четности, поступающие по входам 28 и входу 56 устройства, проходят через мультиплексор 9 и запи- сываются в регистр 8 и в блок 12 за-

писи контрольного разряда соответственно. Правильность записи контролируется блоком 25 контроля сдвигаемой

91325А81

в соответствии с вьфажену5 0 ги

кием (7), Далее информация поступает в узел 1, где осуществляется непосредственно сдвиг. Парахшельно с узлом 1 работает шифратор 18, который на основании поступающей на его входы сдвигаемой информации (сигналы ХО-Х7) и ее контрольного разряда (сигналХ8), информации о направлении сдвига (сигналы: от регистра 8 ХО-Х7, значения которых равны соответственно 10101101, от блока 12 записи контрольного разряда Х8 1, от первого

налы У1 и У2 от дешифратора 3), о ша- О контроля сдвигаемой информации. При ге сдвига (сигнал GO от дешифратора правильном приеме информации блок 25 4 и сигналы L1-L7 от мультиплексора контроля сдвигаемой информации выра- 17), о типе сдв,ига (сигнал от блока батывает сигнал ЕЗ О (в противном 16 коррекции четности) вырабатывает случае ЕЗ 1). В блок 18 предсказа- в соответствии с выражениями (1) чет- 5 ния четности поступают следующие сиг- ность сдвинутой информации (один из сигналов ТО-Т7), которая вместе с сдвинутой в блоке коммутаторов информации (сигналы RO-R7) поступает в блок 21 контроля сдвинутой информации,20 дешифратора 3 У1 , У2 О, от блока 16 работающего в соответствии с вьфаже- коррекции четности О, от второго де- нием (8).шифратора 4 G10 О, от мультиплексоВьщвигаемая информация, например ра 17 1-7, равные соответственно при сдвиге влево (разряды ZO-Z6) пос- 0010000.

тупает, кроме коммутатора 5, еще и На сумматорах 68-74 (фиг.2) сфор- в блок 26 формирования четности вьщви- мируются сигналы КО-Кб 0011011, а гаемой информации, формирующий в соответствии с выражением (5) контрольный разряд Z7 вьщвигаемой информации, которьй через коммутатор 19 поступает блока 21 контроля сдвинутой информа- на выход 41 четности вдвигаемых раз- ции поступают сдвинутая в узле 1 ин- рядов устройства. При сдвиге вправо формация RO-R7 01101000 и предска- аналогично работают блок 27 формирова- занная в шифратор 18 ее четность. При ния четности вьщвигаемых разрядов правильном сдвиге информации в узле

35 блок 21 контроля сдвинутой информации вырабатывает сигнал Е4 О (в противном cjiy4ae Е4 1). Три выдвигаемых разряда (101) с узла 1 поступают в первый блок 26 формирования четности информации, в который поступает также 0 выдвигаемой информации, в коммутатор из коммутатора 19 (с входа 42 устрой- 5 и далее через коммутатор 6 в муль- ства) четность вдвигаемых разрядов (сигнал В7). Блок 22 работает в соответствии с выражением (6) и контролирует прием вдвигаемых слева разрядов. 45 формации формируется сигнал Z7 1, При сдвиге влево аналогично работает который через коммутаторы 19 и 20 пена выходах шифратора 18 - сигнал ТО-Т7 00100000, т.е. четность сдвинутой информации (Т2 1). На входы

и коммутатор 20.

Вдвигаемая информация, например при сдвиге вправо (разряды ВО-В6), поступает, кроме мультиплексора 7, еще и в блок 22 контроля вдвигаемой

типлексор 7 и блок 23 контроля вдвигаемой информации. На выходе блока 26 формирования четности выдвигаемой инблок 23 контроля вдвигаемых (справа) разрядов. I

Шифратор 24 контролирует выходную (из мультиплексора 7) информацию в соответствии с вьфажением (3), формирует контрольный разряд выходной информации и вырабатывает сигнал Ошибредается в блок 23 контроля вдвигаемой информации и шифратор 24. Если передача и прием вьщвигаемых разрядов 50 происходят верно, блок 23 контроля вдвигаемой информации формирует сигнал Е5 О (в противном случае ЕЗ 1).

Таким образом, на выходе мультика в соответствии с выражениями (2) плексора 7 формируется сдвинутая цик- и (4) соответственно, поступающие на лически на три разряда влево информация 01101101, которая подается на информационные выходы 29 устройства и

выход 55 контрольного разряда и выход 44 сигнала ошибки устройства соответственно.

на информационные входы шифратора 24,

10

Пример. Пусть необходимо сдвинуть циклически влево на три разряда (на вход 39 устройства поступает код 001, а на вход 52 устройства - код 011) следующую информацию: 1010 1101. Сдвигаемая информация (ХО-Х7 10101101) и ее контрольный разряд (Х8-1) через мультиплексор 9 и регистр 8 поступают в узел 1 и блок 25

налы: от регистра 8 ХО-Х7, значения которых равны соответственно 10101101, от блока 12 записи контрольного разряда Х8 1, от первого

контроля сдвигаемой информации. При правильном приеме информации блок 25 контроля сдвигаемой информации выра- батывает сигнал ЕЗ О (в противном случае ЕЗ 1). В блок 18 предсказа- ния четности поступают следующие сиг дешифратора 3 У1 , У2 О, от блока 1 коррекции четности О, от второго де- шифратора 4 G10 О, от мультиплексо

На сумматорах 68-74 (фиг.2) сфор- мируются сигналы КО-Кб 0011011, а блока 21 контроля сдвинутой информа- ции поступают сдвинутая в узле 1 ин- формация RO-R7 01101000 и предска- занная в шифратор 18 ее четность. При правильном сдвиге информации в узле

на выходах шифратора 18 - сигнал ТО-Т7 00100000, т.е. четность сдвинутой информации (Т2 1). На входы

блок 21 контроля сдвинутой информации вырабатывает сигнал Е4 О (в противном cjiy4ae Е4 1). Три выдвигаемых разряда (101) с узла 1 поступают в первый блок 26 формирования четности выдвигаемой информации, в коммутатор 5 и далее через коммутатор 6 в муль- формации формируется сигнал Z7 1, который через коммутаторы 19 и 20 петиплексор 7 и блок 23 контроля вдвигаемой информации. На выходе блока 26 формирования четности выдвигаемой инредается в блок 23 контроля вдвигаемой информации и шифратор 24. Если передача и прием вьщвигаемых разрядов происходят верно, блок 23 контроля вдвигаемой информации формирует сигнал Е5 О (в противном случае ЕЗ 1).

Таким образом, на выходе мультина информационные входы шифратора 24,

на управлякмцие входы которого подается следующая информация: с выхода шифратора 18 ТО-Т7 00100000, с выхода коммутатора 19 В7 0, с выхода коммутатора 20 С7 1, с выхода блока 21 контроля сдвинутой информации Е4 О, с выхода блока 22 контроля сдвигаемой информации Е2 О, с вьпсода блока 23 контроля вдвигаемой информа- ции Е5 О, с выхода блока 25 контроля сдвигаемой информации ЕЗ О (при этом предполагается, что ошибок при работе устройства нет). Сумматор 82 (рис. 3) по модулю два сформирует контрольный разряд (равный единице) выходной информации. Сумматор 83 (фиг.З) при правильной работе мультиплексора 7 вырабатьгаает сигнал Е1 О (в противном случае Е1 1). Все сигналы об ошибках в устройстве (Е1, Е2, ЕЗ, Е4 и Е5) собираются в шифраторе 24 по ИЛИ и вырабатывается общий сигнал ЕО об ошибке в устройстве.

При выполнении логического сдвига (на вход 39 устройства поступают кода 100 или 101) контроль работы устройства отличается от контроля при выполнении циклического сдвига тем, что коммутаторы, принимакнцие вдвига- емые разряды и их контрольный разряд, блокированы. При выполнении арифметического сдвига вправо (на вход 39 устройства поступает код 010) блок 16 в случае, если знаковый разряд равен единице и шаг сдвига нечетный, вырабатывает сигнал, равный единице, который скорректирует выходные сигналы ТО-Тб шифратора 24. В этом случае блок 16 коррекции четности формирует четность вдвигаемых разрядов (при ари4метиче.ском сдвиге вправо, как известно, освободившиеся при сдвиге разряды заполняются знаковым разрядом) .

В режиме групповой работы (при разрядности сдвигаемой информации К 8) контроль работы каждого устройства осуществляется аналогично, как и при одиночной работе, с той разницей, что выходы 41 и 51 каждого устройства соединены с входами 50 и 42 соседних левого и правого устройств соответственно, а входы 42 и 50 каждого устройства соединены с выходами 51 и 41 соседних левого и правого устройств соответственно.

Помимо общего сигнала ЕО ошибки (выход 44 устройства), сигналы ошибок

s 0

5 О g 0 5

о

5

Е1-Е5 также имеют выводы на контакт, т.е. являются выходами 45, 43, 48, 46 и 49 устройства. Это позволяет с достаточной степенью точности локализовать ошибку в устройстве, что может оказаться полезным при проверке на годность данного устройства, выполненного в виде БИС.

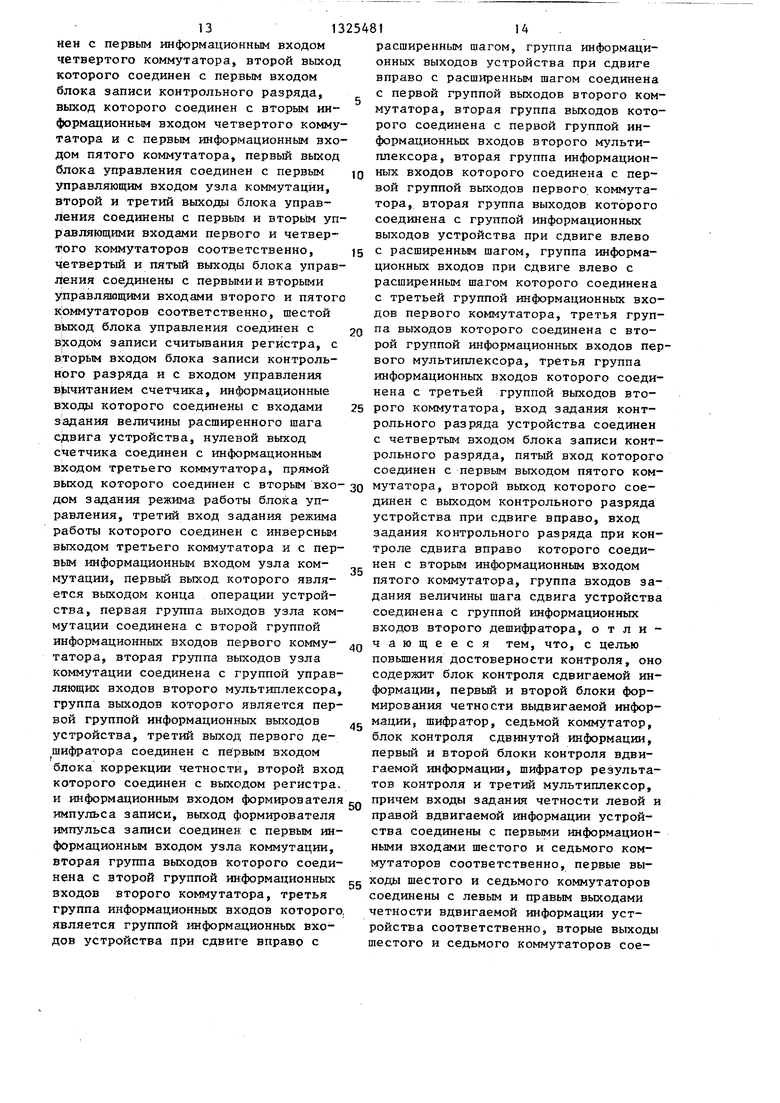

Выходные сигналы дешифратора 3 показаны одной группой выходов (шиной) для упрощения фиг.1. Для более точного определения разводки выходов дешифратора 3 приводятся табл. 1 и 2, где N0 - N2 - разряды входа 39 типа сдвига устройства, SO-S5 - -выходные сигналы дешифратора 3.

Формула изобретения

Устройство для сдвига информации с контролем, содержащее блок управления, два дешифратора, узел коммутации, регистр, шесть коммутаторов, два мультиплексора, счетчик, формирователь импульса записи, блок коррекции четности, блок записи контрольного разряда, причем группа информационных входов устройства соединена с первой группой информационных входов первого мультиплексора, выходы которого соединены с информационными входами регистра, группа выходов которого сбе- динена с группой :информационных входов узла коммутации, с первыми группами информационных входов первого и второго коммутаторов, вход пуска устройства соединен с входом пуска блока управления, регистра и блока записи контрольного разряда, вход задания режима работы устройства соединен с первым входом задания режима работы блока управления, вход синхронизации которого соединен с входом синхронизации устройства и с входом синхронизации третьего коммутатора, группа входов задания типа сдвига устройства соединена с группой информационных входов первого дешифратора, группа выходов которого соединена с группой входов логических условий блока управления, первый выход первого дешифратора соединен с входом разрешения формирователя импульса записи, первый выход четвертого коммутатора соединен с выходом контрольного разряда устройства при сдвиге влево, вход задания признака контрольного разряда при контроле сдвига влево которого соединен с первым информационным входом четвертого коммутатора, второй выход которого соединен с первым входом блока записи контрольного разряда, вьпсод которого соединен с вторым информационным входом четвертого коммутатора и с первым информационным входом пятого коммутатора, первый выход блока управления соединен с первым управляющим входом узла коммутации, второй и третий выходы блока управ- Л|ення соединены с первым и вторьЫ управляющими входами первого и четвертого коммутаторов соответственно, четвертый и пятый выходы блока управления сое/5инены с первыми и вторыми управляющими входами второго и пятого коммутаторов соответственно, шестой в1з1ход блока управления соединен с выходом записи считьгаания регистра, с вторым входом блока записи контрольного разряда и с входом управления в|ычитанием счетчика, информационные входы которого соединены с входами задания величины расширенного шага с цвига устройства, нулевой выход счетчика соединен с информационным входом третьего коммутатора, прямой вькод которого соединен с вторым входом задания режима работы блока управления, третий вход задания режима работь которого соединен с инверсным выходом третьего коммутатора и с первым информационным входом узла коммутации, первьй выход которого является выходом конца операции устройства, первая группа выходов узла коммутации соединена с второй группой информационньш входов первого коммутатора, вторая группа вькодов узла коммутации соединена с группой управляющих входов второго мультиплексора, группа выходов которого является первой группой информационных выходов устройства, третий выход первого дешифратора соединен с первым входом блока коррекции четности, второй вход которого соединен с выходом регистра и информационным входом формирователя импульса записи, выход формирователя импульса записи соединен с первым ин- формационньм входом узла коммутации, вторая группа выходов которого соединена с второй группой информационных входов второго коммутатора, третья группа информационных входов которого является группой информационных входов устройства при сдвиге вправо с

0

5

0

5

0

5

0

5

0

5

расширенным шагом, группа информационных выходов устройства при сдвиге вправо с расширенным шагом соединена с первой группой выходов второго коммутатора, вторая группа выходов которого соединена с первой группой информационных входов второго мультиплексора, вторая группа информационных входов которого соединена с первой группой выходов первого коммутатора, вторая группа выходов которого соединена с группой информатдионных выходов устройства при сдвиге влево с расширенным шагом, группа информационных входов при сдвиге влево с расширенньм шагом которого соединена с третьей группой информационных входов первого коммутатора, третья группа выходов которого соединена с второй группой информационных входов первого мультиплексора, третья группа информационных входов которого соединена с третьей группой выходов второго коммутатора, вход задания контрольного разряда устройства соединен с четвертым входом блока записи контрольного разряда, пятый вход которого соединен с первым выходом пятого коммутатора, второй выход которого соединен с выходом контрольного разряда устройства при сдвиге вправо, вход задания контрольного разряда при контроле сдвига вправо которого соединен с вторым информационным входом пятого коммутатора, группа входов задания величины шага сдвига устройства соединена с группой информационных входов второго дешифратора, отличающееся тем, что, с целью повьшения достоверности контроля, оно содержит блок контроля сдвигаемой информации, первый и второй блоки формирования четности выдвигаемой информации, шифратор, седьмой коммутатор, блок контроля сдвинутой информации, первьй и второй блоки контроля вдвигаемой информации, шифратор результатов контроля и третий мультиплексор, причем входы зад,ания четности левой и правой вдвигаемой информации устройства соединены с первыми информационными входами шестого и седьмого коммутаторов соответственно, первые выходы шестого и седьмого коммутаторов соединены с левым и правым выходами четности вдвигаемой информации устройства соответственно, вторые выходы шестого и седьмого коммутаторов сое151325А81

динены с входами первого и второго блоков контроля четности вдвигаемой информации соответственно и с первым и вторым информационньми входами шифратора результатов контроля соответственно, первая и вторая группы выходов узла коммутации соединены с групзультатов контроля соединена с группой выходов второго мультиплексора, группа выходов регистра соединена с группой информационных входов шифратора и с группой входов блока контроля сдвинутой информации, вход которого соединен с выходом блока записи контрольного разряда и с информаципами входов первого и второго блоков

формирования четности выдвигаемой ин-юонным входом шифратора, выход блока

формации, выходы которых соединены сконтроля сдвинутой информации соедивторыми информационными входами шее-нен с выходом ошибки сдвинутой инфортого и седьмого коммутаторов соответ-мации устройства и с пятым информациственно, первый и второй управляющиеонным входом шифратора результатов

входы шестого и седьмого коммутаторов isконтроля, шестой информационный вход

соединены с вторым, третьим, четвер- Tbw к пятым выходами блока управления соответственно, группы входов первого и второго блоков контроля четности вдвигаемой информации соединены с 20 первой группой выходов первого коммутатора и второй группой выходов второго к 1мутатора соответственно, выходы первого и второго блоков контроля четности вдвигаемой информации яв- 25 и с первым информационным входом треляются левым и правым выходами контроля устройства, соединены с третьим и четвертым информационными входами ши(|1 атора результатов контроля, первый, второй и третий выходы которого соединены с выходами общей ошибки устройства, ошибки по четности устройства и ошибки по четности сдвигаемой информации устройства соответственно, группа входов шифратора ре- нен свькодом третьего мультиплексора.

IOD

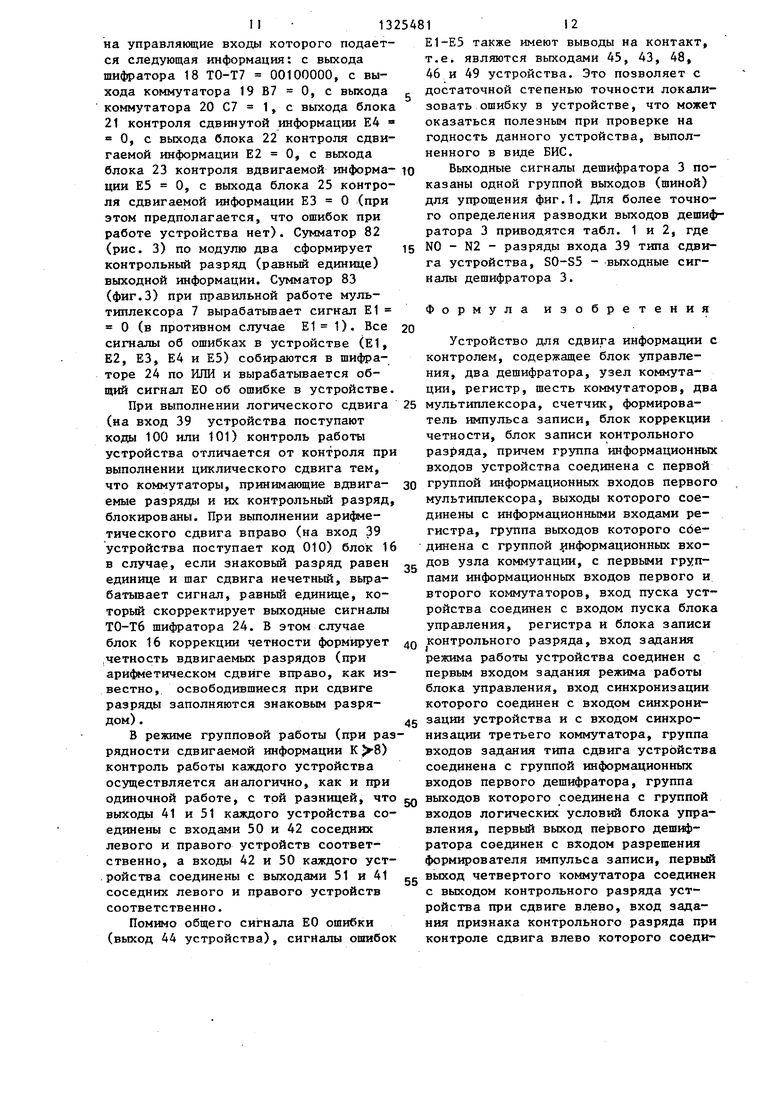

Таблица 1 N0 N1 N2 SO S1 S2 S3 S4 85 Тип операции

О О

О 1

О 1

О О

О 1

О О

16

зультатов контроля соединена с группой выходов второго мультиплексора, группа выходов регистра соединена с группой информационных входов шифратора и с группой входов блока контроля сдвинутой информации, вход которого соединен с выходом блока записи контрольного разряда и с информацикоторого соединен с выходом шифратора и входом блока контроля четности сдвигаемой информации, выход которого соединен с выходом признака ошибки четности сдвигаемой информации и с седьмым информационньм входом шифратора результатов контроля, второй информационный вход шифратора соединен с третьим выходом первого дешифратора

тьего мультиплексора, управляющий вход которого соединен с выходом второго дешифратора, с третьим инфор- мациоиньм входом узла коммутации и с третьим информационным входом шифратора, с третьим входом блока коррекции четности, выход которого соединен с четвертым информационным входом шифратора, пятый вход которого соеди

О Циклический сдвиг вправо

О Циклический сдвиг влево

О Арифметический сдвиг вправо

О Арифметический сдвиг влево

О Логический сдвиг вправо

О

1 Логический сдвиг влево

Блок-приемник

2 10

16 17 18

3f

3 rtVS57

46 19

Таблица2

Выходной сигнал(ы) дешифратора 3 (источник)

S2, S3, S1, S5

SO, SI,, S2, S3, S4, S5 S2

Y1 S1 V S3v S5 Y2 SOv S2 vS4 Y1 Siv S3 VS5 Y2 SOVS2VS4

.56

5tf

31 33

52 0

ff

0 Sff

ffd

Т50От Улока 8

g/n блока 12

77;

Qm локаЪ

щ OmfAOxaie

ffm fflona /7

flflly От Улока

ТО

Фиг,2

KSAOKt/21 8J

Фиг. 5

Фиг.6

Фиг.7

Фиг.8

Фиг,9

38

оi

т

о о

От 8

Редактор Н.Гунько

Составитель А.Сиротская Техред Л.Сердюкова

Заказ 3111/45Тираж 672Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическЬе предприятие, г. Ужгород, ул. Проектная, 4

W к Улокаи 6iJV2

к|

J6S

№7

Фиг.П

Корректор А.Тяско

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для предсказания четности результата сдвигателя | 1988 |

|

SU1580368A1 |

| Устройство для сдвига информации | 1983 |

|

SU1188783A2 |

| Устройство для предсказания четности результата сдвигателя | 1988 |

|

SU1649545A1 |

| Устройство для предсказания четности результата сдвигателя | 1989 |

|

SU1658155A1 |

| Устройство для формирования сигналов четности при сдвигах двоичных кодов | 1989 |

|

SU1783527A1 |

| Устройство односторонних сдвигов двоичных кодов с контролем | 1987 |

|

SU1695306A1 |

| Устройство для предсказания четности результата сдвигателя | 1989 |

|

SU1730628A1 |

| Модуль для сдвига операндов | 1988 |

|

SU1617434A1 |

| Устройство для формирования сигналов четности | 1988 |

|

SU1571591A1 |

| Устройство для формирования сигнала четности при сдвигах двоичных кодов | 1987 |

|

SU1481770A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для полного контроля сдвига информации в вычислительных устройствах. Цель изобретения - повышение достоверности контроля. Устройство содержит семь коммутаторов, три мультиплексора, блок управления, два шифратора, вычитающий счетчик, дешифратор, четыре блока контроля сдвигаемой информации. Устройство контролирует все операции сдвига информации (циклического, логического и арифметического) путем контроля сдвига между секциями (в качестве которого выступает одно устройство) в режиме наращивания разрядности, а также контроля выходной информации. 11 ил., 2 табл. с

| Устройство для сдвига информации | 1981 |

|

SU1014031A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для сдвига информации | 1983 |

|

SU1188783A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-07-23—Публикация

1985-12-30—Подача