11297055

Изобретение относится к вычислительной технике и может быть использовано в высокопроизводительных системах обработки информации.

Цепью изобретения является сокращение аппаратурных затрат,

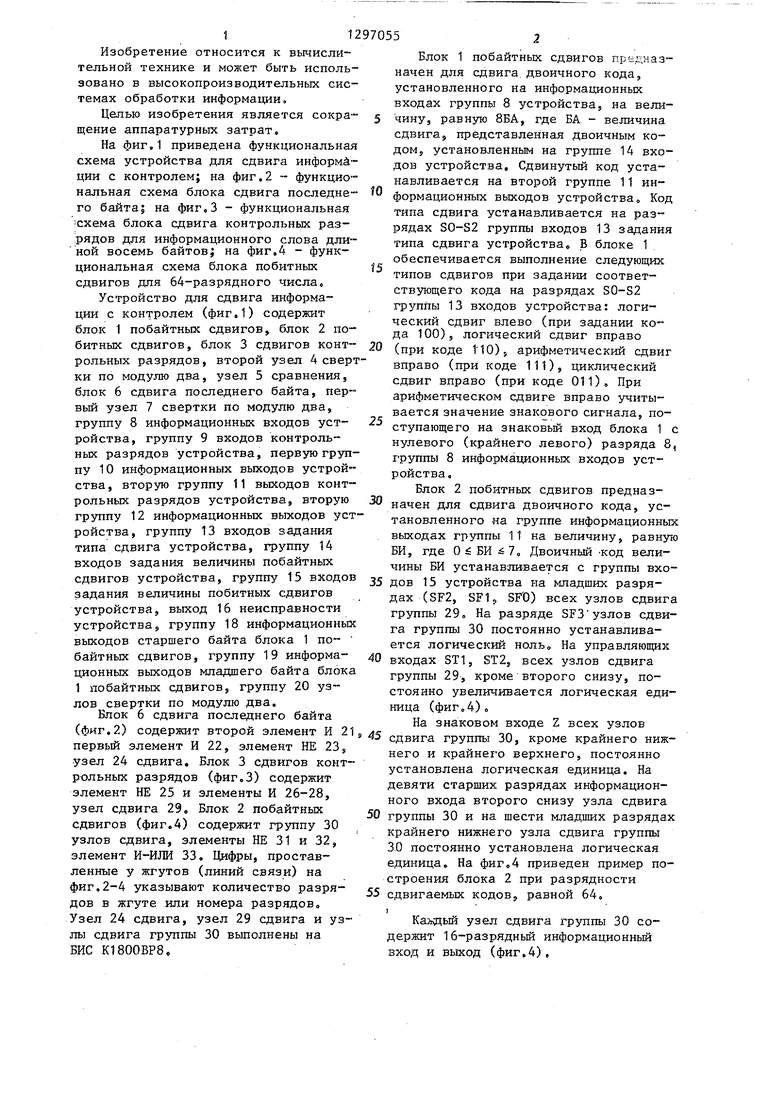

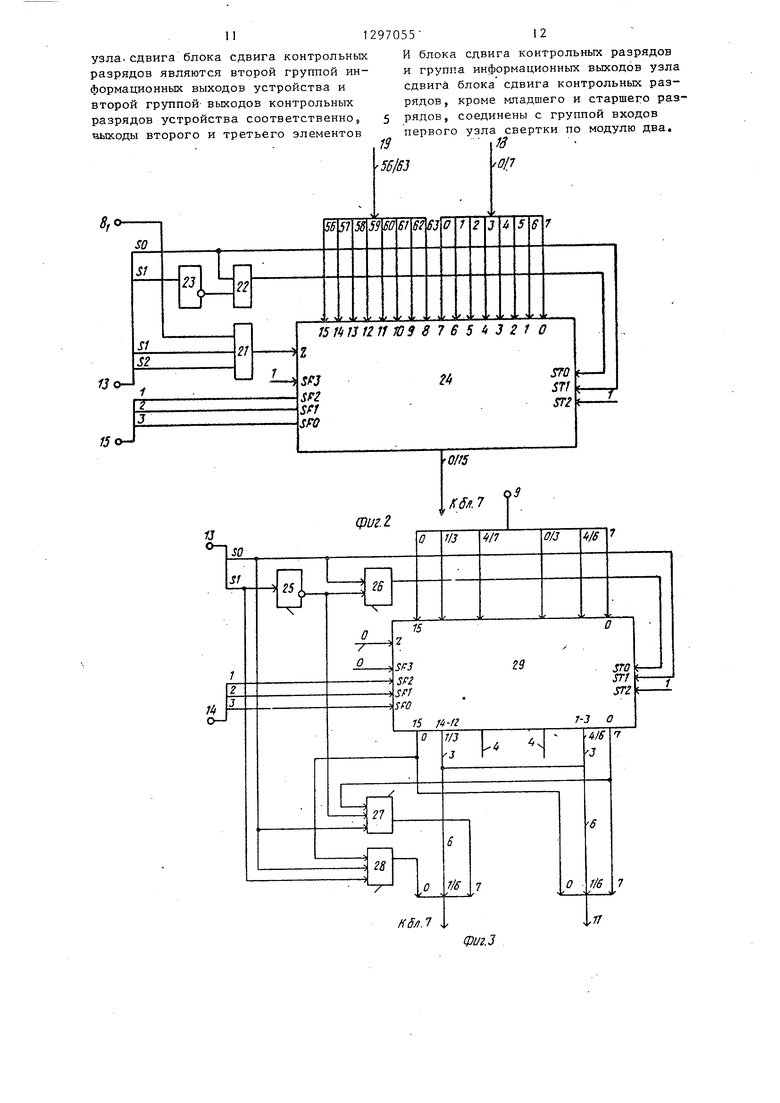

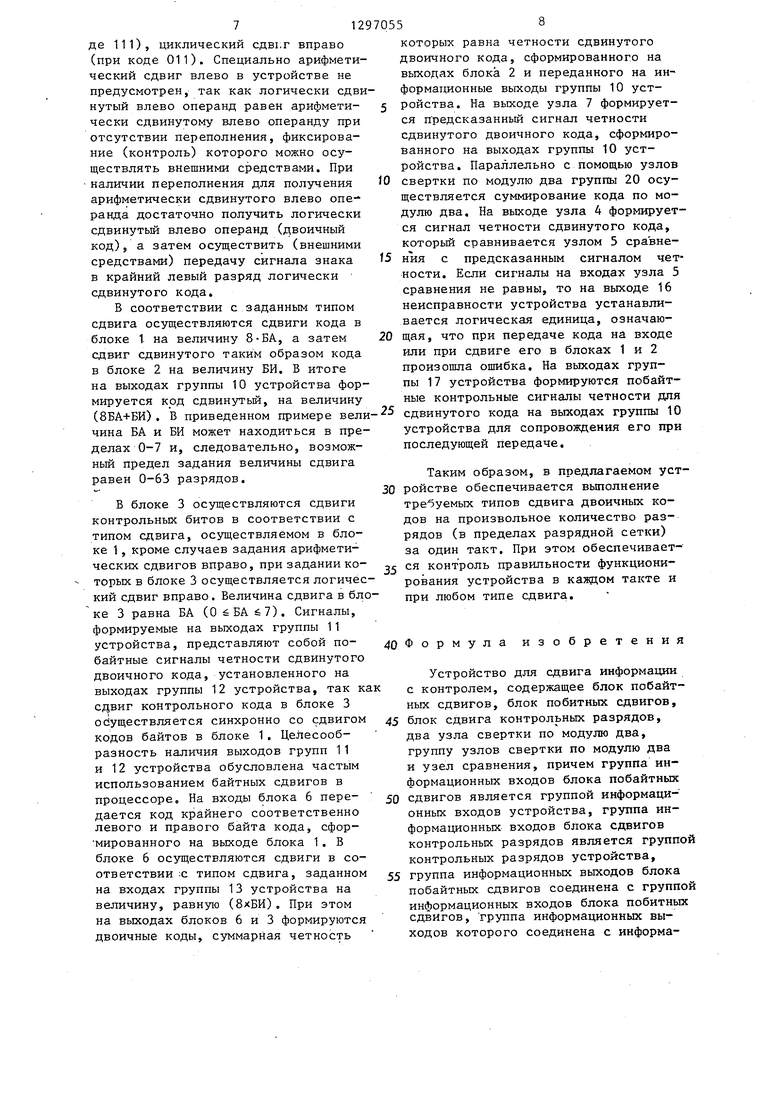

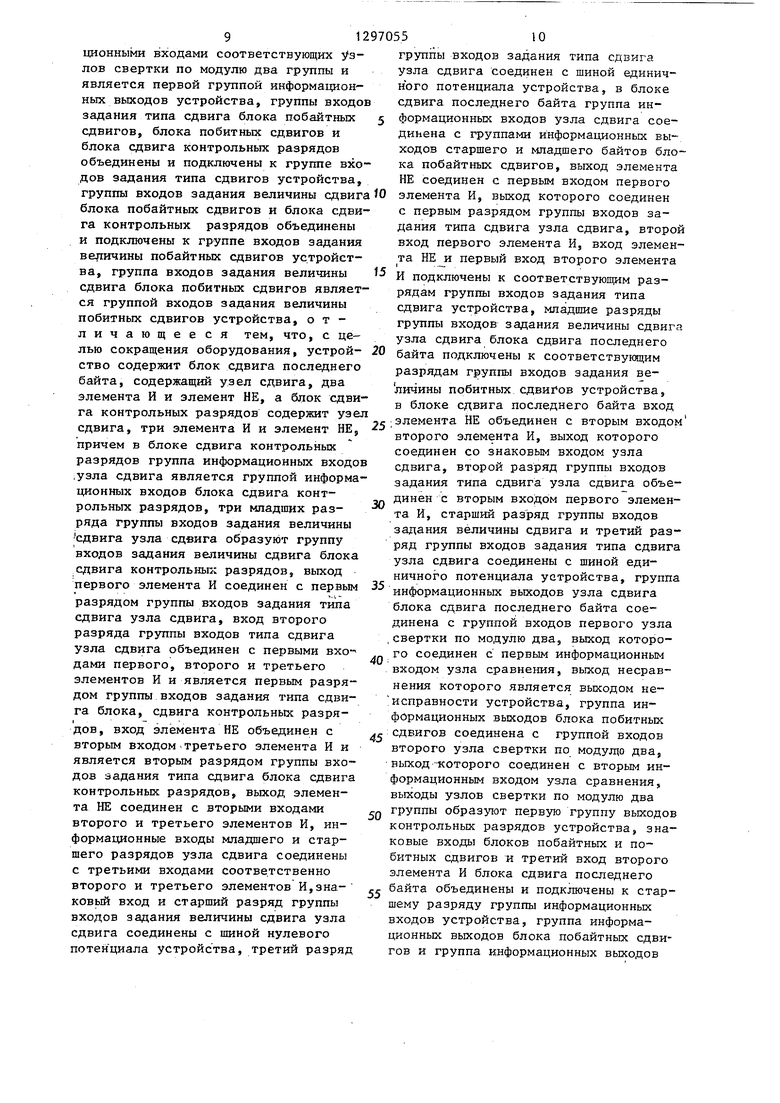

На фиг.1 приведена функциональная схема устройства для сдвига информй- ции с контролем; на фиг,2 - функциоБлок 1 побайтных сдвигов предназначен для сдвига двоичного кода, установленного на информационных входах группы 8 устройства, на вели- 5 чину, равную 8БА, где БА - величина сдвига, представленная двоичным кодом, установленным на группе 14 входов устройства. Сдвинутый код устанавливается на второй группе 11 иннапьная схема блока сдвига последне- tO формационных выходов устройства„ Код

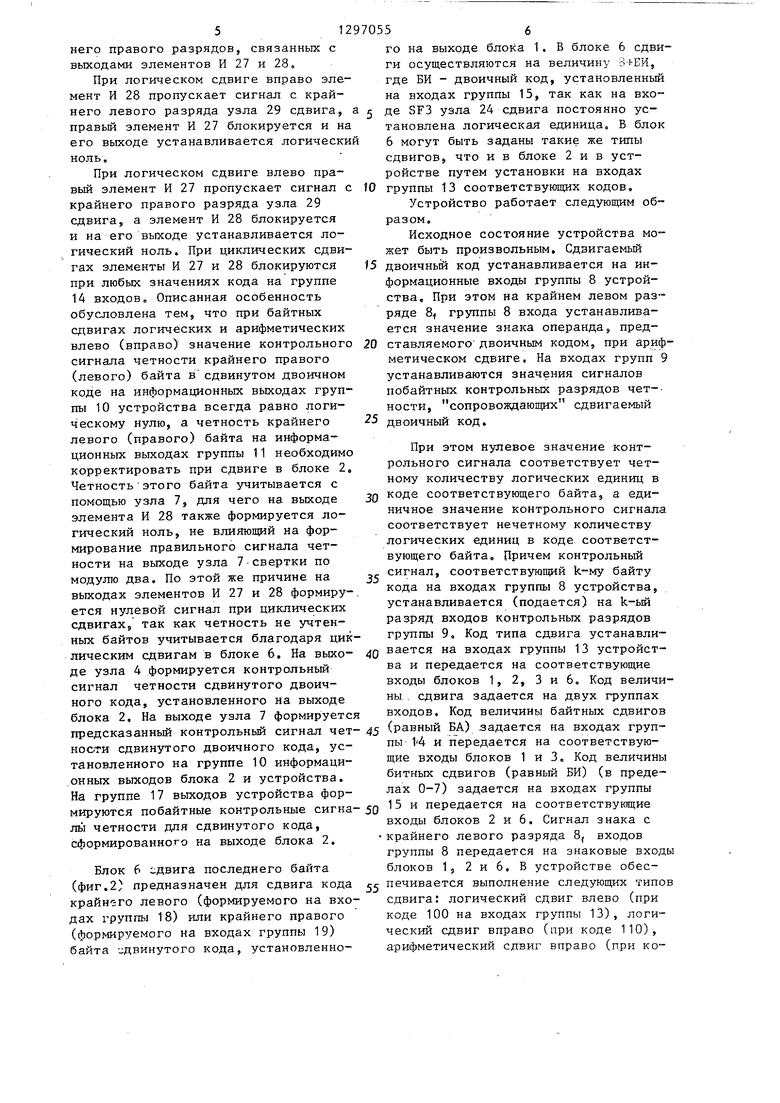

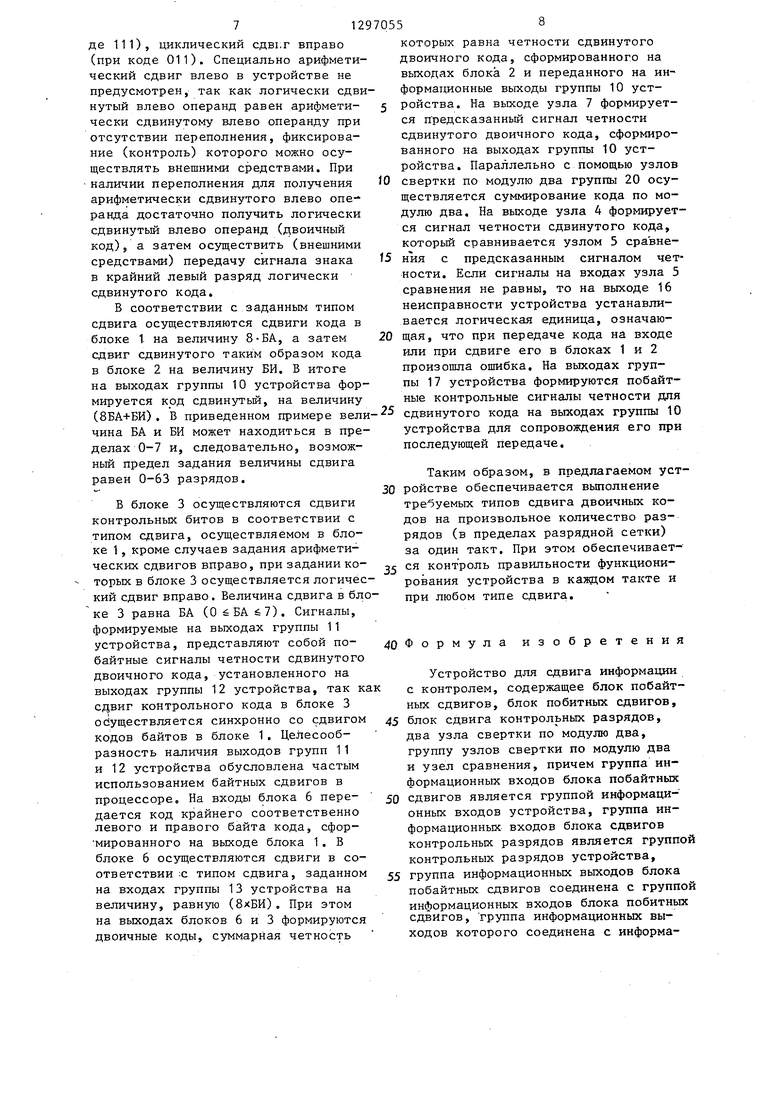

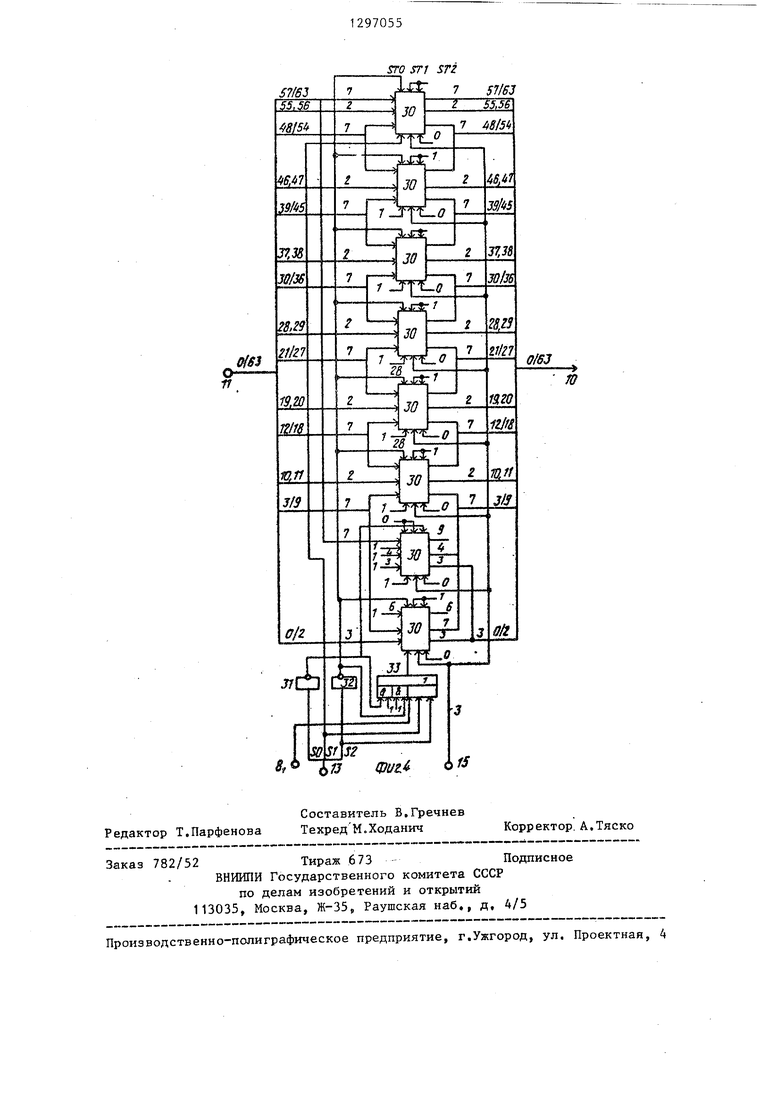

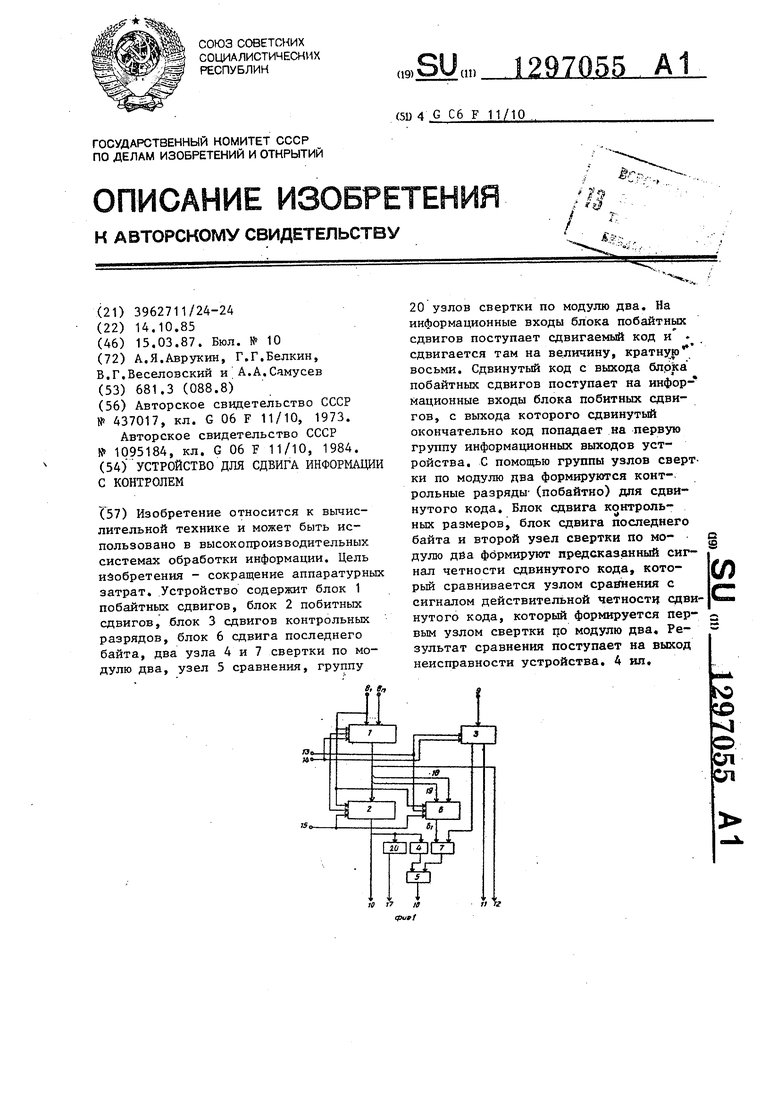

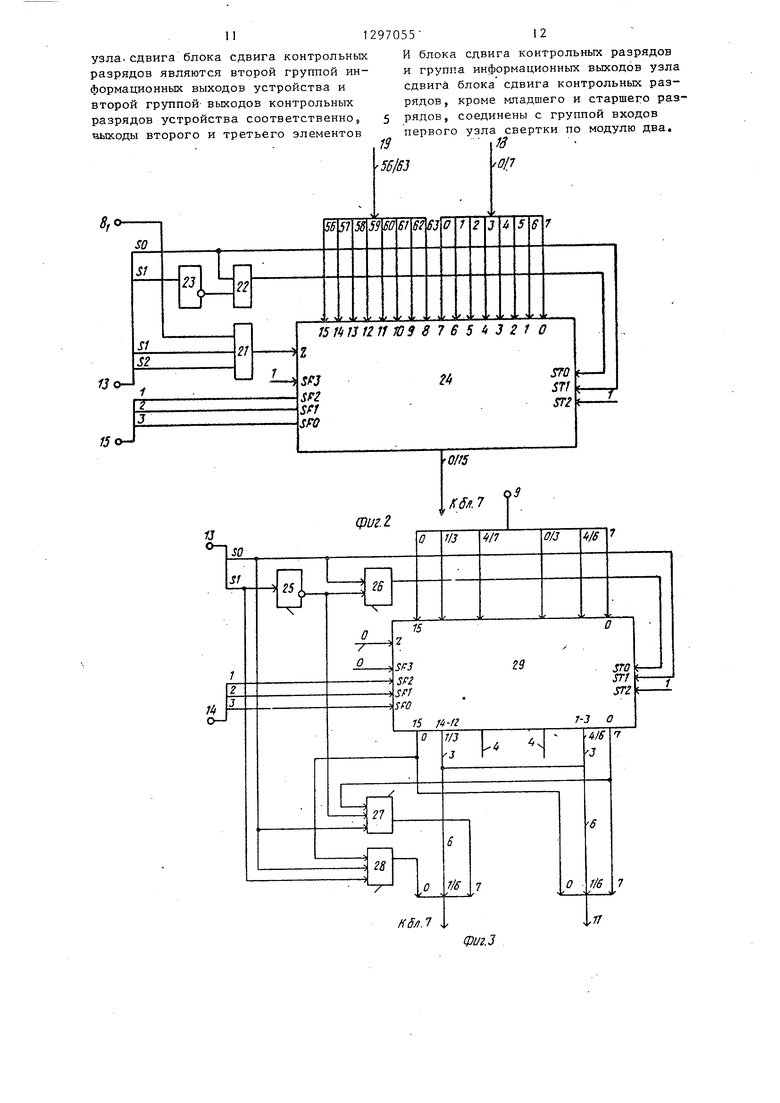

го байта; на фиг.З - функциональная схема блока сдвига контрольных разрядов для информационного слова длиной восемь байтов; на фиг.4 - функциональная схема блока побитных f5 сдвигов для 64-разрядного числа.

Устройство для сдвига информации с контролем (фиг,1) содержит блок 1 побайтных сдвигов, блок 2 побитных сдвигов, блок 3 сдвигов конт- 20 рольных разрядов, второй узел 4 свертки по модулю два, узел 5 сравнения, блок 6 сдвига последнего байта, первый узел 7 свертки по модулю два, группу 8 информационных входов уст- 25 ройства, группу 9 входов контрольных разрядов устройства, первую группу 10 информационных выходов устрой™ ства, вторую группу 11 выходов контрольных разрядов устройства, вторую 30 группу 12 информационных выходов устройства, группу 13 входов задания типа сдвига устройства, группу 14 входов задания величины побайтных

типа сдвига устанавливается на разрядах SO-S2 группы входов 13 задания типа сдвига устройства В блоке 1 обеспечивается выполнение следующих типов сдвигов при задании соответствующего кода на разрядах SO-S2 группы 13 входов устройства: логический сдвиг влево (при задании кода 100), логический сдвиг вправо (при коде 110)s арифметический сдвиг вправо (при коде 111), циклический сдвиг вправо (при коде 011). При арифметическом сдвиге вправо учитывается значение знакового сигнала, поступающего на знаковьй вход блока 1 с нулевого (крайнего левого) разряда 8 группы 8 информационных входов устройства.

Блок 2 побитных сдвигов предназначен для сдвига двоичного кода, установленного на группе информационных выходах группы 11 на величину, равную БИ, где 0 БИ 7, Двоичный Код величины БИ устанавливается с группы вхоБлок 2 побитных сдвигов предназначен для сдвига двоичного кода, установленного на группе информационных выходах группы 11 на величину, равную БИ, где 0 БИ 7, Двоичный Код величины БИ устанавливается с группы вхоустройства, группу 18 информационных выходов старшего байта блока 1 побайтных сдвигов, группу 19 информационных выходов младшего байта блока 1 побайтных сдвигов, группу 20 узлов свертки по модулю два.

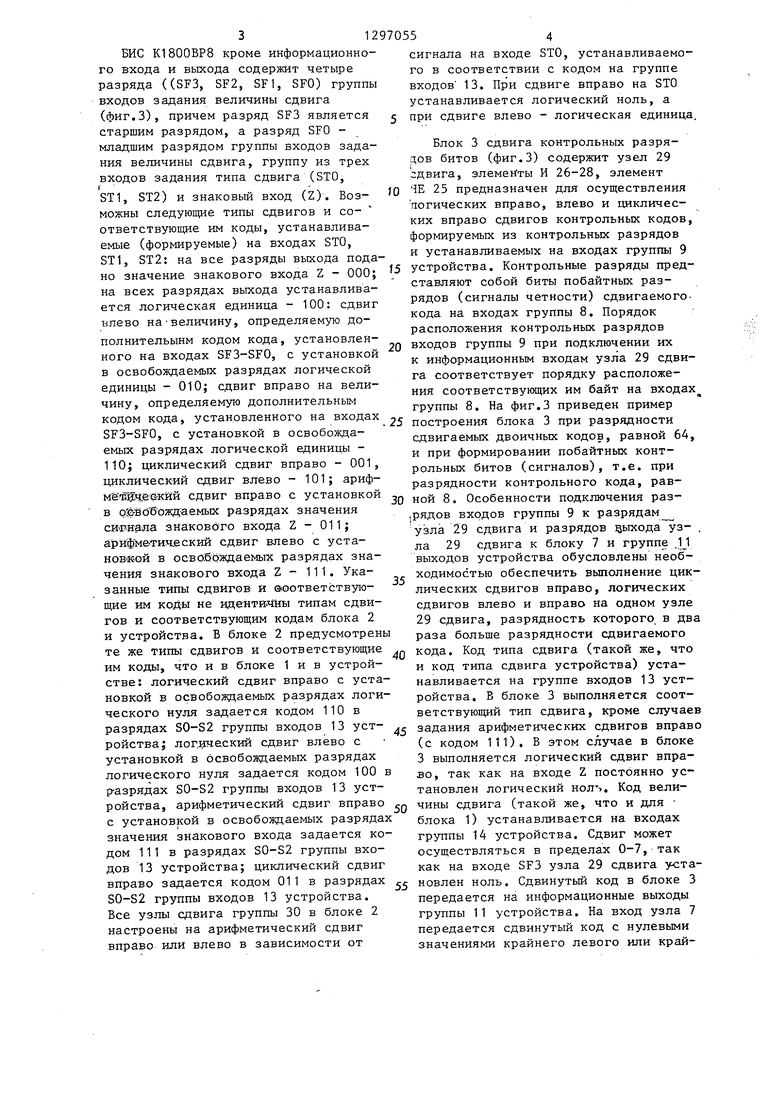

Блок 6 сдвига последнего байта

сдвигов устройства, группу 15 входов дов 15 устройства на младших разря- задания величины побитных сдвигов дах (SF2, SF1,, ЗГО) всех узлов сдвига устройства, выход 16 неисправности группы 29, На разряде SF3 узлов сдвига группы 30 постоянно устанавливается логический ноль. На управляющих 40 входах ST1, ST25 всех узлов сдвига группы 29-, кроме второго снизу, постоянно увеличивается логическая единица (фиг.4).

, .,,„На знаковом входе Z всех узлов

(фиг.2) содержит второй элемент И 21,5 сдвига группы 30, кроме крайнего ниж- первый элемент И 22, элемент НЕ 23, узел 24 сдвига. Блок 3 сдвигов контрольных разрядов (фиг.З) содержит элемент НЕ 25 и элементы И 26-28, узел сдвига 29, Блок 2 побайтных сдвигов (фиг.4) содержит группу 30 узлов сдвига, элементы НЕ 31 и 32, элемент И-ИЛИ 33. Цифры, проставленные у жгутов (линий связи) на

него и крайнего верхнего, постоянно установлена логическая единица. На девяти старших разрядах информационного входа второго снизу узла сдвига

50 группы 30 и на шести младших разрядах крайнего нижнего узла сдвига группы 30 постоянно установлена логическая единица. На фиг,4 приведен пример построения блока 2 при разрядности

фиг.2-4 указывают количество разрядов в жгуте или номера разрядов. Узел 24 сдвига, узел 29 сдвига и узлы сдвига группы 30 выполнены на БИС К1800ВР8.

Блок 1 побайтных сдвигов предназначен для сдвига двоичного кода, установленного на информационных входах группы 8 устройства, на вели- чину, равную 8БА, где БА - величина сдвига, представленная двоичным кодом, установленным на группе 14 входов устройства. Сдвинутый код устанавливается на второй группе 11 информационных выходов устройства„ Код

типа сдвига устанавливается на разрядах SO-S2 группы входов 13 задания типа сдвига устройства В блоке 1 обеспечивается выполнение следующих типов сдвигов при задании соответствующего кода на разрядах SO-S2 группы 13 входов устройства: логический сдвиг влево (при задании кода 100), логический сдвиг вправо (при коде 110)s арифметический сдвиг вправо (при коде 111), циклический сдвиг вправо (при коде 011). При арифметическом сдвиге вправо учитывается значение знакового сигнала, поступающего на знаковьй вход блока 1 с нулевого (крайнего левого) разряда 8, группы 8 информационных входов устройства.

Блок 2 побитных сдвигов предназначен для сдвига двоичного кода, установленного на группе информационных выходах группы 11 на величину, равную БИ, где 0 БИ 7, Двоичный Код величины БИ устанавливается с группы входов 15 устройства на младших разря- дах (SF2, SF1,, ЗГО) всех узлов сдвига группы 29, На разряде SF3 узлов сдвига группы 30 постоянно устанавливается логический ноль. На управляющих входах ST1, ST25 всех узлов сдвига группы 29-, кроме второго снизу, постоянно увеличивается логическая единица (фиг.4).

5 сдвига группы 30, кроме крайнего ниж-

него и крайнего верхнего, постоянно установлена логическая единица. На девяти старших разрядах информационного входа второго снизу узла сдвига

50 группы 30 и на шести младших разрядах крайнего нижнего узла сдвига группы 30 постоянно установлена логическая единица. На фиг,4 приведен пример построения блока 2 при разрядности

55 сдвигаемых кодов, равной 64.

Кахдкй узехг сдвига х руппы 30 содержит 16-разрядньш информационньш вход и выход (фиг,4),

3129

БИС К1800ВР8 кроме информационного входа и выхода содержит четыре разряда ((SF3, SF2, SF1, SFO) группы входов задания величины сдвига (фиг.З), причем разряд SF3 является

старшим разрядом, а разряд SFO - младшим разрядом группы входов задания величины сдвига, группу из трех входов задания типа сдвига (STO,

ST1, ST2) и знаковый вход (Z). Возможны следующие типы сдвигов и со- ответствуюпще им коды, устанавливаемые (формируемые) на входах STO, ST1, ST2: на все разряды выхода подано значение знакового входа Z - 000; на всех разрядах выхода устанавливается логическая единица - 100: сдвиг влево на Величину, определяемую до- полнительынм кодом кода, установленного на входах SF3-SFO, с установкой в освобождаемых разрядах логической единицы - 010; сдвиг вправо на величину, определяемую дополнительным кодом кода, установленного на входах SF3-SFO, с установкой в освобождаемых разрядах логической единицы - 110; циклический сдвиг вправо - 001, циклический сдвиг влево - 101; ариф- мHЩчJЁG кйй сдвиг вправо с установкой в оГёвб б ождаемых разрядах значения си.внала зна.ков6го входа Z - 011; ари ф ме-тич.еский сдвиг влево с установкой в освобождаемых разрядах значения знакового входа Z - 111. Указанные типы сдвигов и ©оответствую- щие им коД Ы не идентичТнгы типам сдвигов и соответствующим кодам блока 2 и устройства. В блоке 2 предусмотрен те же типы сдвигов и соответствующие им коды, что и в блоке 1 и в устройстве: логический сдвиг вправо с установкой Б освобождаемых разрядах логического нуля задается кодом 110 в разрядах SO-S2 группы входов 13 уст- ройства; лог,1ще.ский сдвиг влево с установкой в освобождаемых разрядах логического нуля задается кодом 100 р-азрядах SO-S2 группы входов 13 устройства, арифметический сдвиг вправо с установкой в освобождаемых разряда значения знакового входа задается кодом 111 в разрядах SO-S2 группы входов 13 устройства; циклический сдвиг вправо задается кодом 011 в разрядах SO-S2 группы входов 13 устройства. Все узлы сдвига группы 30 в блоке 2 настроены на арифметический сдвиг вправо или влево в зависимости от

4

сигнала на входе STO, устанавливаемого в соответствии с кодом на группе входов 13. При сдвиге вправо на STO устанавливается логический ноль, а при сдвиге влево - логическая единица.

5

0

0

Q

Блок 3 сдвига контрольных разрядов битов (фиг.З) содержит узел 29 Ьдвига, элементы И 26-28, элемент iE 25 предназначен для осуществления логических вправо, влево и циклических вправо сдвигов контрольных кодов, формируемых из контрольных разрядов и устанавливаемых на входах группы 9 устройства. Контрольные разряды представляют собой биты побайтных разрядов (сигналы четности) сдвигаемого- кода на входах группы 8. Порядок расположения контрольных разрядов входов группы 9 при подключении их к информационным входам узла 29 сдвига соответствует порядку расположения соответствующих им байт на входах группы 8. На фиг.З приведен пример 5 построения блока 3 при разрядности сдвигаемых двоичных кодов, равной 64, и при формировании побайтных контрольных битов (сигналов), т.е. при разрядности контрольного кода, равной 8. Особенности подключения разрядов входов группы 9 к разрядам у:зла 29 сдвига и разрядов дыхода уз- . ла 29 сдвига к блоку 7 и группе .1J выходов устройства обусловлены необходимостью обеспечить вьтолнение циклических сдвигов вправо, логических сдвигов влево и вправо на одном узле 29 сдвига, разрядность которого в два раза больше разрядности сдвигаемого кода. Код типа сдвига (такой же, что и код типа сдвига устройства) устанавливается на группе входов 13 устройства. В блоке 3 выполняется соответствующий тип сдвига, кроме случаев задания арифметических сдвигов вправо (с кодом 111). В этом случае в блоке 3 выполняется логический сдвиг вправо, так как на входе Z постоянно установлен логический нол%. Код величины сдвига (такой же, что и для блока 1) устанавливается на входах группы 14 устройства. Сдвиг может осуществляться в пределах 0-7, так как на входе SF3 узла 29 сдвига установлен ноль. Сдвинутый код в блоке 3 передается на информационные выходы группы 11 устройства. На вход узла 7 передается сдвинутый код с нулевыми значениями крайнего левого или край5

0

5

него правого разрядов, связанных с выходами элементов И 27 и 28.

При логическом сдвиге вправо элемент И 28 пропускает сигнал с крайнего левого разряда узла 29 сдвига, а правьш элемент И 27 блокируется и на его выходе устанавливается логический ноль.

При логическом сдвиге влево правый элемент И 27 пропускает сигнал с крайнего правого разряда узла 29 сдвига, а элемент И 28 блокируется и на его выходе устанавливается логический ноль. При циклических сдвигах элементы И 27 и 28 блокируются при любых значениях кода на группе 14 входов. Описанная особенность обусловлена тем, что при байтных сдвигах логических и арифметических влево (вправо) значение контрольного сигнала четности крайнего правого (левого) байта в сдвинутом двоичном коде на информационных выходах группы 10 устройства всегда равно логическому нулю, а четность крайнего левого (правого) байта на информационных выходах группы 11 необходимо корректировать при сдвиге в блоке 2, Четность этого байта учитывается с помощью узла 7, для чего на выходе элемента И 28 также формируется логический ноль, не влияющий на формирование правильного сигнала четности на выходе узла 7-свертки по модулю два. По этой же причине на выходах элементов И 27 и 28 формиру-. ется нулевой сигнал при циклических сдвигах, так как четность не учтенных байтов учитывается благодаря цикго на выходе блока 1. Б блоке 6 сдвиги осуществляются на величину 3-1-ЕИ, где БИ - двоичный код, установленный на входах группы 15, так как на вхо5 де SF3 узла 24 сдвига постоянно установлена логическая единица. В блок 6 могут быть заданы такие же типы сдвигов, что и в блоке 2 и в устройстве путем установки на входах

Ш группы 13 соответствунлцих кодов.

Устройство работает следующим образом.

Исходное состояние устройства мо жет быть произвольным. Сдвигаемый

5 двоичньй код устанавливается на информационные входы группы 8 устройства. При этом на крайнем левом разряде 8 группы: 8 входа устанавливается значение знака операнда, пред20 ставляемого двоичным кодом, при арифметическом сдЕ1Иге. На входах групп 9 устанавливаются значения сигналов побайтных контрольных разрядов чет-- ности, сопровождающих сдвигаемый

25 двоичный код.

30

35

При этом нупевое значение контрольного сигнала соответствует четному количеству логических единиц в коде соответствующего байта, а единичное значение контрольного сигнала соответствует нечетному количеству логических единиц в коде соответствующего байта. Причем контрольный сигнал, соответствун1Ш {й k-му байту кода на входах группы 8 устройства, устанавливается (подается) на k-ый разряд входов контрольных разрядов группы 9, Код типа сдвига устанавлилическим сдвигам в блоке 6. На выхо- 40 « входах группы 13 устройстде узла 4 формируется контрольньй сигнал четности сдвинутого двоичного кода, установленного на выходе блока 2, На выходе узла 7 формируется

ва и передается на соответствующие входы блоков 1, 2, 3 и 6. Код величины сдвига задается на двух группах входов. Код величины байтных сдвигов

предсказанный контрольный сигнал чет- 45 (равный БА) задается на входах груп- ности сдвинутого двоичного кода, ус- пы 14 и передается на соответствую- тановленного на группе 10 информационных выходов блока 2 и устройства. На группе 17 выходов устройства формируются побайтные контрольные сигна- 50 ль1 четности для сдвинутого кода.

щие входы блоков 1 и 3. Код величины битных сдвигов (равный БИ) (в пределах 0-7) задается на входах группы 15 и передается на соответствующие входы блоков 2 и 6. Сигнал знака с крайнего левого разряда 8 входов группы 8 передается на знаковые входы блоков 1, 2 и 6. В устройстве обеспечивается выполнение следующих типов сдвига: логический сдвиг влево (при коде 100 на входах группы 13), логический сдвиг вправо (при коде 110), арифметический сдвиг вправо (при косформированного на выходе блока 2.

Блок 6 :;двига последнего байта (фиг.2) предназначен для сдвига кода крайн эго левого (формируемого на входах группы 18) или крайнего правого (формируемого на входах группы 19) байта сдвинутого кода, установленного на выходе блока 1. Б блоке 6 сдвиги осуществляются на величину 3-1-ЕИ, где БИ - двоичный код, установленный на входах группы 15, так как на входе SF3 узла 24 сдвига постоянно установлена логическая единица. В блок 6 могут быть заданы такие же типы сдвигов, что и в блоке 2 и в устройстве путем установки на входах

группы 13 соответствунлцих кодов.

Устройство работает следующим образом.

Исходное состояние устройства мо жет быть произвольным. Сдвигаемый

двоичньй код устанавливается на информационные входы группы 8 устройства. При этом на крайнем левом разряде 8 группы: 8 входа устанавливается значение знака операнда, представляемого двоичным кодом, при арифметическом сдЕ1Иге. На входах групп 9 устанавливаются значения сигналов побайтных контрольных разрядов чет-- ности, сопровождающих сдвигаемый

двоичный код.

При этом нупевое значение контрольного сигнала соответствует четному количеству логических единиц в коде соответствующего байта, а единичное значение контрольного сигнала соответствует нечетному количеству логических единиц в коде соответствующего байта. Причем контрольный сигнал, соответствун1Ш {й k-му байту кода на входах группы 8 устройства, устанавливается (подается) на k-ый разряд входов контрольных разрядов группы 9, Код типа сдвига устанавли45 (равный БА) задается на входах груп- пы 14 и передается на соответствую- 50

55

щие входы блоков 1 и 3. Код величины битных сдвигов (равный БИ) (в пределах 0-7) задается на входах группы 15 и передается на соответствующие входы блоков 2 и 6. Сигнал знака с крайнего левого разряда 8 входов группы 8 передается на знаковые вход блоков 1, 2 и 6. В устройстве обеспечивается выполнение следующих типо сдвига: логический сдвиг влево (при коде 100 на входах группы 13), логический сдвиг вправо (при коде 110), арифметический сдвиг вправо (при ко71297055

де 111), циклический сдвьг вправо (при коде 011). Специально арифметический сдвиг влево в устройстве не предусмотрен, так как логически сдвинутый влево операнд равен арифмети- 5 чески сдвинутому влево операнду при отсутствии переполнения, фиксирование (контроль) которого можно осуществлять внешними средствами. При наличии переполнения для получения Ю арифметически сдвинутого влево one- ранда достаточно получить логически сдвинутый влево операнд (двоичный код), а затем осуществить (внешними средствами) передачу сигнала знака 5 в крайний левый разряд логически сдвинутого кода.

В соответствии с заданным типом сдвига осуществляются сдвиги кода в блоке 1. на величину 8-БА, а затем 20 сдвиг сдвинутого таким образом кода в блоке 2 на величину БИ. В итоге на выходах группы 10 устройства формируется код сдвинутьй, на величину

которых равна четности сдвинутого двоичного кода, сформированного на выходах блока 2 и переданного на информационные выходы группы 10 устройства. На выходе узла 7 формируется п редсказанный сигнал четности сдвинутого двоичного кода, сформированного на выходах группы 10 устройства. Параллельно с помощью узлов свертки по модулю два группы 20 осуществляется суммирование кода по модулю два. На выходе узла 4 формируется сигнал четности сдвинутого кода, которьш сравнивается узлом 5 сравнения с предсказанным сигналом четности. Если сигналы на входах узла 5 сравнения не равны, то на выходе 16 неисправности устройства устанавливается логическая единица, означающая, что при передаче кода на входе или при сдвиге его в блоках 1 и 2 произошла ошибка. На выходах группы 17 устройства формируются побайтные контрольные сигналы четности для

(8БА+БИ). В приведенном примере вели-25 сдвинутого кода на выходах группы 10

чина БА и БИ может находиться в пределах 0-7 и, следовательно, возможный предел задания величины сдвига равен 0-63 разрядов.

устройства для сопровождения его при последующей передаче.

В блоке 3 осуществляются сдвиги контрольных битов в соответствии с типом сдвига, осуществляемом в блоке 1, кроме случаев задания арифметиТаким образом, в предлагаемом уст- 30 ройстве обеспечивается вьтолнение требуемых типов сдвига двоичных кодов на произвольное количество разрядов (в пределах разрядной сетки) за один такт. При этом обеспечивает- ческих сдвигов вправо, при задании ко- ся контроль правильности функциони- торых в блоке 3 осуществляется логичес- рования устройства в каждом такте и кий сдвиг вправо. Величина сдвига в бло- при любом типе сдвига, ке 3 равна БА (). Сигналы, формируемые на выходах группы 11 устройства, представляют собой побайтные сигналы четности сдвинутого двоичного кода, установленного на выходах группы 12 устройства, так как сдвиг контрольного кода в блоке 3 осуществляется синхронно со сдвигом кодов байтов в блоке 1, Целесообразность наличия выходов групп 11 и 12 устройства обусловлена частым использованием байтных сдвигов в процессоре. На входы блока 6 передается код крайнего соответственно левого и правого байта кода, сфор- мированного на выходе блока 1. В блоке 6 осуществляются сдвиги в соответствии ;с типом сдвига, заданном на входах группы 13 устройства на

40 Формула изобретения

Устройство для сдвига информации с контролем, содержащее блок побайтных сдвигов, блок побитных сдвигов,

45 блок сдвига контрольных разрядов, два узла свертки по модулю два, группу узлов свертки по модулю два и узел сравнения, причем группа информационных входов блока побайтных

50 сдвигов является группой информаци- онных входов устройства, группа информационных входов блока сдвигов контрольных разрядов является группой контрольных разрядов устройства,

55 группа информационных выходов блока побайтных сдвигов соединена с группой информационных входов блока побитных сдвигов, группа информационных выходов которого соединена с информавеличину, равную (8хБИ), При этом на выходах блоков 6 и 3 формируются двоичные коды, суммарная четность

которых равна четности сдвинутого двоичного кода, сформированного на выходах блока 2 и переданного на информационные выходы группы 10 устройства. На выходе узла 7 формируется п редсказанный сигнал четности сдвинутого двоичного кода, сформированного на выходах группы 10 устройства. Параллельно с помощью узлов свертки по модулю два группы 20 осуществляется суммирование кода по модулю два. На выходе узла 4 формируется сигнал четности сдвинутого кода, которьш сравнивается узлом 5 сравнения с предсказанным сигналом четности. Если сигналы на входах узла 5 сравнения не равны, то на выходе 16 неисправности устройства устанавливается логическая единица, означающая, что при передаче кода на входе или при сдвиге его в блоках 1 и 2 произошла ошибка. На выходах группы 17 устройства формируются побайтные контрольные сигналы четности для

устройства для сопровождения его при последующей передаче.

Таким образом, в предлагаемом уст 30 ройстве обеспечивается вьтолнение требуемых типов сдвига двоичных кодов на произвольное количество разрядов (в пределах разрядной сетки) за один такт. При этом обеспечивает- ся контроль правильности функциони- рования устройства в каждом такте и при любом типе сдвига,

40 Формула изобретения

Устройство для сдвига информации с контролем, содержащее блок побайтных сдвигов, блок побитных сдвигов,

45 блок сдвига контрольных разрядов, два узла свертки по модулю два, группу узлов свертки по модулю два и узел сравнения, причем группа информационных входов блока побайтных

50 сдвигов является группой информаци- онных входов устройства, группа информационных входов блока сдвигов контрольных разрядов является группо контрольных разрядов устройства,

55 группа информационных выходов блока побайтных сдвигов соединена с группо информационных входов блока побитных сдвигов, группа информационных выходов которого соединена с информационными входами соответствующих УЗЛОВ свертки по модулю два группы и является первой группой информационных выходов устройства, группы входов задания типа сдвига блока побайтных сдвигов, блока побитных сдвигов и блока сдвига контрольных разрядов объединены и подключены к группе входов задания типа сдвигов устройства,

группы входов задания типа сдвига узла сдвига соединен с шиной единичного потенцшша устройства, в блоке сдвига последнего байта группа информационных входов узла сдвига соединена с группами информационных выходов старшего и младшего байтов бло ка побайтных сдвигов, выход элемента НЕ соединен с первым входом первого

группы входов задания величины сдвигало элемента И, выход которого соединен

блока побайтных сдвигов и блока с.дви га контрольных разрядов объединены и подключены к группе входов задания величины побайтных сдвигов устройства, группа входов задания величины сдвига блока побитных сдвигов является группой входов задания величины побитных сдвигов устройства, отличающееся тем, что, с цеИ подключены к соответствующим разрядам группы входов задания типа сдвига устройства, младпше разряды группы входов задания величины сдви узла сдвига блока сдвига последнего

лью сокращения оборудования, устрой- 20 байта подключены к соответствугадим

30

ство содержит блок сдвига последнего байта, содержащий узел сдвига, два элемента И и элемент НЕ, а блок сдвига контрольных разрядов содержит узел сдвига, три элемента И и элемент НЕ, причем в блоке сдвига контрольных разрядов группа информационных входов ,узла сдвига является группой информационных входов блока сдвига контрольных разрядов, три младших разряда группы входов задания величины сдвига узла сдвига образуют группу входов задания величины сдвига блока сдвига контрольны/; разрядов, выход первого элемента И соединен с первым разрядом группы входов задания типа сдвига узла сдвига, вход второго разряда группы входов типа сдвига узла сдвига объединен с первыми вхо- дами первого, второго и третьего элементов И и является первьш разрядом группы входов задания типа сдвига блока, сдвига контрольных разрядов, вход элемента НЕ объединен с вторым входом.третьего элемента И и является вторым разрядом группы входов задания типа сдвига блока сдвига контрольных разрядов, выход элемента НЕ соединен с вторыми входами второго и третьего элементов И, информационные входы младшего и старшего разрядов узла сдвига соединены с третьими входами соответственно второго и третьего элементов И,зна- ковь1й вход и старший разряд группы входов задания величины сдвига узла сдвига соединены с шиной нулевого потен циала устройства, третий разряд

разрядам группы входов задания величины побитных сдвих ов устройства, в блоке сдвига последнего байта вхо элемента НЕ объединен с вторым вход второго элемента И, выход которого соединен со знаковым входом узла сдвига, второй разряд группы входов задания типа сдвига узла сдвига объ динен с вторым входом первого элеме та И, старший разряд группы входов задания величины сдвига и третий ра ряд группы входов задания типа сдви узла сдвига соединены с шиной единичного потенциала устройства, груп информационных выходов узла сдвига блока сдвига последнего байта соединена с группой входов первого узл свертки по модулю два, выход которо го соединен с первым информационным входом узла сравнения, выход несрав нения которого является выходом неисправности устройства, группа информационных выходов блока побитных сдвигов соединена с группой входов второго узла свертки по модул о два, выход-которого соединен с вторым ин формационным входом узла сравнения, выходы узлов свертки по модулю два

СП группы образуют пе:рвую группу выход контрольных разрядов устройства, зн ковые входы блоков побайтных и побитных сдвигов и третий вход второг элемента И блока сдвига последнего

ег байта объединены и подключены к ста шему разряду группы информационных входов устройства, группа информационных выходов блока побайтных сдви гов и группа информационных выходов

35

40

45

группы входов задания типа сдвига узла сдвига соединен с шиной единичного потенцшша устройства, в блоке сдвига последнего байта группа информационных входов узла сдвига соединена с группами информационных вы. ходов старшего и младшего байтов блока побайтных сдвигов, выход элемента НЕ соединен с первым входом первого

с первым разрядом группы входов задания типа сдвига узла сдвига, второй вход первого элемента И, вход элемента HEja первый вход второго элемента

И подключены к соответствующим разрядам группы входов задания типа сдвига устройства, младпше разряды группы входов задания величины сдвига узла сдвига блока сдвига последнего

байта подключены к соответствугадим

0

разрядам группы входов задания величины побитных сдвих ов устройства, в блоке сдвига последнего байта вход элемента НЕ объединен с вторым входом второго элемента И, выход которого соединен со знаковым входом узла сдвига, второй разряд группы входов задания типа сдвига узла сдвига объединен с вторым входом первого элемента И, старший разряд группы входов задания величины сдвига и третий разряд группы входов задания типа сдвига узла сдвига соединены с шиной единичного потенциала устройства, группа информационных выходов узла сдвига блока сдвига последнего байта соединена с группой входов первого узла свертки по модулю два, выход которого соединен с первым информационным входом узла сравнения, выход несравнения которого является выходом неисправности устройства, группа информационных выходов блока побитных сдвигов соединена с группой входов второго узла свертки по модул о два, выход-которого соединен с вторым информационным входом узла сравнения, выходы узлов свертки по модулю два

П группы образуют пе:рвую группу выходов контрольных разрядов устройства, знаковые входы блоков побайтных и побитных сдвигов и третий вход второго элемента И блока сдвига последнего

г байта объединены и подключены к старшему разряду группы информационных входов устройства, группа информационных выходов блока побайтных сдвигов и группа информационных выходов

5

0

5

П1297055узла.сдвига блока сдвига контрольных разрядов являются второй груплой информационных выкодов устройства и второй группой выходов контрольных разрядов устройства соответственноj выходы второго и третьего элементов

И б и г сдв ряд 5 ряд пер

13

8,

S657

12

И блока сдвига контрольных разрядов и группа информационных выходов узла сдвига блока сдвига контрольных разрядов, кроме младшего и старшего раз- 5 рядов, соединены с группой входов первого узла свертки по модулю два.

13 18

58 5S SOB г

62 S3

SI

23

22

SI

S2

21

rsitiumnos 8 16 5 l 3 2 1 О

SfJ

Sf2 SfO

rj

-J

24

S70 STf ST2

фиг. г

KSa.l f

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования сигнала четности при сдвигах двоичных кодов | 1987 |

|

SU1481770A1 |

| Устройство для контроля сдвигателя | 1989 |

|

SU1672456A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ПРЕДСКАЗАННЫХ СИГНАЛОВ ЧЕТНОСТИ ПРИ СДВИГАХ ДВОИЧНЫХ КОДОВ | 1992 |

|

RU2045772C1 |

| Устройство для формирования сигналов четности при сдвигах двоичных кодов | 1989 |

|

SU1783527A1 |

| Устройство для формирования сигналов четности | 1988 |

|

SU1571591A1 |

| Устройство для сдвига информации с контролем | 1985 |

|

SU1325481A1 |

| Модуль для сдвига операндов | 1988 |

|

SU1617434A1 |

| Устройство односторонних сдвигов двоичных кодов с контролем | 1987 |

|

SU1695306A1 |

| Устройство для предсказания четности результата сдвигателя | 1988 |

|

SU1649545A1 |

| Устройство для сдвига операндов | 1987 |

|

SU1481741A1 |

Изобретение относится к вычислительной технике и может быть использовано в высокопроизводительных системах обработки информации. Цель изобретения - сокращение аппаратурных затрат. Устройство содержит блок 1 побайтных сдвигов, блок 2 побитных сдвигов, блок 3 сдвигов контрольных разрядов, блок 6 сдвига последнего байта, два узла 4 и 7 свертки по модулю два, узел 5 сравнения, группу 20 узлов свертки по модулю два. На информационные входы блока побайтных сдвигов поступает сдвигаемый код и сдвигается там на величину, кратною восьми. Сдвинутый код с выхода блрка побайтньк сдвигов поступает на инфор- мационные входы блока побитных сдвигов, с выхода которого сдвинутьй окончательно код попадает на первую группу информационных выходов устройства. С помощью группы узлов свертки по модулю два формируются контрольные разряды- (побайтно) для сдвинутого кода. Блок сдвига контрольных размеров, блок сдвига последнего байта и второй узел свертки по модулю два формируют предсказанный сигнал четности сдвинутого кода, кото- рьш сравнивается узлом сравнения с сигналом действительной четности сдвинутого кода, который формируется первым узлом свертки по модулю два. Результат сравнения поступает на выход неисправности устройства, 4 ил. I V)

| Электроды рабочего резонатора параэлектрического радиоспектроскопа | 1971 |

|

SU437017A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сдвига информации с контролем | 1983 |

|

SU1095184A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-03-15—Публикация

1985-10-14—Подача