фигЛ

1501050

Изобретение относится к вычислительной технике и предназначено для использования в цифровых вычислительных машинах различного назначения.

Цель изобретения - повышение достоверности вычислений.

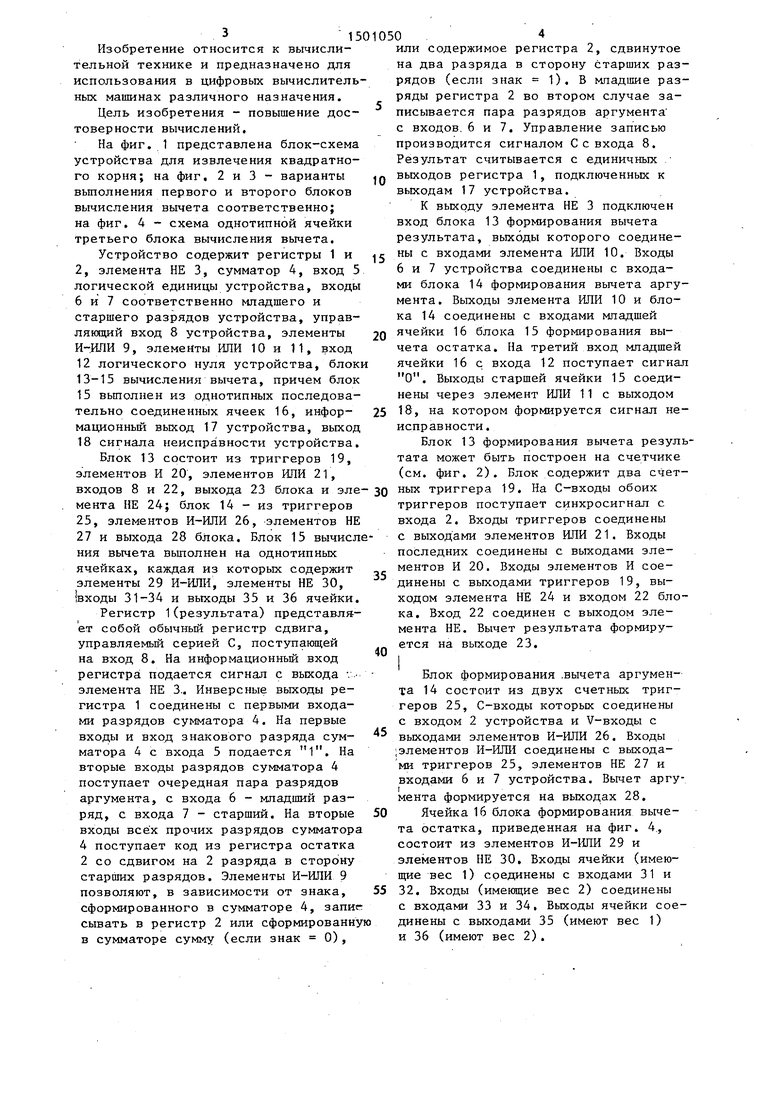

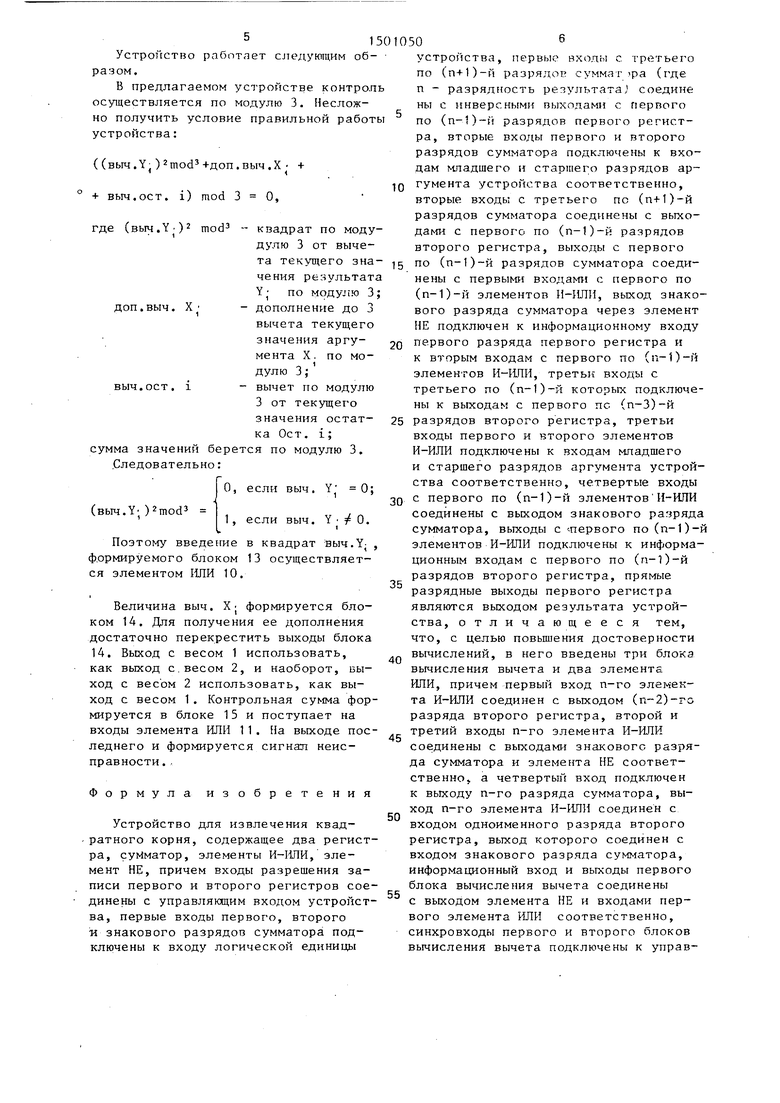

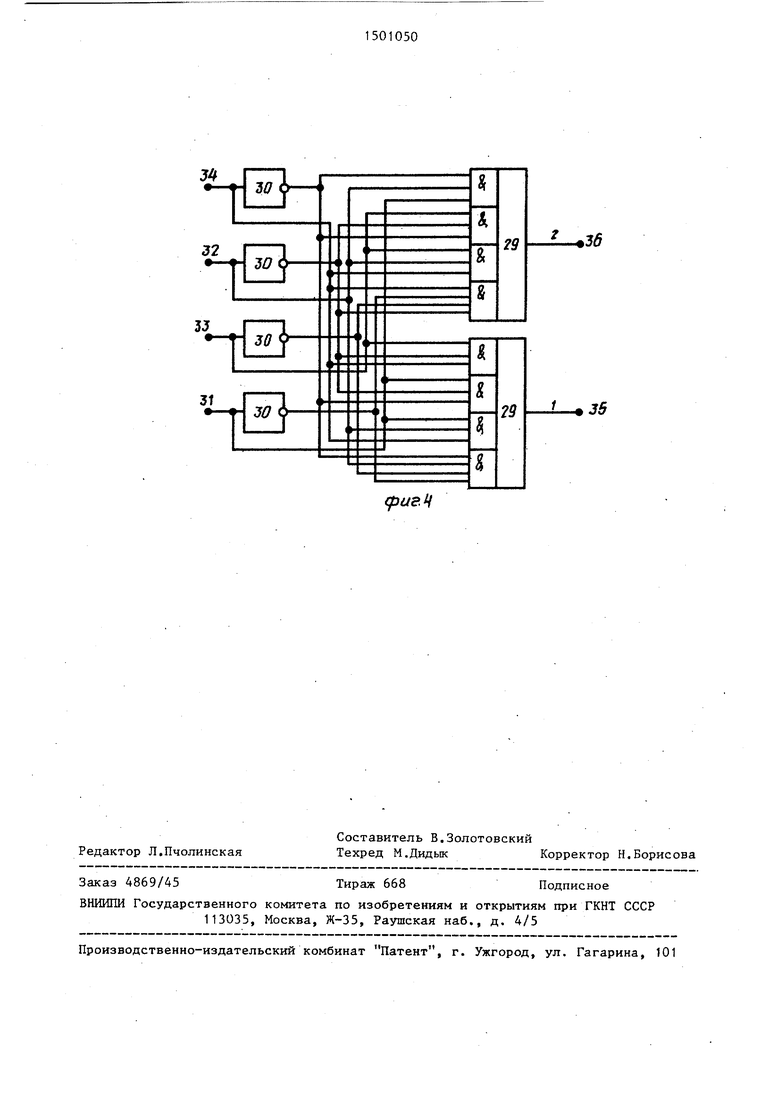

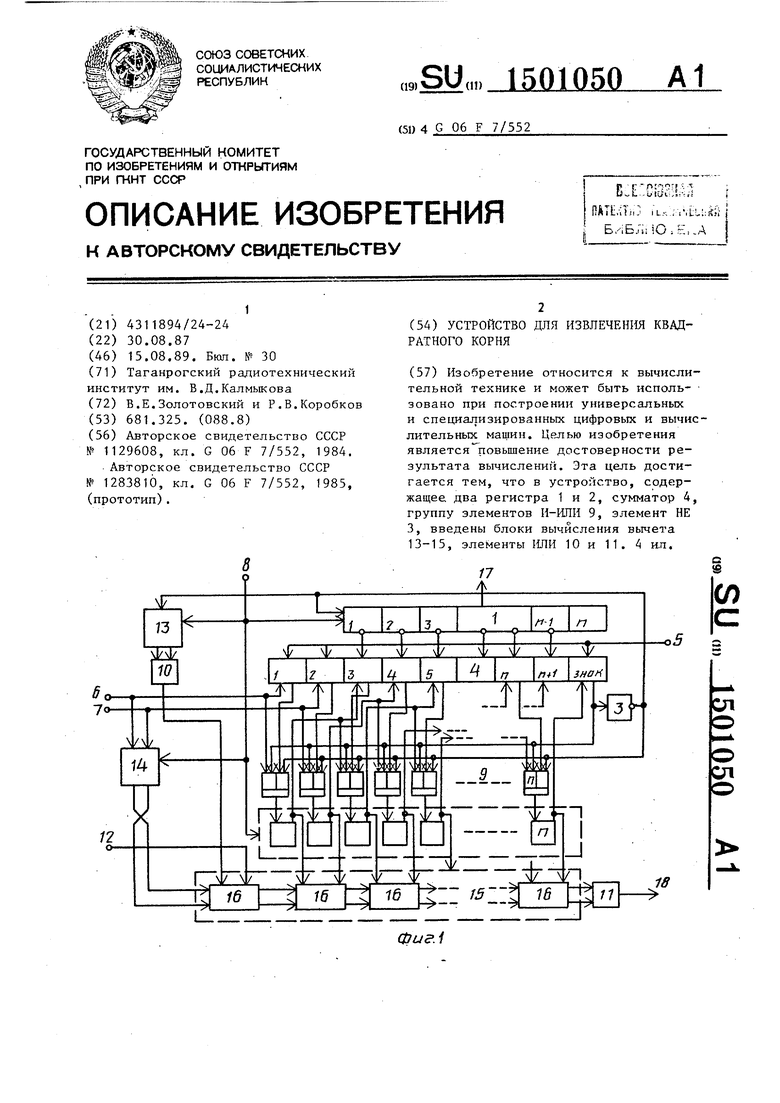

На фиг. 1 представлена блок-схема устройства для извлечения квадратного корня; на фиг, 2 и 3 - варианты вьтолнения первого и второго блоков вычисления вычета соответственно; на фиг. 4 - схема однотипной ячейки третьего блока вычисления вычета.

Устройство содержит регистры 1 и 2, элемента НЕ 3, сумматор 4, вход 5 логической единицы устройства, входы 6 и 7 соответственно младшего и старшего разрядов устройства, управ- ляюощй вход 8 устройства, элементы И-ИЛИ 9, элементы ИЛИ 10 и 11, вход 12 логического нуля устройства, блок 13-15 вычисления вычета, причем блок 15 выполнен из однотипных последовательно соединенных ячеек 16, информационный выход 17 устройства, выход 18 сигнала неисправности устройства.

Блок 13 состоит из триггеров 19, элементов И 20, элементов ИЛИ 21,

0

5

0

5

или содержимое регистра 2, сдвинутое на два разряда в сторону старших разрядов (если знак 1). В мпадшие разряды регистра 2 во втором случае записывается пара разрядов аргумента с входов, 6 и 7. Управление записью производится сигналом С с входа 8. Результат считывается с единичных выходов регистра 1, подключенных к выходам 17 устройства.

К выходу элемента НЕ 3 подключен вход блока 13 формирования вычета результата, выходы которого соединены с входами элемента ИЛИ 10. Входы 6 и 7 устройства соединены с входами блока 14 формирования вычета аргумента. Выходы элемента ИЛИ 10 и блока 14 соединены с входами мпадшей ячейки 16 блока 15 формирования вычета остатка. На третий вход младшей ячейки 16 с входа 12 поступает сигнал О. Выходы старшей ячейки 15 соединены через элемент ИЛИ 11 с выходом 18, на котором формируется сигнал неисправности.

Блок 13 формирования вычета результата может быть построен на счетчике (см. фиг. 2). Блок содержит два счет

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для извлечения корня из суммы квадратов трех чисел | 1988 |

|

SU1624444A2 |

| Устройство для логарифмирования двоичных чисел | 2015 |

|

RU2614932C1 |

| Цифровой знаковый коррелометр | 1980 |

|

SU962975A1 |

| Цифровой преобразователь координат | 1983 |

|

SU1141404A1 |

| Устройство для вычисления обратного гиперболического тангенса | 1973 |

|

SU465630A1 |

| Устройство для вычисления квадратного корня числа в модулярной системе счисления | 1985 |

|

SU1317434A1 |

| Устройство для сложения и вычитания с самоконтролем | 1988 |

|

SU1642469A1 |

| Устройство для вычисления квадратного корня | 1987 |

|

SU1481753A1 |

| Арифметическое устройство | 1975 |

|

SU633016A1 |

| Цифровой фильтр | 1987 |

|

SU1418756A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении универсальных и специализированных цифровых и вычислительных машин. Целью изобретения является повышение достоверности результата вычислений. Эта цель достигается тем, что в устройство, содержащее два регистра 1, 2, сумматор 4, группу элементов И-ИЛИ 9, элемент НЕ 3, введены блоки вычисления вычета 13-15, элементы ИЛИ 10, 11. 3 ил.

35

входов 8 и 22, выхода 23 блока и эле-ЗО триггера 19. На С-входы обоих мента НЕ 24; блок 14 - из триггеров 25, элементов И-ИЛИ 26, элементов НЕ 27 и выхода 28 блока. Блок 15 вычисления вычета вьшолнен на однотипных ячейках, каждая из которых содержит элементы 29 И-Ш1И, элементы НЕ 30, 1входы 31-34 и выходы 35 и 36 ячейки. Регистр 1(результата) представляет собой обычный регистр сдвига, управляемый серией С, поступающей на вход 8. На информационньш вход регистра подается сигнал с выхода . элемента НЕ 3.. Инверсные выходы регистра 1 соединены с первыми входами разрядов сумматора 4. На первые входы и вход знакового разряда сумматора 4 с входа 5 подается 1. На вторые входы разрядов сумматора 4 поступает очередная пара разрядов аргумента, с входа 6 - младший раз40

45

триггеров поступает синхросигнал с входа 2. Входы триггеров соединены с выходами элементов ИЛИ 21. Входы последних соединены с выходами эле ментов И 20. Входы элементов И сое динены с выходами триггеров 19, вы ходом элемента НЕ 24 и входом 22 б ка. Вход 22 соединен с выходом эле мента НЕ. Вычет результата формиру ется на выходе 23.

Блок формирования .вычета аргуме та 14 состоит из двух счетных три геров 25, С-входы которых соединен с входом 2 устройства и V-входы с выходами элементов И-ИЛИ 26. Входы элементов И-ИЛИ соединены с выхода ми триггеров 25, элементов НЕ 27 и входами 6 и 7 устройства. Вычет ар мента формируется на выходах 28.

ряд, с входа 7 - старший. На вторые 50 входы всех прочих разрядов сумматора 4 поступает код из регистра остатка 2 со сдвигом на 2 разряда в сторону старших разрядов. Элементы И-ИЛИ 9 позволяют, в зависимости от знака, 55 сформированного в сумматоре 4, запиг сывать в регистр 2 или сформированную в сумматоре сумму (если знак 0),

триггера 19. На С-входы обоих

триггеров поступает синхросигнал с входа 2. Входы триггеров соединены с выходами элементов ИЛИ 21. Входы последних соединены с выходами элементов И 20. Входы элементов И соединены с выходами триггеров 19, выходом элемента НЕ 24 и входом 22 блока. Вход 22 соединен с выходом элемента НЕ. Вычет результата формируется на выходе 23.

Блок формирования .вычета аргумента 14 состоит из двух счетных триггеров 25, С-входы которых соединены с входом 2 устройства и V-входы с выходами элементов И-ИЛИ 26. Входы элементов И-ИЛИ соединены с выхода- ми триггеров 25, элементов НЕ 27 и входами 6 и 7 устройства. Вычет аргумента формируется на выходах 28.

Ячейка 16 блока формирования вычета остатка, приведенная на фиг. 4., состоит из элементов И-ИПИ 29 и элементов НЕ 30. Входы ячейки (имеющие вес 1) соединены с входами 31 и 32. Входы (имеющие вес 2) соединены с входами 33 и 34, Выходы ячейки соединены с выходами 35 (имеют вес 1) и 36 (имеют вес 2).

Устройство работает следующим об- разом,

В предлагаемом устройстве контроль осу1цествляется по модулю 3. Несложно получить условие правильной работы устройства:

((выч.У,)2тоа5+доп.выч.Х + + выч.ост. i) mod ,

где (выч.У.)2 mod -- квадрат по моду- дулю 3 от вычета тек тчего значения результата YJ по модулю 3;

доп.выч. - дополнение до 3

вычета текущего значения аргумента X, по модулю 3;

выч.ост. i - вычет по модулю

3 от текущего значения остатка Ост. i;

сумма значений берется по модулю 3. .Следовательно:

если выч,

если выч.

Y;

0;

Y. 0.

Поэтому введение в квадрат выч.У- формируемого блоком 13 осуществляется элементом liTM 10.

Величина выч. Х; формируется блоком 14. Для получения ее дополнения достаточно перекрестить выходы блока 14. Выход с весом 1 использовать, как выход с.весом 2, и наоборот, выход с весом 2 использовать, как выход с весом 1. Контрольная сумма формируется в блоке 15 и поступает на входы элемента ИЛИ 11. fia выходе последнего и формируется сигнал неисправности .

Формула изобретения

Устройство для извлечения квадратного корня, содержащее два регистра, сумматор, элементы И-ИЛИ, элемент НЕ, причем входы разрешения записи первого и второго регистров соединены с управляюпщм входом устройства, первые входы первого, второго я знакового разрядов сумматора подключены к входу логической единицы

10

15

0

25

0

5

0

5

0

5

устройства, первые входы с третьего по (п+О-й разрядоЕ суммах ра (где п - разрядность ре: ультата, соедине ны с инверсными выходами с первого по (п-1)-й разрядов первого регистра, вторые входы первого и второго разрядов сумматора подключены к входам младшего и старшего разрядов аргумента устройства соответственно, вторые входы с третьего по (п+1)-й разрядов сумматора соединены с выхо- с первого по (п-1)-й разрядов второго регистра, выходы с первого по (п-1)-й разрядов сумматора соединены с первыми входам 1 с первого по (п-1)-й элементов И-ИЛИ, выход знакового разряда сумматора через элемент НЕ подключен к информационному входу первого разряда первого регистра и к вторым входам с первого по (п-1)-й элементов И-ИЛИ, третьи входы с третьего по (п-1)-й которых подключены к выходам с первого по (п-З)-й разрядов второго регистра, третьи входы первого и второго элементов И-ИЛИ подключены к входам младшего и старшего разрядов аргумента устройства соответственно, четвертые входы с первого по (п-1)-й элементов И-ИЛИ соединены с вькодом знакового разряда сумматора, выходы с tnepBoro по (п-1)-й элементов И-ИЛИ подключены к информационным входам с первого по (п-1)-й разрядов второго регистра, прямые разрядные выходы первого регистра являются выходом результата устройства, отличающееся тем, что, с целью повышения достоверности вычислений, в него введены три блока вычисления вычета и два элемента ИЛИ, причем первый вход п-го элемента И-ИЛИ соединен с выходом (п-2)-го разряда второго регистра, второй и третий входы п-го элемента И-ИЛИ соединены с выходами знакового разряда сумматора и элемента НЕ соответственно а четвертый вход подключен к выходу п-го разряда сумматора, выход п-го элемента И-ИПИ соединен с входом одноименного разряда второго регистра, выход которого соединен с входом знакового разряда сумматора, информационный вход и выходы первого блока вычисления вычета соединены с выходом элемента НЕ и входами первого элемента ИЛИ соответственно, синхровходы первого и второго блоков вычисления вычета подключены к управляющему входу устройства, первый и второй информационные входы второго блока вычисления вычета соединены с входами младшего и старшего разрядов аргумента устройства соответственно, а первый и второй выходы - соответственно с вторым и первым входами третьего блока вычисления вычета, третий и четвертый входы которого

подключены соответственно к выходу первого элемента 11ПИ и входу логического нуля устройства, остальные входы - к единичным разрядным выходам второго регистра, а выходы-- к первому и второму входам второго элемента ПНИ, выход которого является выходом сигнала Неисправность

(риз,г

сригЗ

(рие.Ц

| Устройство для извлечения квадратного корня | 1982 |

|

SU1129608A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для извлечения квадратного корня | 1985 |

|

SU1283810A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-08-15—Публикация

1987-08-30—Подача